João Carlos da Silva Carreira Implementação em hardware de um analisador de espectros baseado em SDR

João Carlos da Silva

Carreira

Implementação em hardware de um analisador de espectros baseado em SDR

Hardware implementation of a spectrum analyzer based in SDR

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia de Electrónica e Telecomunicações, realizada sob a orientação científica do Professor Doutor Nuno Miguel Gonçalves Borges de Carvalho e do Professor Doutor José Manuel Neto Vieira, Professores do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro

### o júri / the jury

presidente / president Professor Doutor José Carlos Esteves Duarte Pedro

Professor Catedátrico da Universidade de Aveiro

vogais / examiners committee Professor Doutor Artur Manuel Oliveira Andrade de Moura

Professor Auxiliar da Faculdade de Engenharia da Universidade do Porto (Arguente)

Professor Doutor Nuno Miguel Gonçalves Borges de Carvalho

Professor Associado com Agregação da Universidade de Aveiro (Orientador)

Professor Doutor José Manuel Neto Vieira

Professor Auxiliar da Universidade de Aveiro (Co-orientador)

# agradecimentos / acknowledgements

Existe um conjunto de pessoas que, directa ou indirectamente, contribuíram para a realização desta dissertação. Sem elas este trabalho não teria sido possível.

Em primeiro lugar, agradeço aos meus orientadores pela ajuda, orientação e transmissão de conhecimentos ao longo deste último ano.

À Universidade de Aveiro, em especial ao Departamento de Electrónica, Telecomunicações e Informática e ao Instituto de Telecomunicações por me terem fornecido os meios necessários à realização deste trabalho.

Ao Sr. Paulo Gonçalves do Instituto de Telecomunicações pela enorme paciência e ajuda na elaboração das PCBs.

A todos os meus amigos que me acompanharam ao longos destes últimos 5 anos, em especial ao Teófilo Monteiro por ter embarcado comigo nesta aventura e ao Luís Nunes pela preciosa ajuda com o software ADS.

Ao meu primo, padrinho e colega de casa Nuno Lourenço por estar sempre disponível para me ajudar.

Aos meus avós, primos e tios por serem uma verdadeira família.

À minha namorada Joana, por me fazer sonhar.

Ao meu irmão Ricardo, por ser para mim um exemplo a seguir.

Aos meus pais, por confiarem em mim e estarem sempre disponíveis para tudo. Sem eles eu não estaria aqui.

A todos, Muito Obrigado!

#### Palavras-chave

Analisador de espectros, software defined radio, SDR, arquitecturas de recepção RF

#### Resumo

A metrologia de rádio-frequência surgiu com as primeiras experiências de sistemas de rádio, pois era importante avaliar as condições em que eram feitas essas experiências assim como avaliar o desempenho dos próprios sistemas. Um dos instrumentos fundamentais na metrologia de rádio-frequência é o analisador de espectros, que tem como principal função apresentar porções do espectro de rádio-frequência, normalmente potência em função da frequência, para posterior análise efectuada pelo utilizador.

Nos últimos tempos temos vindo a assistir a uma revolução ao nível dos sistemas de telecomunicações com o desenvolvimento do conceito de *Software Defined Radio (SDR)*. Com a implementação deste novo conceito pretendese criar sistemas de rádio reconfiguráveis por software, permitindo-lhes assim uma maior flexibilidade e adaptação às diversas normas de comunicação via rádio-frequência.

Com este documento pretende-se mostrar uma implementação de um analisador de espectros de baixo custo baseado num sistema SDR. Para tal, foi efectuada uma procura por componentes disponíveis no mercado e com base nesta procura decidiu-se implementar este sistema para uma gama de frequências de entrada entre 2.1 GHz e 2.6 GHz e uma frequência intermédia de 100 MHz. Sendo este um sistema de rádio com alguma complexidade, o projecto foi divido em duas partes: software e hardware. Esta dissertação é focada na implementação do hardware.

### **Keywords**

Spectrum analyzer, software defined radio, SDR, RF receiver architectures

#### **Abstract**

The radio-frequency metrology appeared with the first experiments in radio systems because it was important to assess the conditions under which these experiments were performed as well as to evaluate the performance of the systems themselves. One of the key tools in radio-frequency metrology is the spectrum analyzer, whose main function is to display pieces of the radio spectrum (normally, power as a function of frequency) for further analysis by the user.

In the last years we have been witnessing a revolution in telecommunication systems with the introduction of a new concept: the *Software Defined Radio (SDR)*. With the implementation of this new concept, one intends to create radio systems that are reconfigurable by means of software, giving them a greater flexibility and adaptation to different radio standards.

This document aims to show a possible implementation of a low-cost spectrum analyzer based on an SDR system. To achieve this end, it was performed a search for components that are available in the market and it was decided to implement this system for an input frequency range of 2.1 GHz to 2.6 GHz and an intermediate frequency of 100 MHz. Since this is a radio system with some degree of complexity, the project was divided into two parts: software and hardware. This dissertation is focused on the hardware implementation.

# Contents

| C            | onter | nts                                     |    |

|--------------|-------|-----------------------------------------|----|

| Li           | st of | Figures                                 | v  |

| Li           | st of | Tables                                  | vi |

| $\mathbf{A}$ | crony | yms                                     | ix |

| 1            | Intr  | roduction                               | 1  |

|              | 1.1   | Overview                                | 1  |

|              | 1.2   | Objectives                              | 2  |

|              | 1.3   | Thesis Outline                          | 2  |

| <b>2</b>     | The   | e Spectrum Analyzer                     | 5  |

|              | 2.1   | Introduction                            | Ę  |

|              | 2.2   | Types of Measurements                   |    |

|              | 2.3   | Types of Spectrum Analyzers             | 6  |

|              |       | 2.3.1 FFT Spectrum Analyzer             | 7  |

|              |       | 2.3.2 Superheterodyne Spectrum Analyzer | 7  |

|              |       | 2.3.3 Vector Signal Analyzer            | 8  |

|              | 2.4   | Theory of Operation                     | Ć  |

|              | 2.5   | Specifications                          | 10 |

|              |       | 2.5.1 Frequency Range                   | 10 |

|              |       | 2.5.2 Accuracy                          | 11 |

|              |       | 2.5.3 Frequency Resolution              | 12 |

|              |       | 2.5.4 Sensitivity                       | 12 |

|              |       | 2.5.5 Distortion                        | 12 |

|              |       | 2.5.6 Dynamic Range                     | 13 |

| 3            | Soft  | tware Defined Radio                     | 15 |

|              | 3.1   | Introduction                            | 15 |

|              | 3.2   | Front-End Receiver Architectures        | 16 |

|              |       | 3.2.1 Baseband Digitalization           | 16 |

|              |       | 3.2.2 IF Digitalization                 | 17 |

|              |      | 3.2.3 RF Digitalization                                    | 17 |

|--------------|------|------------------------------------------------------------|----|

|              | 3.3  | SDR Concerns                                               | 18 |

|              | 3.4  | Cognitive Radio                                            | 19 |

| 4            | Rec  | eiver Architecture                                         | 21 |

|              | 4.1  | Introduction                                               | 21 |

|              | 4.2  | Direct Conversion Architecture                             | 21 |

|              | 4.3  | Multiple Conversion Architecture                           | 23 |

|              | 4.4  | Low IF Architecture                                        | 24 |

|              | 4.5  | Figures of Merit                                           | 24 |

|              |      | 4.5.1 Noise Figure                                         | 24 |

|              |      | 4.5.2 Third-order Intercept Point                          | 25 |

|              |      | 4.5.3 1 dB Compression Point                               | 27 |

| 5            | Imp  | plementation                                               | 29 |

|              | 5.1  | Introduction                                               | 29 |

|              | 5.2  | RF stage                                                   | 30 |

|              |      | 5.2.1 Frequency Synthesizer                                | 30 |

|              |      | 5.2.2 LNA                                                  | 34 |

|              |      | 5.2.3 Mixer                                                | 40 |

|              |      | 5.2.4 Overall circuit and PCB layout                       | 43 |

|              | 5.3  | IF stage                                                   | 44 |

|              |      | 5.3.1 IF Gain                                              | 44 |

|              |      | 5.3.2 Power Detector                                       | 46 |

|              |      | 5.3.3 Overall circuit and PCB layout                       | 47 |

|              | 5.4  | IF Filter                                                  | 48 |

|              |      | 5.4.1 Filter design using the <i>insertion loss method</i> | 48 |

|              |      | 5.4.2 Simulation                                           | 50 |

|              |      | 5.4.3 Circuit diagram & PCB layout                         | 51 |

| 6            | Test | ts & Results                                               | 53 |

|              | 6.1  | RF Stage                                                   | 53 |

|              | 6.2  | IF Stage                                                   | 58 |

|              | 6.3  | IF Filter                                                  | 62 |

| 7            | Con  | nclusions                                                  | 65 |

|              | 7.1  |                                                            | 65 |

|              | 7.2  | Future Work                                                | 66 |

| $\mathbf{A}$ |      |                                                            | 67 |

|              |      |                                                            | 67 |

|              | A.2  | IF output                                                  | 70 |

| $\mathbf{B}$ | Circ  | cui | t dia  | agra | an | ıs | & | $\mathbf{P}$ | CI | 3 | La | ıy | οι | ıtı | $\mathbf{s}$ |  |  |  |  |  |  |      |  |  |  |   | 73 |

|--------------|-------|-----|--------|------|----|----|---|--------------|----|---|----|----|----|-----|--------------|--|--|--|--|--|--|------|--|--|--|---|----|

|              | B.1   | R   | F Sta  | age  |    |    |   |              |    |   |    |    |    |     |              |  |  |  |  |  |  |      |  |  |  |   | 74 |

|              | B.2   | IF  | Sta    | ge . |    |    |   |              |    |   |    |    |    |     |              |  |  |  |  |  |  | <br> |  |  |  |   | 77 |

|              | B.3   | IF  | ` Filt | er . |    |    |   |              |    |   |    |    |    |     |              |  |  |  |  |  |  |      |  |  |  | • | 79 |

| Bi           | bliog | gra | phv    |      |    |    |   |              |    |   |    |    |    |     |              |  |  |  |  |  |  |      |  |  |  |   | 81 |

# List of Figures

| 2.1  | Example of a spectrum analyzer from Agilent [3]                        |

|------|------------------------------------------------------------------------|

| 2.2  | Simplified block diagram of a FFT spectrum analyzer                    |

| 2.3  | Block diagram of a superheterodyne spectrum analyzer, from [2]         |

| 2.4  | Block diagram of a vector signal analyzer, from [4]                    |

| 2.5  | Frequency and amplitude accuracy, from [8]                             |

| 2.6  | Sensitivity and dynamic range                                          |

| 3.1  | Ideal SDR concept                                                      |

| 3.2  | Baseband digitalization architecture                                   |

| 3.3  | IF digitalization architecture                                         |

| 3.4  | RF digitalization architecture                                         |

| 3.5  | Radio technology time evolution, from [17]                             |

| 4.1  | Block diagram of a direct conversion receiver                          |

| 4.2  | Block diagram of double conversion receiver                            |

| 4.3  | Block diagram of low IF receiver                                       |

| 4.4  | Input and output of a two tone test                                    |

| 4.5  | Third-order intercept point                                            |

| 4.6  | Two tone test: measuring IP3 with a spectrum analyzer                  |

| 4.7  | Example of a P1dB measurement, adapted from [24]                       |

| 5.1  | Block diagram of the receiver                                          |

| 5.2  | Implementation diagram of the Radio Frequency (RF) stage               |

| 5.3  | Synthesizer functional block diagram, from [25]                        |

| 5.4  | LTC1799 basic connections, adapted from [27]                           |

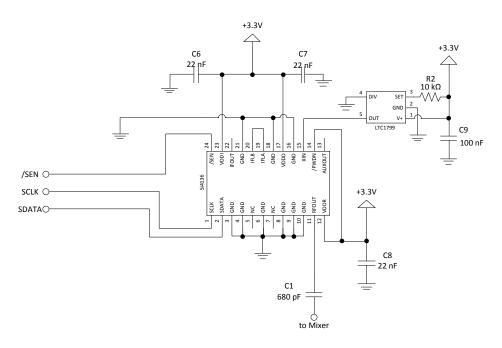

| 5.5  | Electrical diagram of the frequency synthesizer                        |

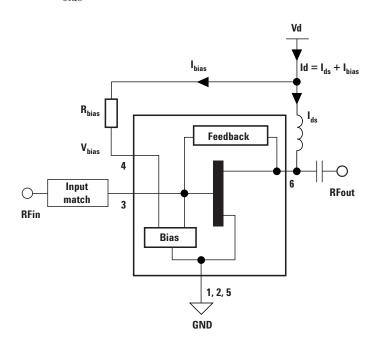

| 5.6  | MGA-62563 Low Noise Amplifier (LNA) simplified schematic, from [28] 35 |

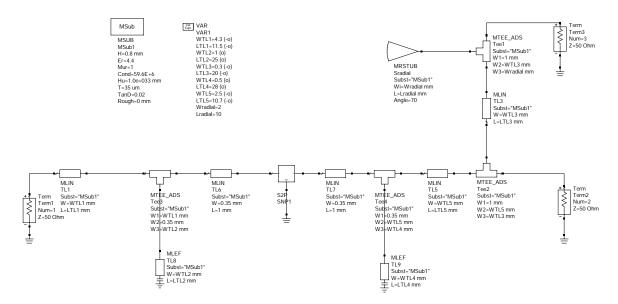

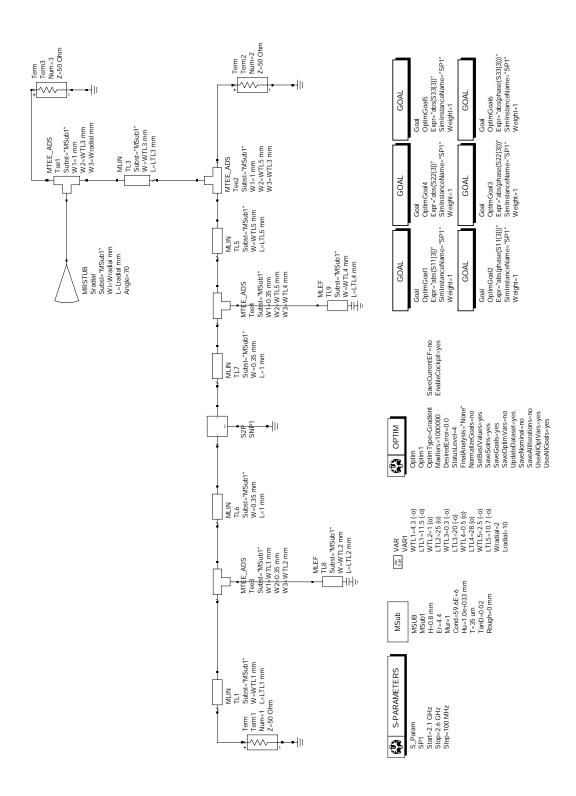

| 5.7  | LNA related circuits, simulated in ADS software                        |

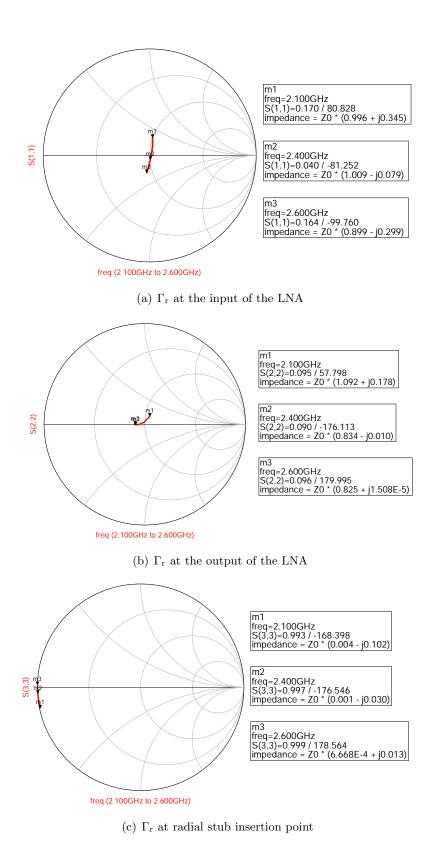

| 5.8  | Simulated reflection coefficients of the LNA with matching networks 4  |

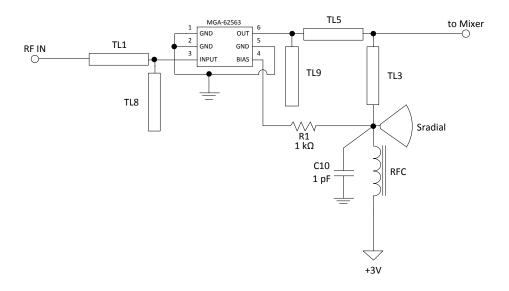

| 5.9  | Circuit diagram related to the LNA                                     |

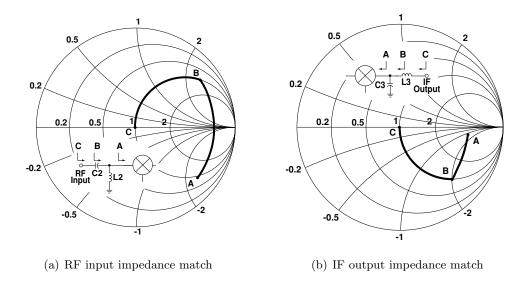

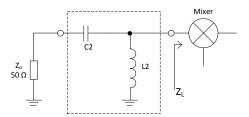

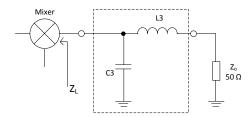

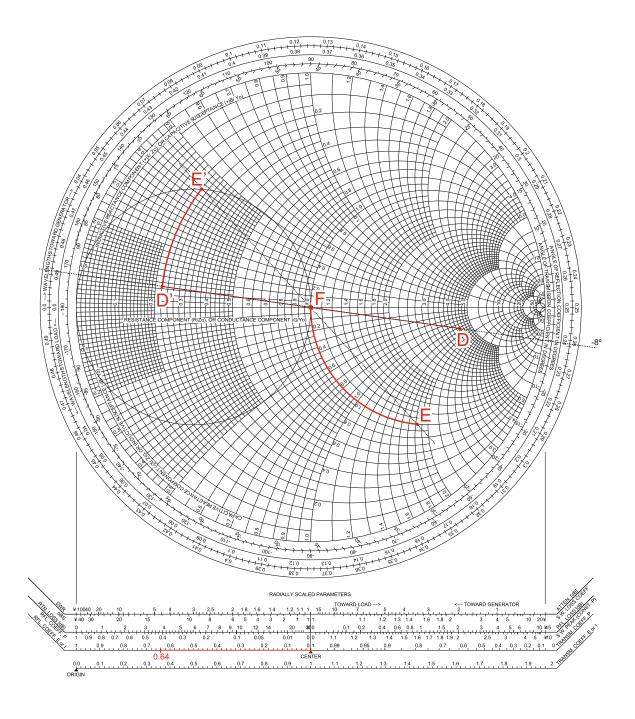

| 5.10 | Mixer's impedance matching, adapted from [31]                          |

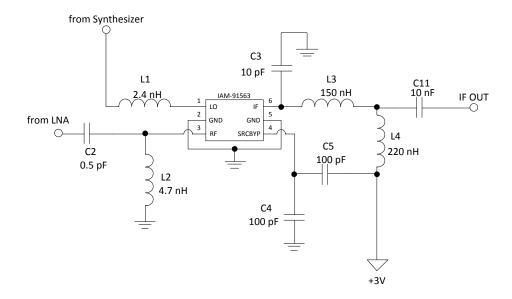

| 5.11 | Circuit diagram related to the mixer                                   |

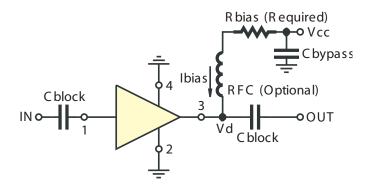

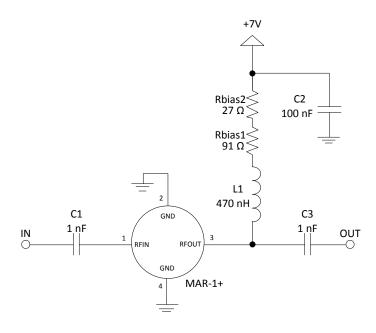

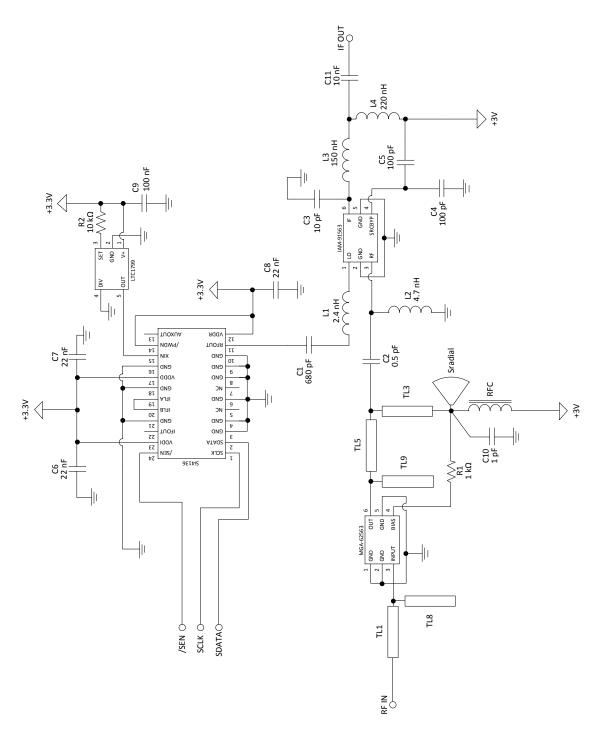

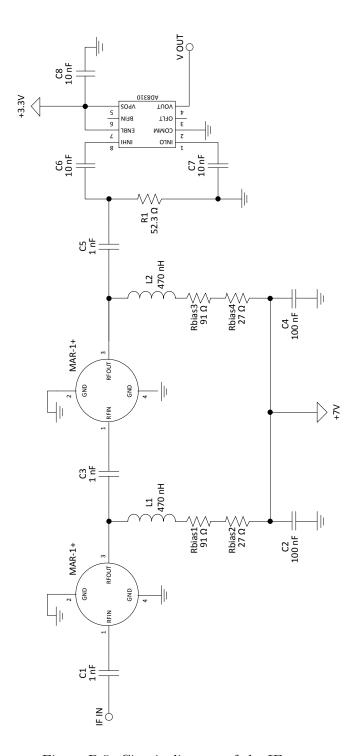

| 5 12 | Recommended application circuit for MAR-1+ from [33]                   |

| 5.13 | MAR-1+ circuit diagram                                                          | 45 |

|------|---------------------------------------------------------------------------------|----|

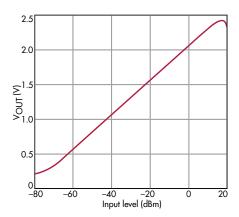

| 5.14 | Typical output curve for a logarithmic power detector, from [34]                | 46 |

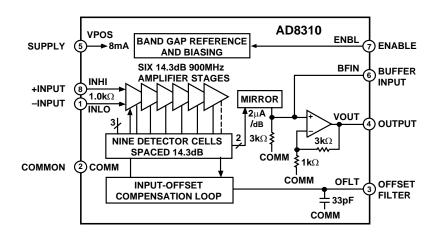

| 5.15 | AD8310 functional block diagram, from [35]                                      | 47 |

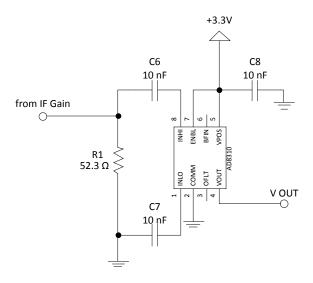

| 5.16 | AD8310 circuit diagram                                                          | 48 |

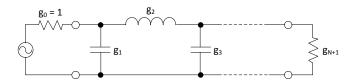

| 5.17 | Low-pass prototype filter                                                       | 49 |

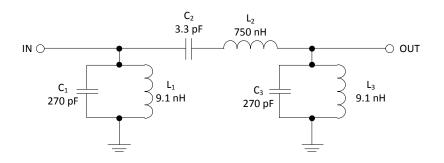

| 5.18 | Bandpass filter circuit diagram                                                 | 50 |

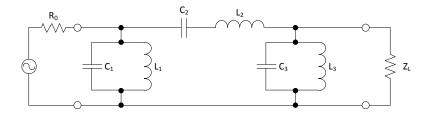

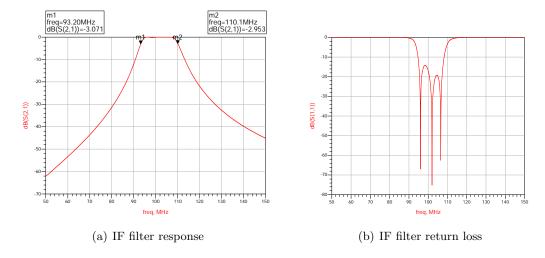

| 5.19 | Simulation of the IF filter                                                     | 51 |

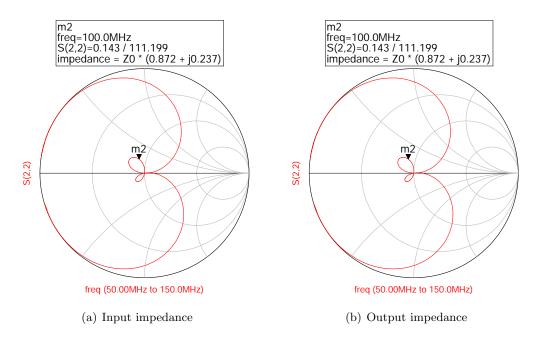

| 5.20 | Adaptation of the IF filter to $50\Omega$ [50 MHz to 150 MHz]                   | 51 |

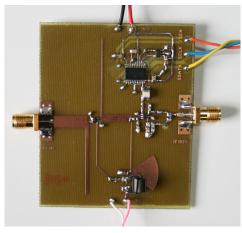

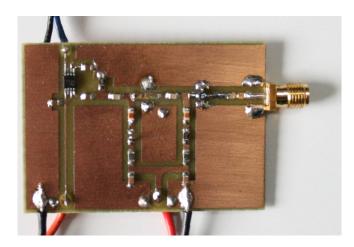

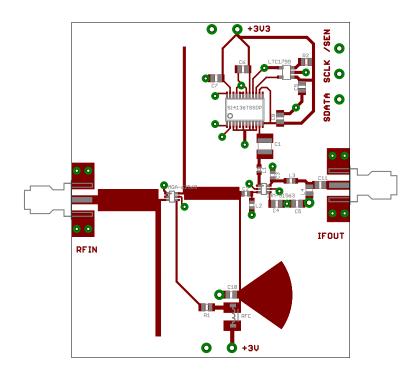

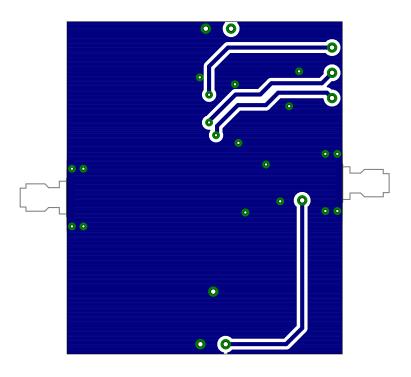

| 6.1  | Photos of RF stage's PCB                                                        | 53 |

| 6.2  | S11 parameters measured in the RF stage                                         | 54 |

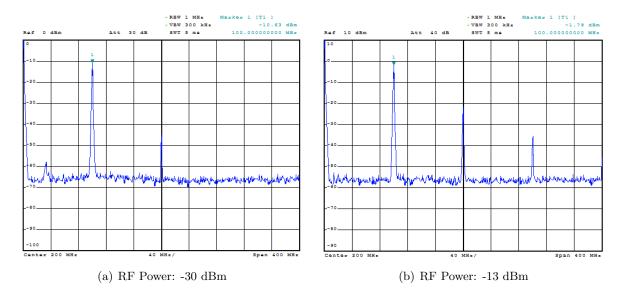

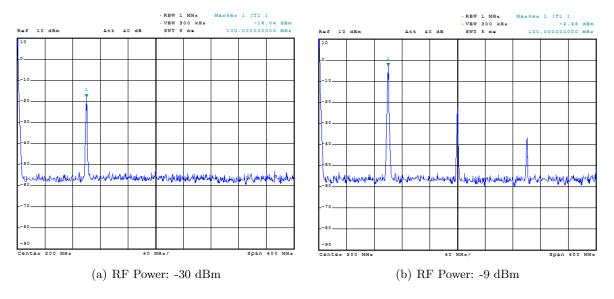

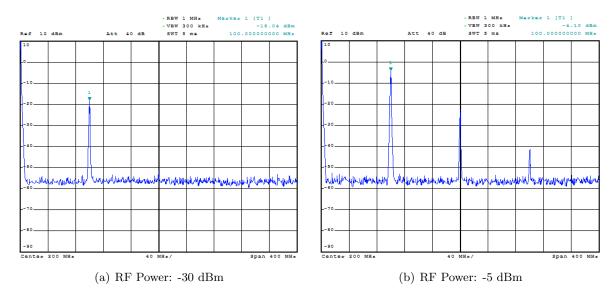

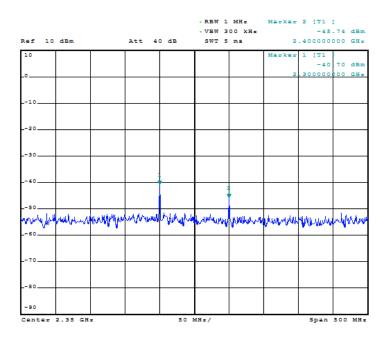

| 6.3  | Mixer's IF output: LO = -5 dBm @ 2.0 GHz and RF = 2.1 GHz $\ \ldots \ \ldots$   | 55 |

| 6.4  | Mixer's IF output: LO = -5 dBm @ 2.3 GHz and RF = 2.4 GHz $$                    | 56 |

| 6.5  | Mixer's IF output: LO = -5 dBm @ 2.5 GHz and RF = 2.6 GHz $\ \ldots \ \ldots$   | 56 |

| 6.6  | Mixer's IF output with LO = -5 dBm @ 2.3 GHz and RF = -20 dBm @ 2.4 GHz         | 57 |

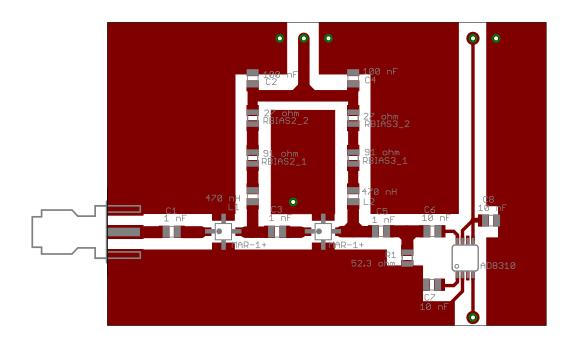

| 6.7  | Photo of the IF stage PCB                                                       | 58 |

| 6.8  | Results obtained at the input of the IF stage                                   | 59 |

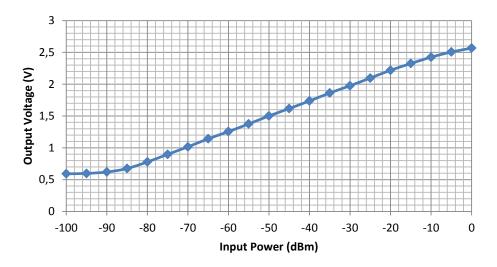

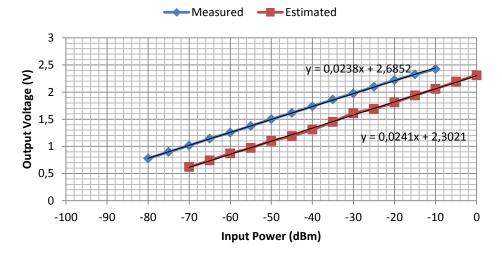

| 6.9  | Output voltage vs input power of the IF stage                                   | 60 |

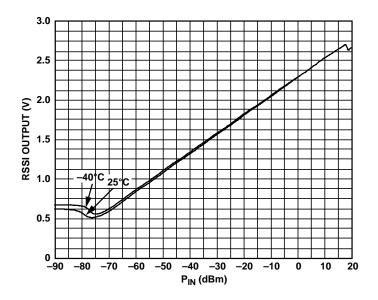

| 6.10 | Typical values of output voltage vs input power, adapted from [35]              | 61 |

| 6.11 | Comparison between estimated and measured values of output voltage              | 61 |

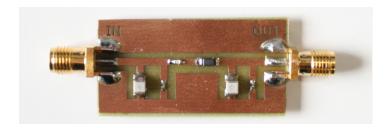

| 6.12 | Photo of the IF filter PCB                                                      | 62 |

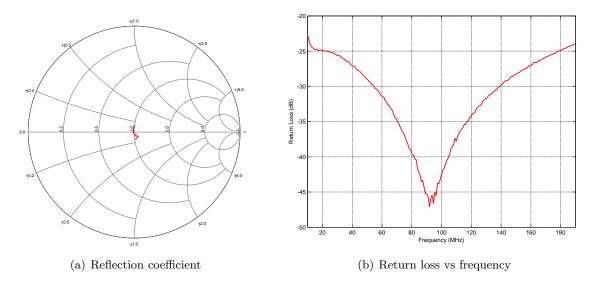

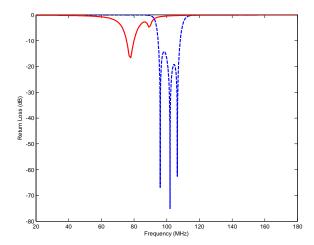

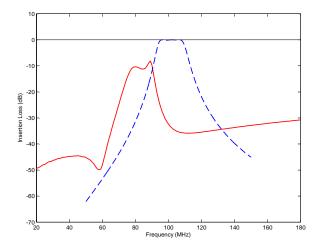

| 6.13 | Simulated (dashed blue) and measured (solid red) return loss of IF filter       | 63 |

| 6.14 | Simulated (dashed blue) and measured (solid red) insertion loss of IF filter .  | 63 |

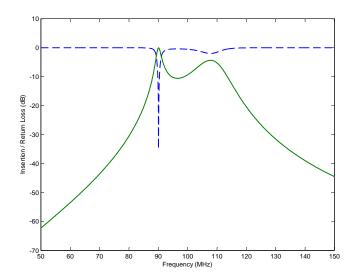

| 6.15 | Insertion loss (solid green) and return loss (dashed blue) simulation with max- |    |

|      | imum tolerance values                                                           | 64 |

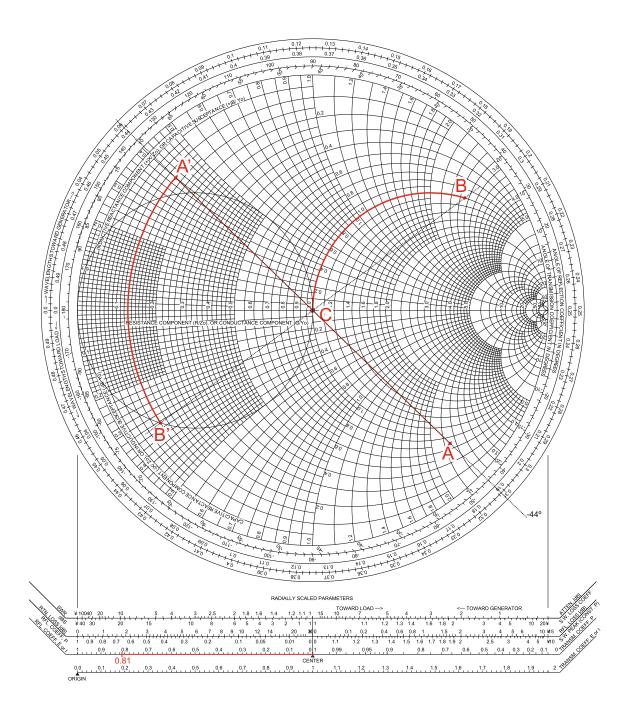

| A.1  | Mixer RF input matching network                                                 | 67 |

| A.2  | Mixer RF input matching network                                                 | 69 |

| A.3  | Mixer IF output matching network                                                | 70 |

| A.4  | Mixer IF output matching network                                                | 71 |

| В.1  | Simulation of the I/O matching networks and bias circuit of the LNA $$          | 74 |

| B.2  | Circuit diagram of the RF stage                                                 | 75 |

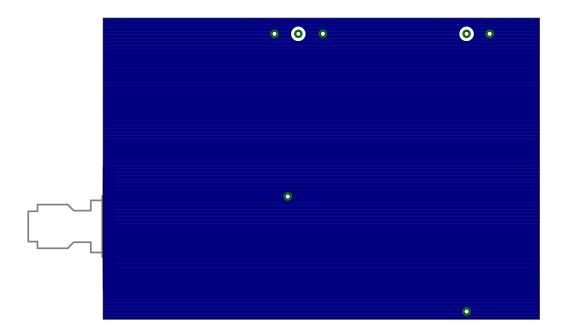

| B.3  | RF stage PCB layout (top view)                                                  | 76 |

| B.4  | RF stage PCB layout (bottom view)                                               | 76 |

| B.5  | Circuit diagram of the IF stage                                                 | 77 |

| B.6  | IF stage PCB layout (top view)                                                  | 78 |

| B.7  | IF stage PCB layout (bottom view)                                               | 78 |

| B.8  | IF filter circuit diagram                                                       | 79 |

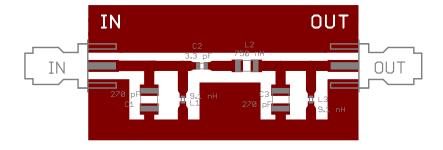

| B 9  | IF filter PCB layout (top)                                                      | 79 |

# List of Tables

| 2.1 | Typical table of specifications from a manufacturer, from [6]              | 10 |

|-----|----------------------------------------------------------------------------|----|

| 4.1 | Output frequency components from a two tone test                           | 26 |

| 5.1 | FR-4 substrate parameters                                                  | 38 |

| 5.2 | LNA's microstrip line values for the matching networks and bias circuit    | 40 |

| 5.3 | Typical reflection coefficients, $Z_0 = 50\Omega$ , $V_d = 3V$ , from [31] | 42 |

| 5.4 | 3rd order equal ripple prototype, ripple 0.1 dB                            | 49 |

| 6.1 | Output voltage of the power detector for different values of input power   | 59 |

| 6.2 | Estimation on the output voltage of the power detector                     | 61 |

# Acronyms

ADC Analog-to-Digital Converter

**ADS** Advanced Design System

AGC Automatic Gain Control

ASIC Application-specific Integrated Circuit

${f BPF}$  Band-pass Filter

CR Cognitive Radio

**DAC** Digital-to-Analog Converter

**DANL** Displayed Average Noise Level

**DC** Direct Current

**DFT** Discrete Fourier Transform

**DR** Dynamic Range

**DSP** Digital Signal Processor

**EAGLE** Easily Applicable Graphical Layout Editor

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

FR-4 FR-4 Glass Epoxy PCB substrate

**GND** Ground

**GSPS** Giga-Samples Per Second

I/O Input/Output

IC Integrated Circuit

**IEEE** Institute of Electrical and Electronics Engineers

IF Intermediate Frequency

**IMD** Intermodulation Distortion

**IP3** Third-order Intercept Point

IMR Intermodulation Ratio

ISM Industrial, Scientific and Medical

IT Instituto de Telecomunicações

JTRS Joint Tactical Radio System

LNA Low Noise Amplifier

LO Local Oscillator

LPF Low-pass Filter

MSOP Mini Small Outline Package

NF Noise Figure

P1dB 1 dB Compression Point

${f PC}$  Personal Computer

PCB Printed Circuit Board

PBAR Policy-Based Adaptive Radio

PLL Phase-locked Loop

**RBW** Resolution Bandwidth

RF Radio Frequency

**RFC** RF Choke

**RFI** Request for Information

**RMS** Root Mean Square

**RSSI** Receiver Signal Strength Indication

SCR Software Controlled Radio

SDR Software Defined Radio

**SMA** SubMiniature version A

**SMD** Surface Mount Device

${f SNR}$  Signal-to-Noise Ratio

**SOIC** Small-Outline Integrated Circuit

**SOT** Small-Outline Transistor

SR Software Radio

SSOP Shrink Small-Outline Package

${\bf TSOP}$  Thin Small-Outline Package

**ULP** User Language Program

US United States

**USB** Universal Serial Bus

${f VCO}$  Voltage-controlled Oscillator

$\mathbf{VSA}$  Vector Signal Analyzer

**WLAN** Wireless Local Area Network

Wi-Fi Wireless Fidelity

## Chapter 1

# Introduction

### 1.1 Overview

In the 19<sup>th</sup> century, James Maxwell predicted the existence of waves of oscillating electrical and magnetic fields, which is now known as electromagnetic radiation. Maxwell published his famous equations, but it was only some years later that his theory was demonstrated experimentally by the physicist Heinrich Hertz. This marks the starting point of radio history. After Maxwell and Hertz, two other individuals, Guglielmo Marconi and Nikola Tesla, stood out in what was called the "wireless telegraphy". The invention of the radio is usually attributed to Marconi, although Tesla had demonstrated the wireless telegraphy before. Despite this claim, Marconi was the first to create a wireless system that was capable of transmitting a signal at long distances. After that, many other people have contributed to bring the radio systems to the level that we know today.

With the development of radio communications, came the need for some instruments that could be used to measure some parameters of the signals transmitted and received by this radio systems, as well as to evaluate the experiments that were taking place in order to develop better radio communications. One of this instruments is the spectrum analyzer which, as the name reveals, is used to analyze the radio spectrum. This instrument became of even great importance with the proliferation of radio communication systems in the late 20<sup>th</sup> century, where the radio spectrum had become overcrowded with all the different standards and protocols. Today, the spectrum analyzer is one of the fundamental tools in an RF laboratory used to test RF equipment and to develop new prototypes that could improve radio communications. Also, it is of great importance to have a constant monitoring of the radio spectrum for several reasons, including health and fair competition, for example. The agencies that regulate the use of radio spectrum make use of the spectrum analyzer to perform this monitoring, thus reinforcing the importance of this measuring equipment.

As said previously, the radio spectrum is now overcrowded and there is no room for expansion. With the boom of radio communications, many radio standards and protocols were developed and now they have to coexist in the limited radio spectrum. Taking this into account, a new concept of a radio system that is multi-standard, multi-mode and reconfigurable, was introduced by Joseph Mitola in 1991. To this new concept, Mitola gave the

name of Software Defined Radio (SDR). In this technology, the functions of many hardware components are implemented in software, which gives the system a higher degree of freedom to work in multi-standard and multi-mode environments. With SDR technology comes the promise of solving some problems that RF engineers face today. Some of this problems are the overcrowded radio spectrum, the specificity of most RF front-ends that only work with one standard or in a narrow frequency band and the need to implement several RF front-ends in one system in order to provide for communications with more than one standard. However, the concept as Mitola first described is not possible to implement yet, mainly due to restrictions of the current technology of ADCs and DSPs. To solve this problems, approximations to the ideal concept of SDR are being implemented in order to provide current radio systems with new features such as reconfigurability which enable those radio systems to work in a multi-standard environment, for example. Considering all the advantages that SDR promises, this area is receiving much interest from researchers and is regarded as the future of radio communications.

### 1.2 Objectives

The main goal of this dissertation is to implement a low cost RF front-end that is able to realize spectrum analysis by using a SDR based system. This document is focused on the hardware component, while another dissertation [1] will focus on the software component, as well as the ADC and the USB protocol for connecting the front-end to a PC. Through this dissertation, we intend to study the spectrum analyzer as the tool to perform RF spectrum analysis and to study the concept of SDR and how it can be applied to build a spectrum analyzer. Then, the RF front-end should be developed and implemented in hardware in order to perform tests with that prototype.

### 1.3 Thesis Outline

This dissertation is organized into seven chapters and two appendices. An insight on this structure will be given in this section.

Chapter 1 presents an introduction to the project, as well as the objectives of this thesis.

In Chapter 2, several architectures of spectrum analyzers will be described. Then, the most widely used architecture is described in more detail, by explaining its theory of operation and its components.

The following chapter, Chapter 3, describes the concept of Software Defined Radio, its advantages and disadvantages, and the possibles architectures. An introduction to the concept of Cognitive Radio is also presented.

In Chapter 4, several receiver architectures will be studied in order to choose the most suitable to implement the RF receiver, that will work as a spectrum analyzer. A more detailed explanation will be provided for the components that are part of the chosen architecture.

Chapter 5 describes the hardware implementation of the receiver, divided into three main sections: RF stage, IF stage and IF filter.

The results achieved with the implemented receiver are presented in Chapter 6.

In Chapter 7, a final conclusion of the work that has been done will be given, as well as some suggestions for a future work.

This thesis will end with two appendices. The first one, Appendix A, contains the detailed explanation as well as the Smith charts used to calculate the matching networks necessary for the mixer. In Appendix B, all the circuit diagrams and the PCB layouts of the implemented hardware are presented.

## Chapter 2

# The Spectrum Analyzer

### 2.1 Introduction

The spectrum analyzer is a passive instrument used to display signal information. It is widely used to measure power over frequency, noise and distortion in RF circuits by comparing the input and output signals. In telecommunications, it is frequently used to analyze the RF spectrum to determine the occupied bandwidth of signals, their power and to track interferences [2].

An example of a commercial spectrum analyzer from Agilent<sup>1</sup> can be seen in figure 2.1. These spectrum analyzers are usually very expensive and can cover a large frequency bandwidth, up to 50 GHz.

Figure 2.1: Example of a spectrum analyzer from Agilent [3]

### 2.2 Types of Measurements

The most common measurements that can be made with a spectrum analyzer include power, modulation, distortion and noise.

<sup>&</sup>lt;sup>1</sup>Agilent Technologies is a spin-off company from Hewlett-Packard which designs and manufactures electronic and bio-analytical measurement instruments and equipment for measurement and evaluation.

#### Power

The radio spectrum is a limited and shared resource, so it is necessary to regulate and control who can use the spectrum and how it can be used. Here, the power measurement is an important tool used by the agencies that manage and regulate the radio spectrum. While monitoring the spectrum usage, they can measure power over frequency to know if someone is above the maximum limits established in telecommunications standards, for example.

For the manufacturers it is of great importance to measured the transmitted power of their devices, not only to guarantee that it does not exceed the maximum limit allowed by the regulators but also to guarantee a minimum transmitted power so that the signal can reach its destination.

### Modulation

The modulation is the process of varying one or more properties of a signal, such as frequency, amplitude and phase, so that it can be physically transmitted. By changing the properties of a signal, it is possible to make it more robust to the adverse conditions of the medium where that signal is being transmitted. Measuring the modulation of a system can be used to check if the information is being properly transmitted.

Common types of modulation measurements are: modulation degree, sideband amplitude, modulation quality and occupied bandwidth.

#### Distortion

All systems have non-linearities that cause distortion and measuring this distortion is critical for both the receiver and the transmitter. For instance, excessive harmonic distortion in a transmitter can interfere with the signal that carries the information or can interfere with other communication bands. At the receiver, the first stages must be free of intermodulation distortion to prevent crosstalk [2].

Intermodulation, harmonics and spurious emissions are common distortion measurements.

### Noise

Noise is present in all active circuits and, in a general way, is unwanted. Measuring noise figure and Signal-to-Noise Ratio (SNR) is important to evaluate the performance of a device and/or its contribution to overall system performance. Actually, noise is often the signal measured in spectrum analysis in order to understand how it can affect a system that is being tested.

### 2.3 Types of Spectrum Analyzers

There are two main types of spectrum analyzers: the swept-tuned, or superheterodyne spectrum analyzer and the Fast Fourier Transform (FFT) spectrum analyzer [2]. These two architectures will be described in the following sections. There is also another type of modern

spectrum analyzer that combines the advantages of the previous two. It is known as the Vector Signal Analyzer and it will also be described in a later section.

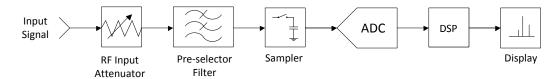

### 2.3.1 FFT Spectrum Analyzer

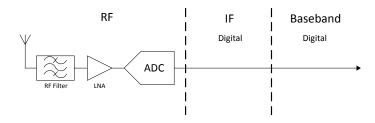

The FFT spectrum analyzer, also known as digital spectrum analyzer or simply Fourier analyzer [2], samples the time domain signal and then converts it to the frequency domain using a Discrete Fourier Transform (DFT). After the digitalization of the signal by an Analog-to-Digital Converter (ADC), a Digital Signal Processor (DSP) is used to compute the FFT algorithm. A simplified block diagram of the FFT spectrum analyzer is represented in figure 2.2.

Figure 2.2: Simplified block diagram of a FFT spectrum analyzer

In a Fourier analyzer, the fact that the signal is first digitized and then analyzed enables the signal to be captured in a relatively short time, which can be an advantage. Another advantage of this analyzer regarding the swept-tuned analyzer is the possibility to retrieve the signal's phase.

One of the main disadvantages of this spectrum analyzer is the maximum frequency limit imposed by the ADC. Even today, the ADC's maximum sampling rate isn't sufficient to digitize signals with a high frequency. To convert those signals from analog to digital it is necessary to down-convert them to a lower frequency, which will then impose limits to the bandwidth of the spectrum analyzer. Due to these limitations, the FFT spectrum analyzer is typically used in the analysis of baseband signals.

This architecture requires high performance ADCs which are expensive, so the high cost is another disadvantage of the Fourier analyzer.

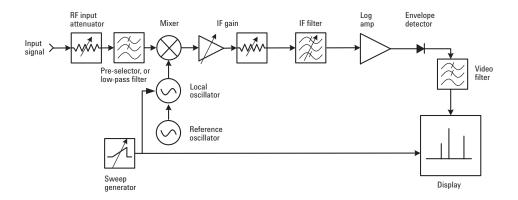

### 2.3.2 Superheterodyne Spectrum Analyzer

The superheterodyne (or swept-tuned) spectrum analyzer is by far the most used type of spectrum analyzer. As the name reveals, this type of spectrum analyzer is based on the superheterodyne principle which enables its operation up to very high frequencies.

Although this type of spectrum analyzer is expensive, the Fourier analyzer is even more expensive for the same performance level, so the superheterodyne spectrum analyzer is often preferred.

The main disadvantages of this type of spectrum analyzer is its inability to measure a signal's phase (it can only measure its amplitude) and the inability to measure transient events effectively because the sweeping of the required bandwidth takes some time.

Figure 2.3: Block diagram of a superheterodyne spectrum analyzer, from [2]

A block diagram of the superheterodyne spectrum analyzer is depicted in figure 2.3. This type of spectrum analyzer will be described in detail in section 2.4.

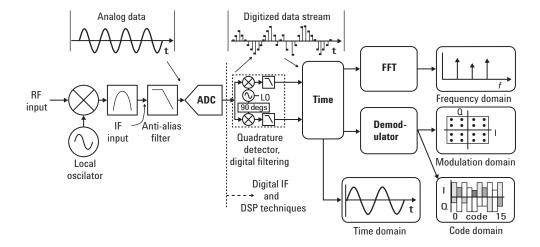

### 2.3.3 Vector Signal Analyzer

The Vector Signal Analyzer (VSA) is obtained by combining the last two spectrum analyzers technologies. The VSA digitize the time domain signal like the FFT spectrum analyzers, but also uses down-conversion like the superheterodyne spectrum analyzers [4].

Figure 2.4: Block diagram of a vector signal analyzer, from [4]

The vector signal analyzer is mainly a digital system in contrast to the analog system of the superheterodyne spectrum analyzer. Being essentially a digital system, enables the VSA to perform the same powerful measurements of the Fourier analyzer at very high frequency. The VSA is able to measure phase and to characterize complex signals such as burst, transient or modulated signals [4].

As the signals are becoming more and more complex, this type of analyzer is now a fundamental device in a modern RF laboratory.

A block diagram of the vector signal analyzer is represented in figure 2.4.

### 2.4 Theory of Operation

This section and the next will focus on the superheterodyne spectrum analyzer, as it is the most used type of spectrum analyzer.

As can be seen in figure 2.3, the major components of the superheterodyne spectrum analyzer are: RF input attenuator, mixer, Intermediate Frequency (IF) amplifier, IF filter, detector, video filter, local oscillator, sweep generator and finally the display.

The input signal passes through the RF input attenuator that will adjust the level of signal incident upon the mixer. This is important to prevent mixer gain compression or distortion due to high-level and/or broadband signals. Between the RF attenuator and the mixer, there is a Low-pass Filter (LPF) used to prevent the higher-frequency signals from reaching the mixer.

In the mixer, the output signal of the LPF is mixed with the signal from the Local Oscillator (LO) to convert it to an Intermediate Frequency (IF), lower than the frequency of the input signal. The mixer is a non-linear device, so its output will include not only the two original signals, but also their harmonics and the sums and differences of the original frequencies and their harmonics. One of the output frequencies (for example, the difference frequency) is the desired signal converted to an IF and the other (sum frequency) is known as *image frequency*.

After the mixer, there is an IF amplifier/attenuator that allows the adjustment of the vertical position of the signal on the display.

Then, to filter the image frequency there is a Band-pass Filter (BPF). This filter has an adjustable bandwidth known as the Resolution Bandwidth (RBW) because it is this filter who will impose the resolution bandwidth of the spectrum analyzer. The selectivity<sup>2</sup> is improved with a narrow RBW, which can also improve the SNR. On the other hand, with a narrower RBW the sweep speed and the trace update rate is degraded.

The signal then passes through the envelope detector to be rectified. This rectified signal is then used to drive the y-axis of the display. Modern spectrum analyzers have digital displays, so the video signal is first digitized with an ADC.

The next element in the block diagram represented in figure 2.3 is the video filter. This filter is a LPF used to smooth the trace seen on the screen.

Finally, the LO is a Voltage-controlled Oscillator (VCO) tuned by the sweep generator. The VCO responds with frequency changes proportionally to the ramp voltage of the sweep generator. It is the sweep generator who creates the frequency domain in the x-axis of the display.

<sup>&</sup>lt;sup>2</sup>Selectivity is the ability of the receiver to detect the desired signal and reject all the others [5].

### 2.5 Specifications

When working with a spectrum analyzer it is important to know its specifications. The specifications are a set of requirements that a device should satisfy. For example, if a spectrum analyzer is being used to measure the power of a RF signal, the signal's frequency must be within the frequency range of the spectrum analyzer, otherwise it is referred as being *out of specification*.

The manufacturers usually write in datasheets, user's guide or product brochures the specifications of the spectrum analyzers. That way, the user know if the spectrum analyzer is indicated for the tests and measurement the user pretend to do. Table 2.1 represents various spectrum analyzer's specifications, and is quoted from a Rohde & Schwarz's<sup>3</sup> product brochure [6].

|                                                                                                                              | R&S®FSU3                                                                             | R&S®FSU8       | R&S®FSU26                | R&S®FSU 43      | R&S®FSU46       | R&S*FSU 50      |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|--------------------------|-----------------|-----------------|-----------------|--|

| Frequency range                                                                                                              | 20 Hz to 3.6 GHz                                                                     | 20 Hz to 8 GHz | 20 Hz to 26.5 GHz        | 20 Hz to 43 GHz | 20 Hz to 46 GHz | 20 Hz to 50 GHz |  |

| Reference frequency                                                                                                          | aging: 1 $\times$ 10-7/year; with R&S $^{\circ}$ FSU-B4 option: 3 $\times$ 10-8/year |                |                          |                 |                 |                 |  |

| Spectral purity                                                                                                              |                                                                                      |                |                          |                 |                 |                 |  |

| Phase noise                                                                                                                  | typ. —133 dBc (1 Hz) at 640 MHz from carrier                                         |                |                          |                 |                 |                 |  |

| Residual FM                                                                                                                  | 1 Hz                                                                                 |                |                          |                 |                 |                 |  |

| Sweep time                                                                                                                   |                                                                                      |                |                          |                 |                 |                 |  |

| Span ≥10 Hz                                                                                                                  | 2.5 ms to 16000 s                                                                    |                |                          |                 |                 |                 |  |

| Span 0 Hz (zero span)                                                                                                        | 1 µs to 16000 s                                                                      |                |                          |                 |                 |                 |  |

| Resolution bandwidth 10 Hz to 50 MHz (R&S*FSU43: 10 Hz to 10 MHz), FFT filter: 1 Hz to 30 kHz, channel filter, EMI bandwidth |                                                                                      |                |                          |                 |                 |                 |  |

| deo bandwidth 1 Hz to 10 MHz                                                                                                 |                                                                                      |                |                          |                 |                 |                 |  |

| Display range                                                                                                                | displayed average noise level to +30 dBm                                             |                |                          |                 |                 |                 |  |

| Displayed average noise level (10 Hz RBW)                                                                                    |                                                                                      |                |                          |                 |                 |                 |  |

| 1 GHz                                                                                                                        | typ148 dBm                                                                           | typ148 dBm     | typ146 dBm               | typ146 dBm      | typ146 dBm      | typ146 dBm      |  |

| 7 GHz                                                                                                                        | -                                                                                    | typ144 dBm     | typ146 dBm               | typ143 dBm      | typ143 dBm      | typ143 dBm      |  |

| 13 GHz                                                                                                                       | -                                                                                    | -              | typ143 dBm               | typ143 dBm      | typ143 dBm      | typ143 dBm      |  |

| 26 GHz                                                                                                                       | -                                                                                    | -              | -                        | typ. –138 dBm   | typ138 dBm      | typ138 dBm      |  |

| 40 GHz                                                                                                                       | -                                                                                    | -              | -                        | typ133 dBm      | typ133 dBm      | typ126 dBm      |  |

| 50 GHz                                                                                                                       | -                                                                                    | -              | -                        | -               | -               | typ121 dBm      |  |

| Displayed average noise level with pre-<br>amplifier ON (R&S®FSU-B25), 1 GHz,<br>10 Hz RBW                                   | <-152 dBm                                                                            | <-152 dBm      | <-152 dBm                | <-152 dBm       | <-152 dBm       | <-152 dBm       |  |

| Displayed average noise level with pre-<br>amplifier ON (R&S®FSU-B23), 26 GHz,<br>10 Hz RBW                                  | -                                                                                    | -              | <-140 dBm,<br>typ150 dBm | -               | _               | -               |  |

| Trace detectors                                                                                                              | max peak, min peak, auto peak, sample, RMS, average, quasi-peak, CSIPR-AV, CSIPR-RMS |                |                          |                 |                 |                 |  |

| Total measurement error, f $< 3.6~\mathrm{GHz}$                                                                              | 0.3 dB                                                                               |                |                          |                 |                 |                 |  |

| Display linearity                                                                                                            | 0.1 dB (0 dB to -70 dB)                                                              |                |                          |                 |                 |                 |  |

Table 2.1: Typical table of specifications from a manufacturer, from [6]

The most important specifications of a spectrum analyzer are: frequency range, frequency and amplitude accuracy, frequency resolution, sensitivity, distortion and dynamic range [7, 8]. These will be explained in the following sections.

### 2.5.1 Frequency Range

When choosing a spectrum analyzer to perform some measurements, the first specification to know is the frequency range. The spectrum analyzer should cover not only the fundamental

<sup>&</sup>lt;sup>3</sup>Rohde & Schwarz is a well known German company that manufacture electronic test equipment.

frequency of the signal but also the harmonics. The baseband and IF frequencies are also important, so the spectrum analyzer should be able to measure high frequency signals (RF and harmonics) and at the same time low frequency signals (baseband and IF).

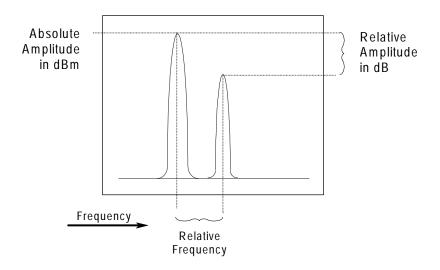

## 2.5.2 Accuracy

There are two types of accuracy specification: absolute accuracy and relative accuracy. While the absolute measurement is made with a single marker, the relative measurement is made with a delta marker which make this more accurate than the absolute measurement [8]. In spectrum analysis, both frequency and amplitude accuracy are important.

Figure 2.5: Frequency and amplitude accuracy, from [8]

#### Frequency Accuracy

The frequency accuracy of a spectrum analyzer depends upon several terms, such as the frequency readout, frequency reference accuracy, frequency span, RBW and the residual error. To provide the frequency reference for the spectrum analyzer there is usually a crystal oscillator that has a small variation of frequency with the temperature. This is why modern spectrum analyzers include an oven to control the temperature of the crystal oscillator in order to provide the best frequency accuracy possible.

#### Amplitude Accuracy

The frequency response and the display fidelity will directly affect the amplitude accuracy of the measurement. There are other items that will also affect the amplitude accuracy, but only if they are changed in the course of the measurement. Some of these item include:

• Variations in the RF input attenuator. Ideally, this element should respond equally to the entire frequency range of the spectrum analyzer, but in practice this does not

occurs. For instance, the IF gain block has a minor contribution to the amplitude accuracy because it operates only at one frequency;

- Variations in the RBW. These variations result from the different insertion losses of the filters used in the spectrum analyzer.

- Calibrator accuracy. The spectrum analyzer must be calibrated, so the calibrator accuracy is relevant to know how the measurement of a signal's amplitude is accurate.

#### 2.5.3 Frequency Resolution

This is a specification of great importance to the spectrum analyzer's user. It tells what is the frequency separation of the two closest signals that the spectrum analyzer can distinguish. If two signals are separated with less than the frequency resolution, the spectrum analyzer can't resolve the two signals, and they will appear in the display as only one signal.

#### 2.5.4 Sensitivity

The sensitivity of a receiver defines the weakest signal level that the receiver can detect to produce a desired SNR [5]. It depends on the temperature, bandwidth of the signal, noise figure of the receiver and the SNR desired. The sensitivity  $S_i$  can be defined as:

$$S_i = k \cdot T \cdot B \cdot NF \cdot SNR \text{ [W]}$$

where  $k = 1.38 \times 10^{-23} J K^{-1}$  is the Boltzmann's constant, T is the equivalent noise temperature in Kelvin, B is the bandwidth of the signal, NF is the noise figure of the receiver and SNR is the signal to noise ratio.

At room temperature (T = 290K), kT is equal to -174 dBm/Hz, so equation (2.1) can be re-written as:

$$S_i = -174 \text{ dBm/Hz} + 10 \log(B) + NF \text{ dB} + SNR \text{ dB} \text{ [dBm]}$$

(2.2)

Another specification of a spectrum analyzer that is related to the sensitivity is the Displayed Average Noise Level (DANL). This is the term for the noise floor of the spectrum analyzer, in a particular bandwidth and represents the best-case sensitivity of the spectrum analyzer in that bandwidth. This best-case sensitivity is achieved when there is minimum RF input attenuation and the RBW is the narrowest possible.

#### 2.5.5 Distortion

The spectrum analyzer is often used to measure signal distortion, but its components also add some distortion. For instance, the mixers are non-linear devices that will generate internal distortion and in the worst case scenario, this internal distortion can cover up the signal's distortion we want to measure. Therefore, this specification is very important and is specified by the manufacturer.

This specification, particularly the Intermodulation Distortion (IMD), will be discussed later in section 4.5.2, where the IP3 figure of merit will be presented.

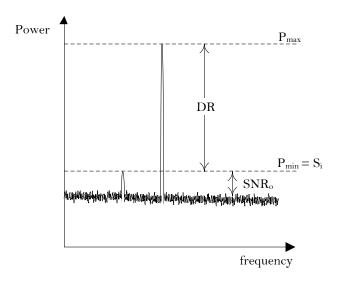

Figure 2.6: Sensitivity and dynamic range

## 2.5.6 Dynamic Range

Dynamic range is, by definition, the maximum ratio of two signal levels simultaneously present at the input of the spectrum analyzer that allows the signals to be measured to a given degree of uncertainty [2]. Graphically, it is determined in a spectrum analyzer's display like the one depicted in figure 2.6, where the dynamic range is represented as DR, the difference between the maximum signal and the minimum signal at the input. This specification is expressed in dB by the manufacturers since it is a ratio between two signal powers.

# Chapter 3

# Software Defined Radio

## 3.1 Introduction

In the early 1990s, Joseph Mitola introduced the concept of Software Defined Radio (SDR). He described SDR as:

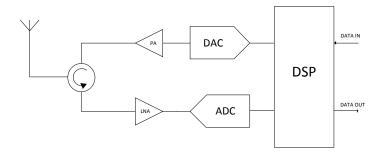

"A software radio is a radio whose channel modulation waveforms are defined in software. That is, waveforms are generated as sampled digital signals, converted from digital to analog via a wideband Digital-to-Analog Converter (DAC) and then possibly upconverted from IF to RF. The receiver, similarly, employs a wideband ADC that captures all of the channels of the software radio node. The receiver then extracts, downconverts and demodulates the channel waveform using software on a general purpose processor." [9]

In other words, the concept of SDR proposes that the digital-to-analog conversion (in the transmitter) and the analog-to-digital conversion (in the receiver) is performed as close as possible to the antenna.

The ideal SDR transceiver is depicted in figure 3.1. The filters, mixers, modulators or demodulators and others, are implemented in software using a DSP. This provides the system with flexibility because it only requires switching the software in order to adapt the system to another standard.

Figure 3.1: Ideal SDR concept

Although Joseph Mitola coined the term Software Defined Radio in 1991, the concept of a reconfigurable, multi-mode and multi-band system was introduced several years before, in the 1970s, by the US military with a project called Speakeasy [10]. The purpose of Speakeasy was to emulate several military radios into one unique radio by using programmable processing. This project was a success in creating a software-defined radio capable of emulating more than 10 different military radios that operated from 2 MHz to 2 GHz. Although the Speakeasy was portable, it was not a handheld radio.

With the conclusion of the Speakeasy project, a new project named Joint Tactical Radio System (JTRS) was born [11, 12]. This radio system is planned to be the next-generation radio used by the US military and can be seen as an improvement of Speakeasy project. It provides the capability to communicate with systems that use similar or diverse waveforms, which gives the military flexibility to communicate with different standards while maintaining the interoperability between new and old radio systems. Also, the JTRS is planned to help reducing costs in the fields of operation, training and maintenance.

Nowadays, there is an even greater need for a unique multi-standard and multi-mode hardware platform that is re-programmable and reconfigurable by software. This need comes from the excess of mobile system standards enhanced by the rapid growth occurred in the telecommunications world since the massive use of cellphones. One porpuse of SDR is to solve this problem, but unfortunately the ideal concept is very difficult to implement at this time or even in the nearest future, due to the restrictions imposed by the state-of-art hardware, such as the antenna, the ADC/DAC or the DSP [13].

An SDR system should have one or more of the following characteristics [14]:

- a transceiver architecture that can be controlled and programmed by software;

- radio functions mainly implemented in DSP;

- re-programmability via air interface;

- support for multi-standards and multi-mode.

## 3.2 Front-End Receiver Architectures

As the ideal SDR represented in figure 3.1 is not possible to implement at the present time, other architectures have to be considered to implement SDR. These architectures differ in the place where the digitalization occurs, so three types of configurations will be considered: baseband digitalization, IF digitalization and RF digitalization. These configurations will be presented over the next subsections.

### 3.2.1 Baseband Digitalization

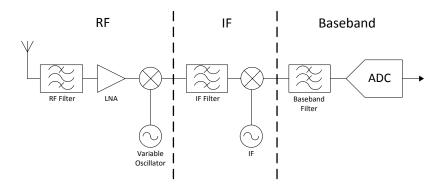

In the baseband digitalization, the ADC is placed in the baseband stage and the signal suffers two down-conversions before reaching the baseband frequency, as depicted in figure 3.2.

Although this architecture is widely used in radio receivers, it is not suitable for SDR. Because it is an architecture that is designed for narrowband porpuse, it goes against one of

Figure 3.2: Baseband digitalization architecture

the objectives of an SDR system, which is to be broadband. Another problem is the number of components required by this architecture, which make the integration of the system in a single Integrated Circuit (IC) difficult to implement.

## 3.2.2 IF Digitalization

In this approach, the ADC is now placed in the IF stage. This allows for a wider bandwidth when compared to the previous architecture, thus making this implementation closer to the ideal SDR. Now, the received band can be wider, and since the digitalization is done at IF, digital filters and further processing can be used for channel selection. This architecture allows for more standards to be implemented and it is suitable of being realized with the components currently available. That is the reason why this architecture is the most feasible and preferred to implement a SDR system these days.

Figure 3.3: IF digitalization architecture

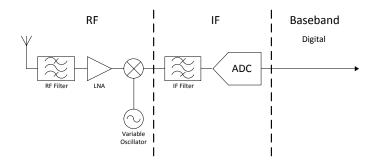

## 3.2.3 RF Digitalization

By moving the ADC closer to the antenna once more, the digitalization is now performed at RF. This is the final architecture of the evolution of SDR and is the one proposed by Joseph Mitola as the ideal SDR architecture, but unfortunately is still utopical. The ADC must have both high dynamic range and high sampling ratio, preferably with a large number

of resolution bits. Nowadays, there are high-speed ADCs that can achieve high sampling rate with a fair number of resolution bits, but they are too expensive. For instance, one of the best ADCs in the market is manufactured by National Semiconductor<sup>1</sup> and has a sampling rate of 3.6 GSPS with 12 resolution bits [15], costing over \$3,000, which is too expensive for commercial applications.

Figure 3.4: RF digitalization architecture

A lot of research is yet to be done in the field of ADCs and DSPs in order to implement the RF digitalization. For now, the most feasible implementation for a SDR system is the IF digitalization which is still somewhat expensive for high IFs.

#### 3.3 SDR Concerns

One of the key components in SDR is the ADC. The most important parameters of an ADC are the sampling rate, the number of bits (resolution) and the dynamic range. Advances in this area allowed the ADC to move from baseband to IF, sampling the signal at higher frequencies. As stated before, there are now in the market high speed ADCs with sampling rates of GSPS but they are too expensive and are not feasible for implementation in commercial applications where the end user normally want low cost systems. Another drawback is the power consumption because the higher the speed of the ADC, the higher the power consumption will be. This limits the application of these ADCs because one important characteristic of a radio system is its portability, which would be limited through battery life. That is why the current research on ADCs focus in increasing sampling rate and reducing power consumption.

The processing unit is also of great importance in an SDR system. This unit has to keep up with the speed of ADC to be able to process all the digital signal. An ASIC can perform this processing with good performance and high speed; however, it is limited to the functionalities for which it was design. In an SDR system this is not very useful because it does not provide the system with the desired reconfigurability. Currently, this processing is mainly done with DSPs, which have lower performance than ASICs but can provide the system with more flexibility.

<sup>&</sup>lt;sup>1</sup>National Semiconductor is a company founded in 1959 that designs and produces integrated circuits, such as amplifiers, data converters, etc. It has more than 10,000 products and a number of patents that exceeds 3,000. It has reported \$1.42 billion in sales for fiscal 2010.

Both ASICs and DSPs have pros and cons and in an attempt to conjugate the pros of both components, the FPGA arises. An FPGA is an IC that is designed to be reconfigurable and reprogrammable and is able to perform complex operations such as the ones performed by an ASIC. For its characteristics, the FPGA is a desired component for an SDR system, but this comes with a price. The FPGAs are usually very expensive compared to ASICs or DSPs.

# 3.4 Cognitive Radio

With the concept of SDR, Joseph Mitola came up with a new idea, the Cognitive Radio (CR) [16]. This new concept can be viewed as an upgrade of SDR, because it is an intelligent radio that is aware of the environment in which it is inserted, that is, location and utilization of the RF spectrum. Therefore, the CR can make decisions based on the knowledge acquired by itself in order to give the best communications experience to end-users. While doing this, the CR must be fair with other users and obey to the basics rules of RF spectrum sharing.

The CR should be able to operate in a wide range of frequencies, have support for multi-standard and multi-mode and be re-programmable, just like an SDR. The advantage of CR over SDR is the capability of making decisions for itself.

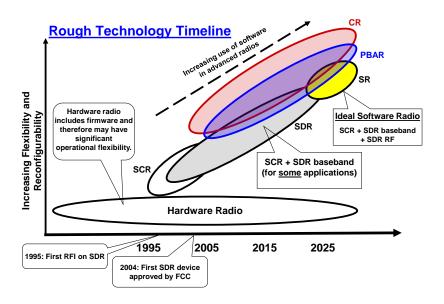

Figure 3.5: Radio technology time evolution, from [17]

For a better understanding of this concept, let's take an example of a CR that is using Wi-Fi. While monitoring the RF spectrum, the CR detects that the channel used is too crowded with other users, so in order to avoid interference and to improve the quality of the communication the CR automatically changes to another frequency channel that is less occupied. The user is unaware of that change because this process is totally transparent to the end-user.

At the beginning, the CRs and SDRs may be expensive due to the high performance components required, but with the advance of technology and mass production the cost of this type of radios would become less expensive to the end-user, allowing for better communications. In figure 3.5 it is represented the expected evolution of the radio technology, predicted by Hoffmeyer [17]. With this in mind, it can be said that the future of radio communications will pass through SDRs and CRs!

# Chapter 4

# Receiver Architecture

### 4.1 Introduction

Due to the analog nature of the air interface where the radio waves propagate, a Software Defined Radio will always have an analog front-end to receive the radio signals called the RF receiver. This is an electronic circuit whose purpose is to receive a RF signal and to perform some operations with that signal, such as amplification, filtering and frequency mixing. The objectives of the receiver RF front-end are [5]:

- capture the desired signal while rejecting unwanted signals;

- convert the signal's center frequency to a range that is compatible with the ADC. This should be performed with minimal distortion;

- amplify the signal to match the level required by the ADC;

- minimize the noise added while performing amplification and frequency mixing.

This chapter is intended to describe some receiver's architectures and to compare the advantages and disadvantages of these architectures in order to find the best suitable architecture for SDR receiver.

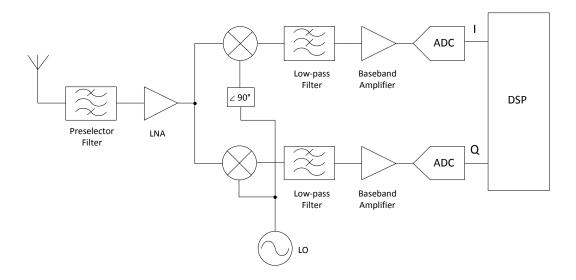

## 4.2 Direct Conversion Architecture

In a direct conversion receiver, the received signal is down-converted directly to the baseband using a mixer and a local oscillator. Because the frequency of the local oscillator is set to the same frequency of the desired input signal, this type of receiver is also called a homodyne receiver [18]. A block diagram of this type of receiver is presented in figure 4.1.

In this receiver, the input signal is filtered in order to attenuate undesired signals and is amplified in a LNA. Then, a mixer and a LO are used to down-convert the signal directly to baseband. Two signals will then appear at the output of the mixer: one is the baseband signal and the other is a signal whose frequency is twice the frequency of the input signal.

Figure 4.1: Block diagram of a direct conversion receiver

This last signal is also known as the *image frequency* signal and to remove it a low-pass filter is used. Later, the wanted signal is amplified in order to fit in the ADC's dynamic range.

The advantages of this receiver, when compared to a multiple conversion receiver, are [18, 19, 20]:

- low complexity;

- simple filtering requirements;

- easier image frequency suppression.

As this receiver doesn't have an IF, it is simpler and less costly than a multiple conversion receiver. The low-pass filter in the baseband stage is also easier to implement than a narrow band-pass filter required at the IF stage of a multiple conversion receiver.

Despite this advantages, there are some disadvantages that makes the direct conversion receiver difficult to implement, such as [18, 19, 20]:

- LO drift;

- DC offset;

- LO-to-RF and RF-to-LO leakage;

- ADC sampling rate.

The LO must be of high precision and stability so that the desired RF signal is correctly down-converted to the baseband. The Direct Current (DC) offset is another major problem in a homodyne receiver. This can occur if the LO signal leaks to the input of the LNA because the LO and the RF frequencies are equal. The RF signal usually has a very low power when

compared to the LO signal and if this leakage occurs, the LO signal is mixed with itself to produce a DC voltage that will be present at the input of the baseband amplifier.

In the past, one of the biggest obstacles to implement this type of receiver was the low sampling rate and resolution of the ADCs. As stated in subsection 3.2.3, in the present time there are high-speed ADCs that can achieve high sampling rate with a fair number of resolution bits, but they are too expensive.

The homodyne architecture enables wideband signals to be received [13], which is an important feature of an SDR receiver, but the limitations described above makes this type of receiver to be difficult to implement with low cost components, because it requires expensive components (such as a very stable LO).

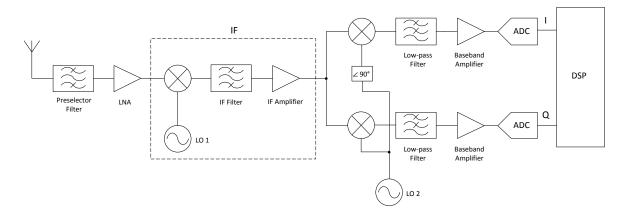

# 4.3 Multiple Conversion Architecture

In the multiple conversion receiver, the desired signal is firstly down-converted to an intermediary frequency before it is down-converted to baseband. This type of receiver is known as a superheterodyne receiver, and in the figure 4.2 it is represented a superheterodyne with two down-conversions.

Figure 4.2: Block diagram of double conversion receiver

Despite having its own disadvantages, this type of receiver can overcome the main problems of the homodyne architecture. This is one of the reasons why nowadays the superheterodyne receiver is used in the majority of the communications systems, such as cellular telephone systems, data communication systems and radar systems [18].

As can be seen in the figure 4.2, the first stage is similar to the direct conversion receiver. The main difference is that in the multiple conversion receiver there is an intermediary stage between the RF and the baseband stages. One problem that arises with this architecture is the presence of an *image frequency* at the output of the first mixer. In order to prevent this signal from reaching the second mixer, the IF band-pass filter should have a narrow bandwidth. This type of filter is more difficult to implement than the low-pass filter required in the direct conversion receiver, so this is a disadvantage of this architecture.

A superheterodyne receiver has a better performance than a homodyne receiver because it does not suffer from the problems caused by DC offsets and self-mixing at the input of the mixers. However, the incapability of dealing with wideband signals [13] dictates that this architecture is not suitable to use in a SDR system.

## 4.4 Low IF Architecture

To overcome the problems in the two architectures presented before, it was developed another architecture [21, 20] that combine the best features of the two presented above. The conversion from analog to digital is done at IF instead of being done at baseband, so there is no problem with DC-offset because the wanted signal is not located around DC. Also, the LO frequency is not equal to the RF carrier signal, so the LO-to-RF and RF-to-LO isolation is not as important as the one needed in the homodyne receiver.

Figure 4.3: Block diagram of low IF receiver

As can be seen in figure 4.3, the ADC is placed in the IF stage closer to the antenna than in the other two architectures. This architecture is suitable to be used in a SDR communication system and it is a close approach to the ideal SDR receiver (figure 3.1). For this reason, the low IF architecture was the one chosen to implement the front-end of the spectrum analyzer.

# 4.5 Figures of Merit

To better understand the operation of the RF receiver, some important figures of merit that characterize the elements used in the receiver will be explained in the following subsections. These figures of merit are: Noise Figure (NF), Third-order Intercept Point (IP3) and 1 dB Compression Point (P1dB).

#### 4.5.1 Noise Figure

The Noise Figure (NF) is an important figure of merit, specially for the LNA. It is defined as [22]:

$$NF = \frac{SNR_i}{SNR_o} \tag{4.1}$$

where  $SNR_i$  is the signal-to-noise ratio of the input and  $SNR_o$  is the signal-to-noise ratio at the output.

The NF is a measure of the degradation in SNR between the input and output ports of the device. A RF receiver is composed by several devices, so in order to calculate the overall noise figure of the receiver, the following equation is used:

$$NF_T = NF_1 + \frac{NF_2 - 1}{G_1} + \frac{NF_3 - 1}{G_1 \cdot G_2} + \frac{NF_4 - 1}{G_1 \cdot G_2 \cdot G_3} + \dots$$

(4.2)

where  $NF_n$  is the noise factor of each stage and  $G_n$  is the numerical gain of each stage (not in dB).

This expression and its deduction can be found in [23], and in many other books about RF. Equation 4.2 shows that the first stage is the one who has a larger contribution to the total NF of the system, and this is the reason why the first amplifier of the receiver must have a low noise figure.

#### 4.5.2 Third-order Intercept Point

Another important figure of merit is the Third-order Intercept Point (IP3). This parameter is related with the linearity and is used to calculate the Intermodulation Distortion (IMD).

Intermodulation products are a source of distortion in non-linear devices. Even devices that are assumed to be linear, can have non-linearities in certain conditions of operation. For example, when two RF signals with the same amplitude are applied to the input of the mixer,

$$v(t) = A\cos 2\pi f_1 t + A\cos 2\pi f_2 t \tag{4.3}$$

the output voltage can be represented as the power series:

$$v_o(t) = a_1 v(t) + a_2 v^2(t) + a_3 v^3(t)$$

(4.4)

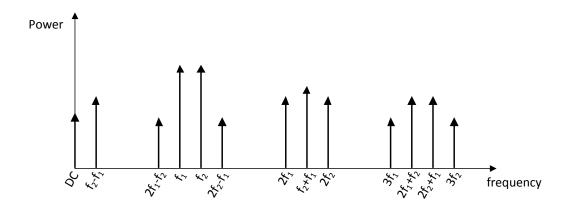

This output signal will contain several frequency components, where the most important are presented in table 4.1 and are shown graphically in figure 4.4. Placing two sinusoidal signals at the input of a device while reading the response at the output is a common test that is done to characterize and understand how the device works; this is known as the *two tone test*.

In figure 4.4, we can see that the IMD products will appear inside the bandwidth. Because of this, the removal of these frequency components is very difficult to do with a simple filter. Another problem of IMD is that the two can mask the desired signal if their power is sufficiently high.

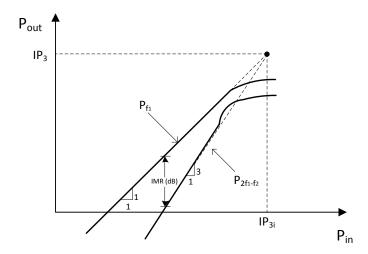

As an example, when measuring the output power of the third-order intermodulation product  $P_{2f_1-f_2}$  versus the input power  $P_{f_1}$ , we obtain the graphic shown in figure 4.5. The slope of the fundamental output power is 1 dB/dB and the slope of the IMD products output power is 3 dB/dB. This occurs because the power of the third-order IMD is proportional to the cube of the input signal (equation 4.4). By definition, the third-order intercept point is the point where the extrapolated lines  $P_{f_1}$  and  $P_{2f_1-f_2}$  intersect each other. This is a conceptual point that does not exist in reality because at very large signal levels, both curves

Figure 4.4: Input and output of a two tone test

| Description                                          | Frequency component |

|------------------------------------------------------|---------------------|

| Component resulting from $f_1 - f_1$ and $f_2 - f_2$ | DC                  |

| $f_1$ fundamental frequency                          | $f_1$               |

| $f_2$ fundamental frequency                          | $f_2$               |

| $f_1$ second harmonic                                | $2f_1$              |

| $f_2$ second harmonic                                | $2f_2$              |

| $f_1$ third harmonic                                 | $3f_1$              |

| $f_2$ third harmonic                                 | $3f_2$              |

| Second-order intermodulation products                | $f_2 \pm f_1$       |

| Third-order intermodulation products                 | $2f_1 \pm f_2$      |

| Third-order intermodulation products                 | $2f_2 \pm f_1$      |

Table 4.1: Output frequency components from a two tone test

tend to compress towards a constant value of output power due to the contribution of higher order terms [24].

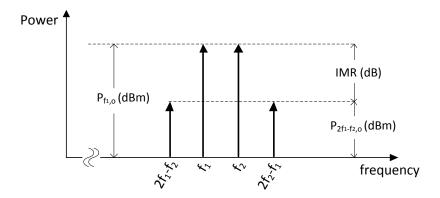

Another important figure of merit directly related with intermodulation distortion is the Intermodulation Ratio (IMR), which is defined as the ratio between the fundamental output power and the IMD output power:

$$IMR = \frac{P_{f_1,o}}{P_{2f_1 - f_2,o}} = \frac{P_{f_2,o}}{P_{2f_2 - f_1,o}}$$

(4.5)

or in dB units:

$$IMR_{dB} = P_{f_1,o} (dBm) - P_{2f_1 - f_2,o} (dBm) = P_{f_2,o} (dBm) - P_{2f_2 - f_1,o} (dBm)$$

(4.6)

In figure 4.6 is represented a typical spectrum analyzer's display when a two tone test is

Figure 4.5: Third-order intercept point

Figure 4.6: Two tone test: measuring IP3 with a spectrum analyzer

being performed in a RF device. Using this display of the spectrum analyzer, the IP3 can be calculated as:

IP3 (dBm) =

$$P_{f_1,o}$$

(dBm) +  $\frac{\text{IMR}_{dB}}{2}$  (4.7)

From (4.7) it can be observed that, for the same  $P_{f_1,o}$  value, the higher the IP3 is, the higher, and therefore better, the IMR will be.

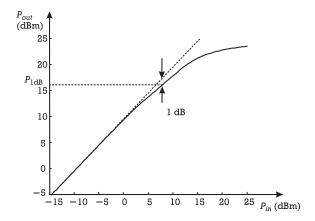

#### 4.5.3 1 dB Compression Point

As seen before, in the linear zone of an amplifier the output power raises 1 dB for each dB raised in the input power, for the fundamental frequency. However, the amplifier cannot maintain this ratio indefinitely and there is a certain point where the amplifier saturates and starts to compress the signal. This point is typically specified as the 1 dB Compression Point (P1dB) by the manufacturers and is defined as the value of output power at which the

output signal is compressed in 1 dB compared to the extrapolated line of the small-signal characteristic of the linear system [24].

This is an important figure of merit for amplifiers because they have to be kept working far from this point, otherwise the amplifier could enter in the non-linear zone adding more distortion to the system where the amplifier is inserted. Figure 4.7 represents an example of a P1dB measurement.

Figure 4.7: Example of a P1dB measurement, adapted from [24]

# Chapter 5

# **Implementation**

#### 5.1 Introduction

In this chapter, the implementation of the receiver's hardware will be explained. The components chosen will be presented, as well as the reasons why they were chosen. Also, the electric diagrams and the Printed Circuit Board (PCB) layouts will be presented.

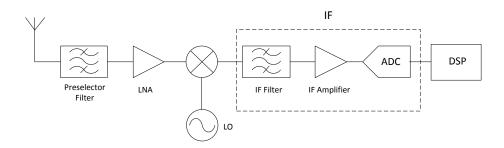

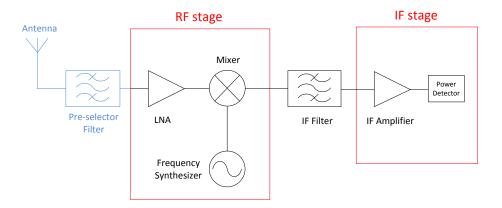

While studying the best approach to implement the receiver, it quickly became clear that if the hardware was divided in various boards, instead of being only one, the implementation and testing of the hardware would become easier. For that reason, it was decided to divided the receiver in four stages, as represented in figure 5.1:

- The antenna and the pre-selector filter;

- The RF stage, with the LNA, the mixer and the frequency synthesizer;

- The IF filter;

- The IF stage, with the IF amplifier and the power detector.

Figure 5.1: Block diagram of the receiver

This thesis work has focused on the RF stage, the IF stage and the IF filter, so this chapter will explain the implementation of these stages. The antenna and the pre-selector filter weren't implemented, so they will not be referred in this chapter.

# 5.2 RF stage

The RF stage is composed by one LNA, one mixer and one frequency synthesizer. This stage will receive an input frequency of 2.1 GHz to 2.6 GHz (RF frequency) and will have an output frequency of 100 MHz (IF frequency).

These components work at RF and IF frequencies and they will need impedance matching circuits for the inputs/outputs as well as bias circuits to provide the supply power needed. Therefore, a diagram of the implementation of this stage is presented in figure 5.2.

Figure 5.2: Implementation diagram of the RF stage

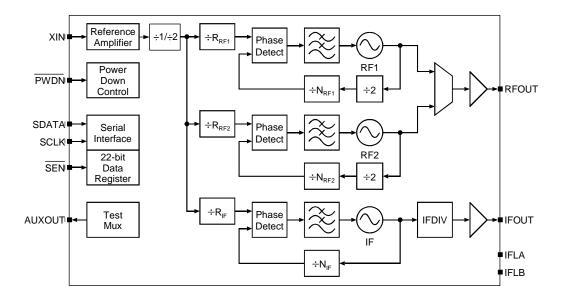

#### 5.2.1 Frequency Synthesizer

The frequency synthesizer will be the first one explained here because it was the choice of this component that limited the frequency range of the RF signals.

The frequency synthesizer consists of two main components: a Phase-locked Loop (PLL) and a VCO. Attending to this information, the frequency synthesizer could be bought as one monolithic IC or it could be realized with a PLL and a VCO. To implement a simple and low cost receiver, is was decided to buy the frequency synthesizer as one monolithic IC.

From the beginning it was intended that the frequency synthesizer could generate a wide range of frequencies around the ISM band of 2.4 GHz to 2.5 GHz, because this is the frequency range used by many communication standards, such as IEEE 802.11 (Wi-Fi, WLAN), IEEE 802.15.4 (ZigBee) and Bluetooth. The characteristics wanted in the frequency synthesizer are:

- low supply voltage, preferably 3V, 3.3V or 5V because these are common supply voltages found in many circuits;