Universidade de Aveiro Departamento de Electrónica e Telecomunicações

# Synthesis and Simulation of Reprogrammable Control Units from Hierarchical Specifications

# Synthesis and Simulation of Reprogrammable Control Units from Hierarchical Specifications

#### António Manuel Adrego da Rocha

Departamento de Electrónica e Telecomunicações Universidade de Aveiro Portugal, May, 1999

Thesis submitted in fulfilment of the requirements for the degree of Doutor em Engenharia Electrotécnica

## Acknowledgements

I would like to thank to my thesis supervisors. To Valery Sklyarov for introducing me in the field of hierarchical finite state machines with stack memory and for having proposed and supervised this work. To António Ferrari for the many comments and suggestions in order to improve this thesis, and also for the corrections regarding the proper use of the English language. They deserve my sincere gratitude.

I am also indebted to Artur Pereira for his expertise in Petri nets and to António Rui Borges for the helpful discussions and suggestions concerning the contents of some chapters of this thesis.

I would also like to thank to every one in the Departamento de Electrónica e Telecomunicações and INESC, especially to all members in the Computer group, for their support and encouragement.

This work was supported by the grant PRODEP Formação n° 35/3/94. The financial support of the Human Capital and Mobility Programme of the European Community under contract CHRX-CT94-0459, the Network "Behavioural Design Methodologies for Digital Systems", that made possible the presentation and discussion of part of this work is also acknowledge.

Finally, thanks to my family and friends, in particular to my parents Maria and João and my sister Rosa for their love, patience and support. This work is dedicated to them.

#### **Abstract**

Finite state machines (FSM) have been a topic of great importance in the last five decades and have been used to specify and implement control units. Due to the increasing complexity of control units and since the FSM model does not explicitly support hierarchy and concurrency, new state-based models with hierarchical and concurrent constructions were proposed in order to overcome the limitations of the conventional FSM model and allowing the specification of complex control units in a top-down manner. Still, there are not many hierarchical FSM architectures (HFSM) that have been proposed to implement those hierarchical specifications and most of them cannot be seen as a whole FSM implementing internally in an efficient way the switching between the different hierarchical levels of the machine, except for the HFSM with stack memory.

This thesis tackles the synthesis of FSMs from hierarchical specifications and proposes two HFSMs and a parallel hierarchical FSM (PHFSM) with stack memory that can provide such facilities as flexibility, extensibility and reusability. It also presents the synthesis methodology from hierarchical specifications to the generation of state transition tables that can be used to carry out the logic synthesis of the proposed HFSM models.

Considering that the use of formal state-based models that provide hierarchical and concurrent constructions is highly recommended for specifying complex control units, hierarchical graph-schemes (HGS) and parallel hierarchical graph-schemes (PHGS) are used and some considerations about their execution and correctness are presented. It is also explained how HGSs can be used to specify a control algorithm and how it is possible to verify automatically its correctness and to validate the intended functionality through simulation.

Using the first model of a HFSM with stack memory as a starting model, two new models that can provide flexibility, extensibility and reusability and a PHFSM model that combines hierarchy and pseudo-parallel execution of operations are proposed. Their functionality, flexibility, extensibility, synchronisation and internal realisation are fully explained.

To implement a control unit specified with a set of HGSs/PHGSs it is necessary to perform the first step of the sequential logic synthesis, taking in consideration the pretended target model. The manual synthesis methodology required to build the state transition table of a HFSM/PHFSM starting from a hierarchical specification based on HGSs/PHGSs is explained for a Moore, a Mealy and a mixed Moore/Mealy FSM. A tool that automatically performs this first step for the two HFSM models proposed is also presented.

In order to validate the proposed HFSM/PHFSM models and their synthesis, the models were described in VHDL for a LUT-based implementation and simulated using the Synopsys simulation tools.

#### Resumo

As máquinas finitas de estados (FSM) têm sido usadas para especificar e implementar unidades de controlo e têm sido um assunto de grande importância nas últimas cinco décadas. Devido ao aumento da complexidade das unidades de controlo e uma vez que o modelo FSM não permite descrições hierárquicas e concorrentes, novos modelos formais que suportam hierarquia e concorrência têm sido propostos com o objectivo de ultrapassar as limitações do modelo FSM e que permitem a especificação de unidades de controlo complexas usando uma metodologia de decomposição hierarquizada. Apesar disso não têm sido propostas arquitecturas de máquinas finitas de estados hierárquicas, com excepção das máquinas construídas com memória *stack*, que possam ser vistas como uma máquina integral que implementa internamente e de forma eficiente a transição entre os diferentes níveis hierárquicos da máquina.

Esta tese aborda a síntese de máquinas de estados especificadas hierarquicamente e propõe duas arquitecturas de máquinas hierárquicas (HFSM) e uma máquina paralela hierárquica (PHFSM) contruídas com memória *stack*, que são flexíveis, extensíveis e reutilizáveis. Apresenta também, a metodologia de síntese lógica que permite construir a tabela de transição de estados a partir da especificação hierárquica, tabela essa que é utilizada na implementação dos modelos propostos.

Considerando que é altamente recomendável a utilização de modelos formais que permitam descrições hierárquicas e concorrentes na especificação de unidades de controlo complexas, os modelos de grafos hierárquicos (HGS) e grafos paralelos hierárquicos (PHGS) são apresentados e são feitas algumas considerações acerca da sua utilização, execução e correcção. É ainda explicado como se pode validar a especificação hierárquica da funcionalidade de unidades de controlo complexas através da verificação automática e simulação da especificação baseada em HGSs.

Os modelos propostos de máquinas de estados são apresentados detalhadamente tendo em atenção o seu funcionamento, implementação interna baseada em memórias e sincronização, bem como as novas facilidades de flexibilidade e extensibilidade que estes modelos apresentam.

É apresentada a metodologia manual da síntese lógica que é necessário implementar a partir das especificações hierárquicas baseadas em HGSs ou PHGSs de forma a construir a tabela de transição de estados que especifica a máquina hierárquica ou paralela hierárquica, para as máquinas de estados de Moore, Mealy ou mista Moore/Mealy. É também apresentado um programa que implementa automaticamente a síntese lógica dos dois modelos de máquinas de estados hierárquicas propostos a partir da especificação feita com HGSs.

Os modelos de arquitecturas propostas, bem como a metodologia de síntese, foram validadas através de uma simulação em VHDL que foi feita usando as ferramentas de simulação da Synopsys.

# **CONTENTS**

| 1 | INT                        | RODUCTION                                            | 1           |

|---|----------------------------|------------------------------------------------------|-------------|

|   | 1.1                        | Outline of the Evolution of the Finite State Machine | 2           |

|   | 1.2                        | Control Units Overview                               | 5           |

|   |                            | 1.2.1 Introduction                                   | 5<br>5<br>7 |

|   |                            | 1.2.2 Specification of Control Units                 | 7           |

|   |                            | 1.2.3 Implementation of Control Units                | 8           |

|   |                            | 1.2.4 Synthesis of Control Units                     | 9           |

|   | 1.3                        | Objectives of the Work                               | 12          |

|   | 1.4                        | Organisation of the Thesis                           | 13          |

| 2 | SPE                        | CIFICATION OF CONTROL UNITS                          | 15          |

|   | 2.1                        | Introduction                                         | 16          |

|   | 2.2                        | Specification Requirements                           | 16          |

|   |                            | 2.2.1 State transitions                              | 16          |

|   |                            | 2.2.2 Concurrency                                    | 16          |

|   |                            | 2.2.3 Hierarchy                                      | 16          |

|   |                            | 2.2.4 Non-determinism                                | 17          |

|   |                            | 2.2.5 Behavioural Completion                         | 17          |

|   |                            | 2.2.6 Programming Constructs                         | 18          |

|   |                            | 2.2.7 Communication                                  | 18          |

|   |                            | 2.2.8 Synchronisation                                | 18          |

|   |                            | 2.2.9 Exceptions                                     | 19          |

|   |                            | 2.2.10 Timing                                        | 19          |

|   | 2.3                        | Specification models                                 | 19          |

|   |                            | 2.3.1 Introduction                                   | 19          |

|   |                            | 2.3.2 Finite State Machine model                     | 20          |

|   |                            | 2.3.3 Algorithmic State Machine model                | 21          |

|   |                            | 2.3.4 Graph-Scheme of Algorithm model                | 23          |

|   |                            | 2.3.5 Petri net model                                | 24          |

|   |                            | 2.3.6 Statecharts model                              | 26          |

|   | 2.4                        | Specification languages                              | 29          |

|   |                            | 2.4.1 Introduction                                   | 29          |

|   |                            | 2.4.2 VHDL                                           | 29          |

|   | 2.5                        | Conclusions                                          | 31          |

| 3 | HIERARCHICAL GRAPH-SCHEMES |                                                      |             |

|   | 3.1                        | Graph-Schemes of Algorithms                          | 34          |

|   | 3.2                        | Execution of a GS                                    | 35          |

|   |                            | 3.2.1 GS Traverse Procedure                          | 35          |

|   |                            | 3.2.2 Paths in GS                                    | 37          |

|   |                            | 3.2.3 Matrix Scheme of Algorithm                     | 38          |

|   | 3.3  | Graph-Schemes of Algorithms and Finite State Machines            | 39           |

|---|------|------------------------------------------------------------------|--------------|

|   |      | 3.3.1 Synthesis of a Moore Finite State Machine                  | 39           |

|   |      | 3.3.2 Synthesis of a Mealy Finite State Machine                  | 41           |

|   | 3.4  | Hierarchical Graph-Schemes                                       | 43           |

|   | 3.5  | Parallel Hierarchical Graph-Schemes                              | 45           |

|   | 3.6  | Execution and synchronisation of a HGS/PHGS                      | 46           |

|   | 3.7  | Correctness of a HGS/PHGS and Problems with Recursive Calls      | 46           |

|   | 3.8  | An Example                                                       | 48           |

|   | 3.9  | C++ Simulation of Hierarchical Graph-Schemes                     | 51           |

|   |      | 3.9.1 Introduction                                               | 51           |

|   |      | 3.9.2 Description of the Class System                            | 51           |

|   |      | 3.9.3 Acquisition and Construction of a Hierarchical Algorithm   | 53           |

|   |      | 3.9.4 Checking a Hierarchical Algorithm                          | 56           |

|   |      | 3.9.5 Running a Hierarchical Algorithm                           | 57           |

|   | 3.10 | ) Conclusions                                                    | 58           |

| 4 | TTrr | EDADOMICAL EDATE CHATE MACHINES                                  | 50           |

| 4 |      | ERARCHICAL FINITE STATE MACHINES Introduction                    | <b>59</b> 60 |

|   |      |                                                                  | 61           |

|   |      | FSM with Stack Memory (managing hierarchy) Parallel HFSM         | 67           |

|   |      | Virtual HFSM                                                     | 69           |

|   |      |                                                                  | 71           |

|   | 4.3  | HFSM/PHFSM Synchronisation 4.5.1 Synchronisation of a Moore HFSM | 71           |

|   |      | 4.5.2 Synchronisation of a Mealy HFSM                            | 73           |

|   |      | 4.5.3 Synchronisation of a PFSM                                  | 73<br>74     |

|   |      | 4.5.4 Synchronisation of a PHFSM                                 | 74           |

|   | 4.6  | Application Field                                                | 76           |

|   |      | Conclusions                                                      | 70<br>77     |

|   | 4./  | Conclusions                                                      | 1 1          |

| 5 | Syn  | NTHESIS OF HIERARCHICAL FINITE STATE MACHINES                    | 79           |

|   | 5.1  | Introduction                                                     | 80           |

|   | 5.2  | Synthesis of a Moore HFSM                                        | 80           |

|   | 5.3  | Synthesis of a Mealy HFSM                                        | 87           |

|   | 5.4  | Synthesis of a Mixed Moore/Mealy HFSM                            | 92           |

|   | 5.5  | Synthesis of a PFSM                                              | 94           |

|   | 5.6  | Synthesis of a PHFSM                                             | 98           |

|   | 5.7  | Automatic Synthesis of a HFSM                                    | 103          |

|   |      | 5.7.1 Marking a Hierarchical Algorithm                           | 103          |

|   |      | 5.7.1.1 Marking for synthesis as a Moore HFSM                    | 104          |

|   |      | 5.7.1.2 Marking for synthesis as a Mealy HFSM                    | 105          |

|   |      | 5.7.2 Constructing a State Transition Table                      | 105          |

|   |      | 5.7.2.1 Constructing a Moore State Transition Table              | 106          |

|   |      | 5.7.2.2 Constructing a Mealy State Transition Table              | 109          |

|   |      | 5.7.3 Constructing a Code Converter Programming Table            | 112          |

|   | 5.8  | Conclusions                                                      | 114          |

CONTENTS

| 6  | IMPLEMENTATION AND OPTIMISATION OF HIERARCHICAL         |     |  |

|----|---------------------------------------------------------|-----|--|

|    | STATE MACHINES                                          | 115 |  |

|    | 6.1 Introduction                                        | 116 |  |

|    | 6.2 Decomposition of the Combinational Scheme           | 117 |  |

|    | 6.2.1 Hierarchical FSM                                  | 117 |  |

|    | 6.2.2 Parallel FSM/HFSM                                 | 119 |  |

|    | 6.3 Replacement of Input Variables                      | 120 |  |

|    | 6.4 State Encoding                                      | 121 |  |

|    | 6.5 State Splitting                                     | 123 |  |

|    | 6.6 State Splitting in the Tool SIMULHGS                | 125 |  |

|    | 6.7 Quantification of the Optimisation Techniques       | 125 |  |

|    | 6.8 Conclusions                                         | 126 |  |

| 7  | 7 VHDL SIMULATION OF HIERARCHICAL FINITE STATE MACHINES |     |  |

|    | 7.1 Introduction                                        | 128 |  |

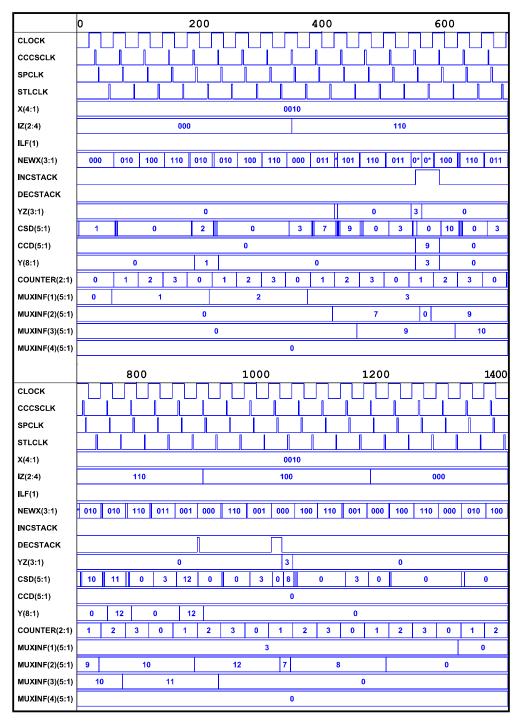

|    | 7.2 Simulation of a Moore HFSM model 2                  | 129 |  |

|    | 7.3 Simulation of a Mealy HFSM model 2                  | 132 |  |

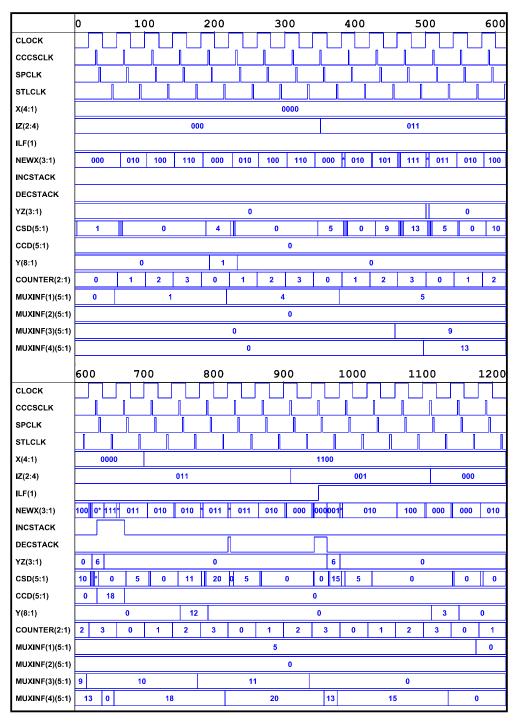

|    | 7.4 Simulation of a Moore HFSM model 3                  | 133 |  |

|    | 7.5 Simulation of a Mealy HFSM model 3                  | 135 |  |

|    | 7.6 Simulation of a Moore PFSM                          | 136 |  |

|    | 7.7 Simulation of a Moore PHFSM                         | 138 |  |

|    | 7.8 Providing Flexibility                               | 142 |  |

|    | 7.9 Providing Extensibility                             | 147 |  |

|    | 7.10 Providing Reusability                              | 151 |  |

|    | 7.11 Using Pure Virtual HGSs                            | 151 |  |

|    | 7.12 Hierarchical FSMs versus Non-Hierarchical FSMs     | 151 |  |

|    | 7.13 Conclusions                                        | 154 |  |

| 8  | FINAL CONCLUSIONS AND FUTURE WORK                       | 155 |  |

|    | 8.1 Introduction                                        | 156 |  |

|    | 8.2 Contributions                                       | 157 |  |

|    | 8.2.1 HFSM and PHFSM models                             | 157 |  |

|    | 8.2.2 Synthesis of HFSMs                                | 157 |  |

|    | 8.2.3 Experimental Results                              | 158 |  |

|    | 8.3 Future Work                                         | 158 |  |

| 9  | APPENDIX A - LUTS                                       | 159 |  |

| 10 | APPENDIX B - SIMULHGS                                   | 169 |  |

| 11 | REFERENCES                                              | 197 |  |

| 12 | 12 GLOSSARY                                             |     |  |

# LIST OF FIGURES

| Chapter 1   |                                                                |      |

|-------------|----------------------------------------------------------------|------|

| Figure 1.1  | General form of a Turing machine.                              | 2    |

| Figure 1.2  | Embedded system block diagram.                                 | 6    |

| Figure 1.3  | (a) Control unit model. (b) Control unit with decoder.         |      |

|             | (c) Control unit with counter. (d) Control unit with stack.    | 8    |

| Figure 1.4  | Automatic synthesis of digital circuits.                       | 11   |

| Chapter 2   |                                                                |      |

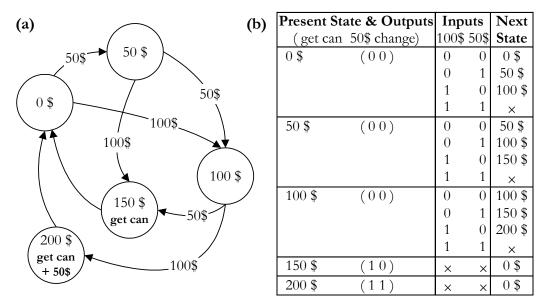

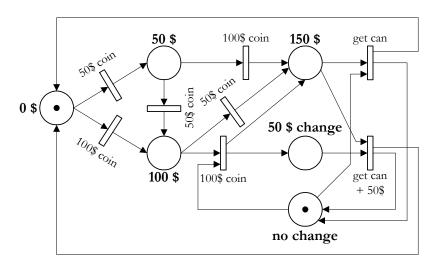

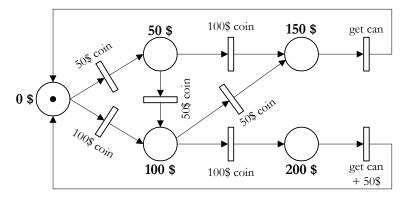

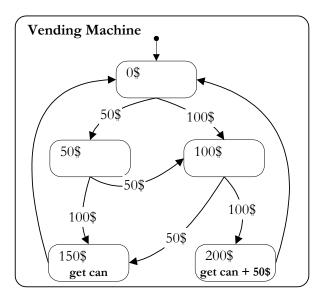

| Figure 2.1  | (a) Vending machine state diagram.                             |      |

|             | (b) Vending machine state transition table.                    | 21   |

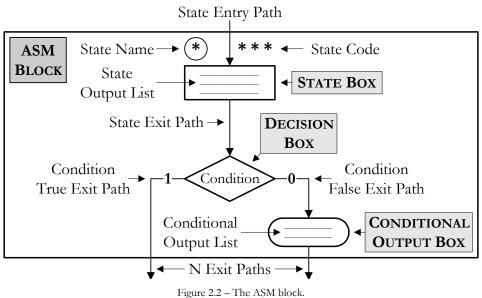

| Figure 2.2  | The ASM block.                                                 | 22   |

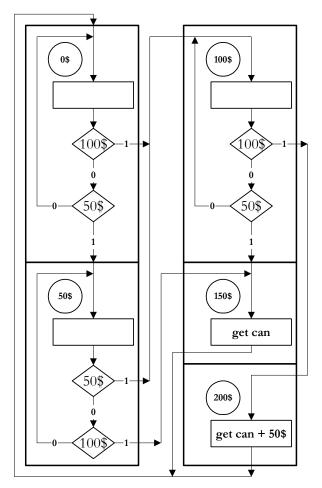

| _           | Vending machine ASM chart.                                     | 23   |

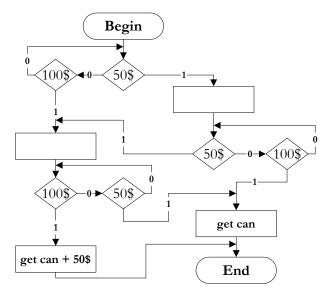

|             | Vending machine GS description.                                | 24   |

|             | Vending machine Petri net.                                     | 25   |

| Figure 2.6  | State machine equivalent to the previous Petri net.            | 26   |

| Figure 2.7  | A Statechart example.                                          | 28   |

| Figure 2.8  | Vending machine Statechart.                                    | 28   |

| Figure 2.9  | Vending machine VHDL behavioural description.                  | 32   |

| Chapter 3   |                                                                |      |

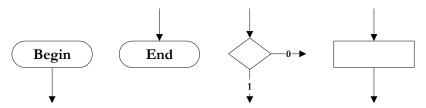

| Figure 3.1  | Nodes of GS.                                                   | 34   |

| Figure 3.2  | An example of a GS.                                            | 35   |

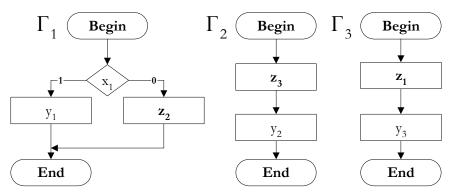

| Figure 3.3  | GS marked for Moore synthesis.                                 | 39   |

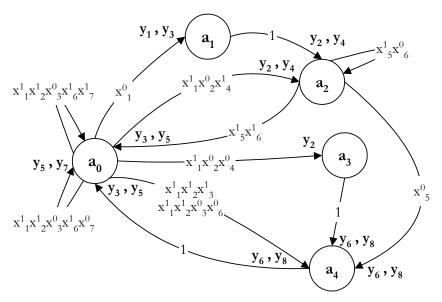

| _           | State diagram of the Moore FSM.                                | 40   |

|             | GS marked for Mealy synthesis.                                 | 41   |

| Figure 3.6  | State diagram of the Mealy FSM.                                | 42   |

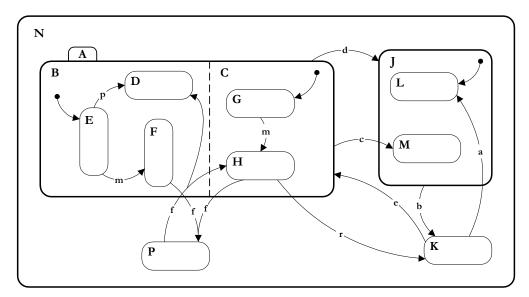

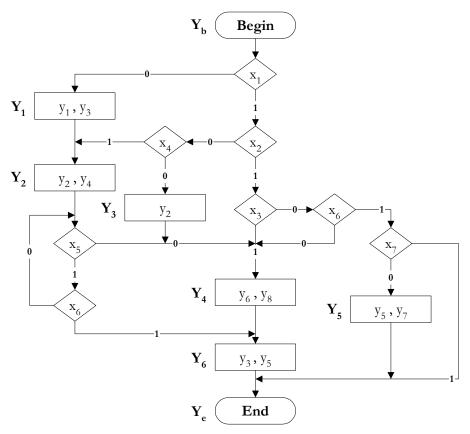

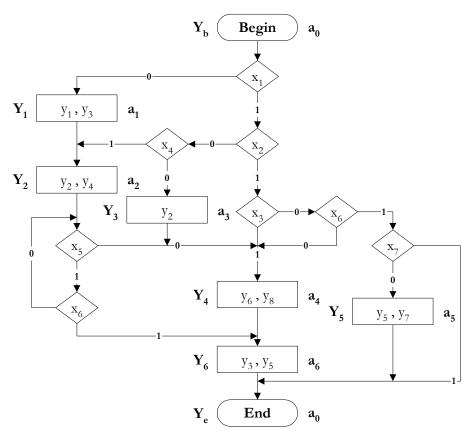

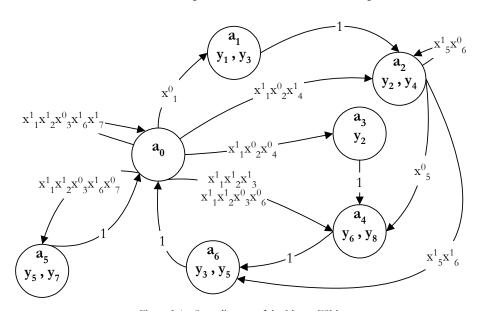

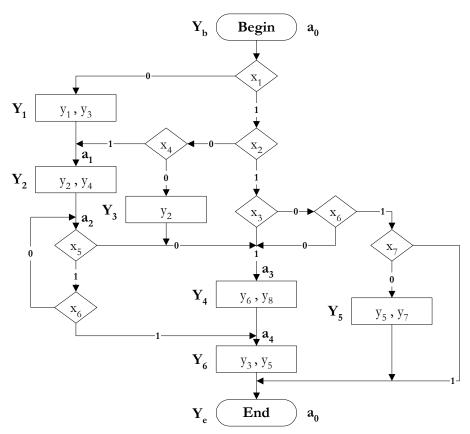

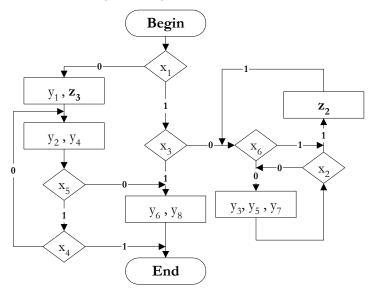

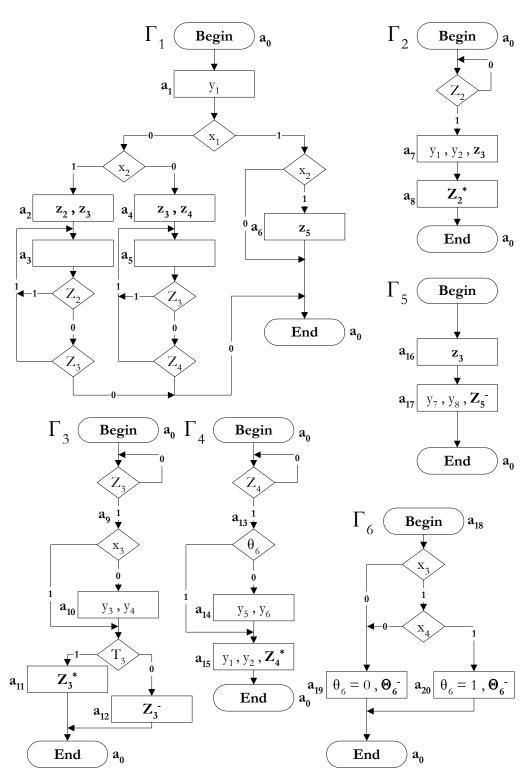

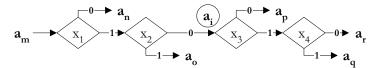

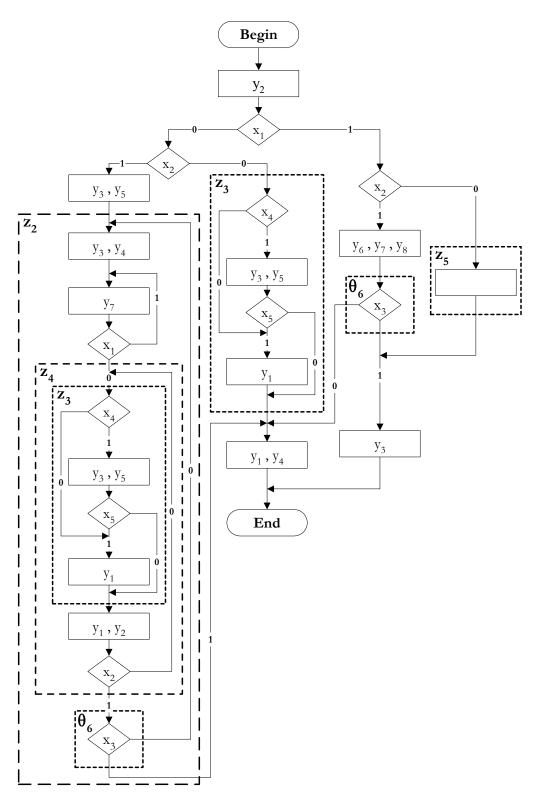

| Figure 3.7  | An algorithm described by hierarchical graph-schemes.          | 44   |

| Figure 3.8  | An algorithm described by parallel hierarchical graph-schemes. | . 45 |

| Figure 3.9  | An example of a HGS with an infinite cycle.                    | 46   |

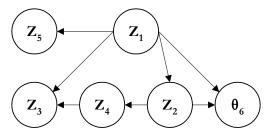

| Figure 3.10 | Special graph to detect infinite recursion.                    | 47   |

| Figure 3.11 | Macrooperation looping without infinite recursion.             | 47   |

| Figure 3.12 | Binary multiplication algorithm.                               | 48   |

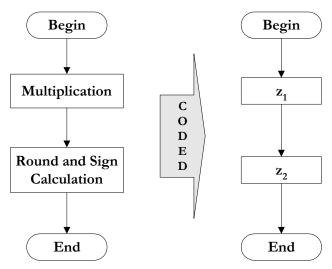

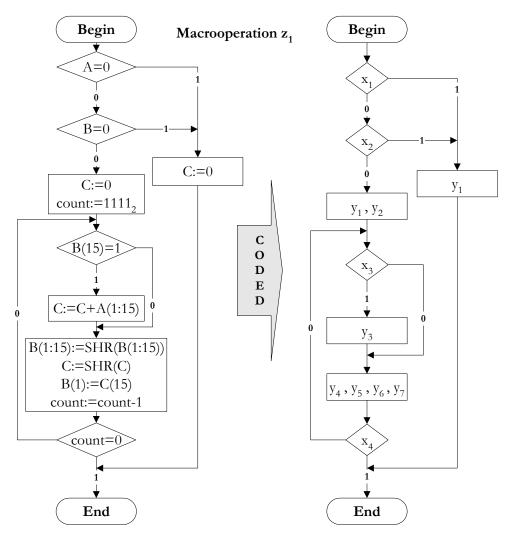

| Figure 3.13 | Macrooperation $z_1$ implementation and codification.          | 49   |

| Figure 3.14 | Macrooperation $z_2$ implementation and codification.          | 49   |

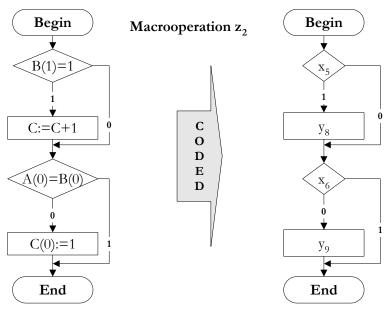

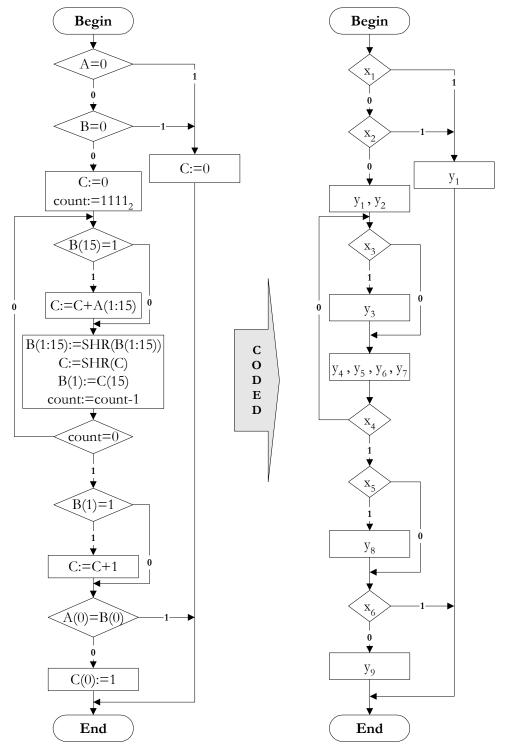

| Figure 3.15 | Non-hierarchical implementation and codification of the l      | •    |

|             | multiplication algorithm.                                      | 50   |

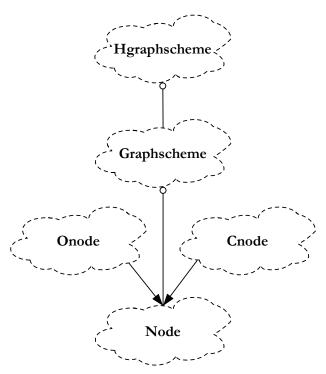

| _           | Class system diagram of the tool SIMULHGS.                     | 53   |

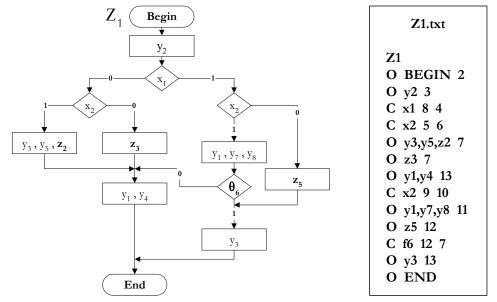

| Figure 3.17 | Macrooperation $Z_1$ and its text description.                 | 54   |

| Figure 3.18 | Logic function $\Theta_c$ and its text description             | 54   |

| Chapter 4    |                                                                                 |          |

|--------------|---------------------------------------------------------------------------------|----------|

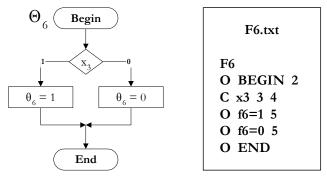

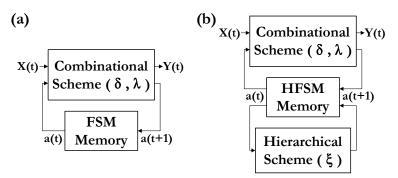

| Figure 4.1   | (a) FSM block diagram. (b) HFSM block diagram.                                  | 60       |

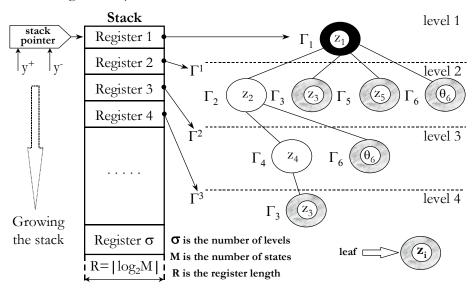

| Figure 4.2   | Graph G <sub>h</sub> showing hierarchical levels.                               | 61       |

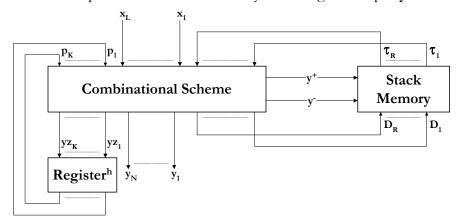

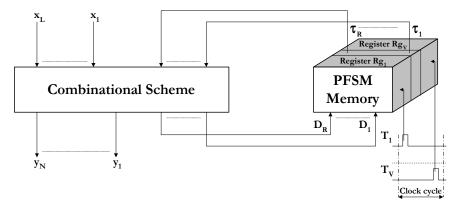

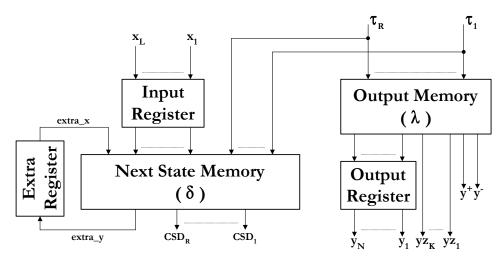

| Figure 4.3   | Hierarchical finite state machine structure (model 1).                          | 62       |

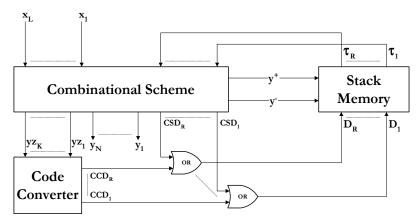

| Figure 4.4   | Hierarchical finite state machine structure (model 2).                          | 63       |

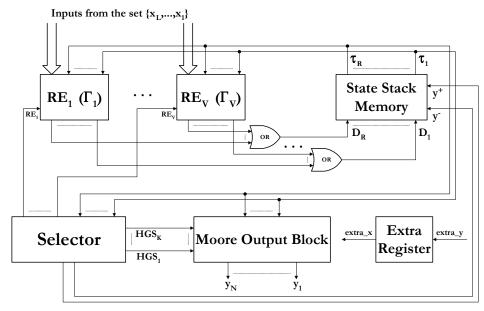

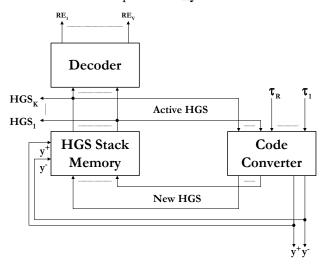

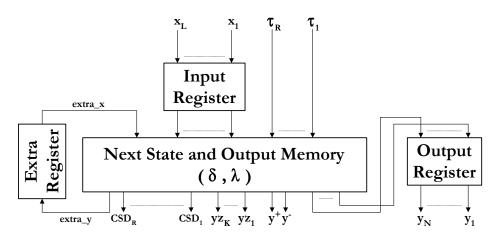

| _            | Hierarchical finite state machine structure (model 3).                          | 64       |

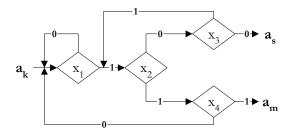

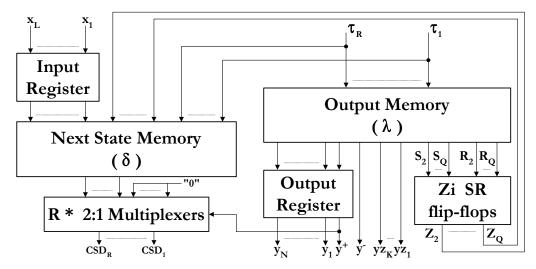

| _            | Selector implementation.                                                        | 65       |

| Figure 4.7   | *                                                                               | 67       |

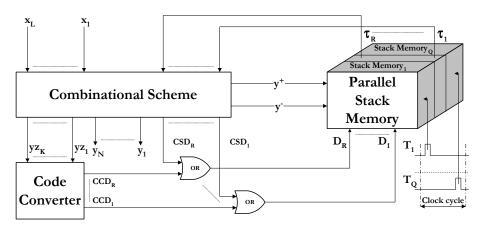

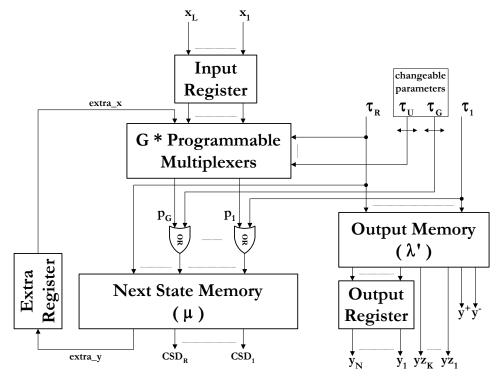

| 0            | Model of a pseudo-parallel hierarchical finite state machine.                   | 68       |

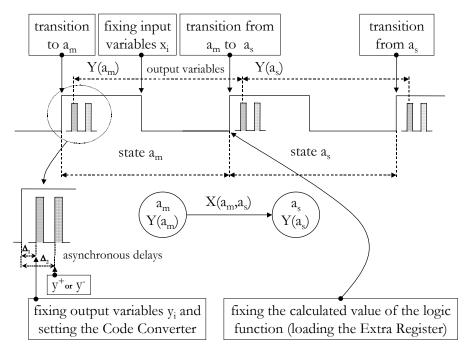

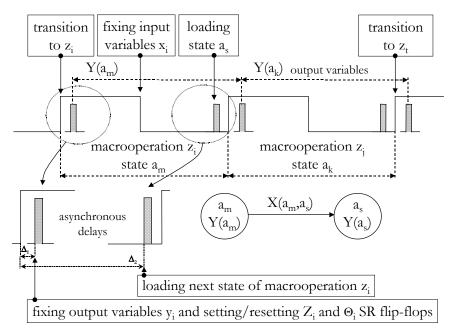

| -            | Synchronisation of a Moore HFSM model 2.                                        | 71       |

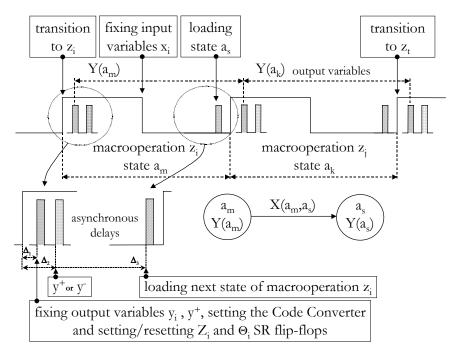

| 0            | Synchronisation of a Mealy HFSM model 2.                                        | 73       |

| 0            | Synchronisation of a Moore PFSM.                                                | 74       |

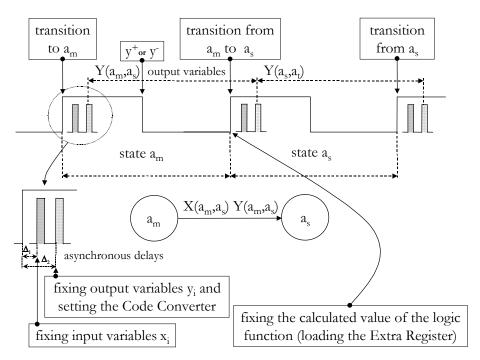

| _            | 2 Synchronisation of a Moore PHFSM.                                             | 75       |

| Ü            | of a moore in the six                                                           | 7.5      |

| Chapter 5    |                                                                                 |          |

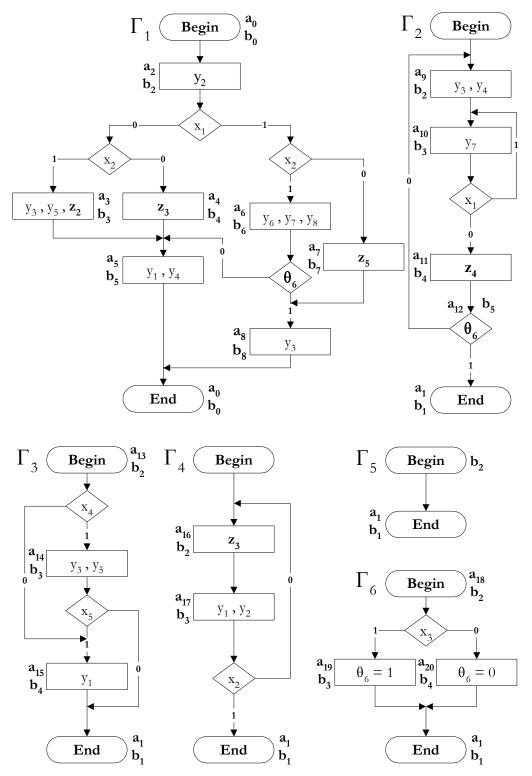

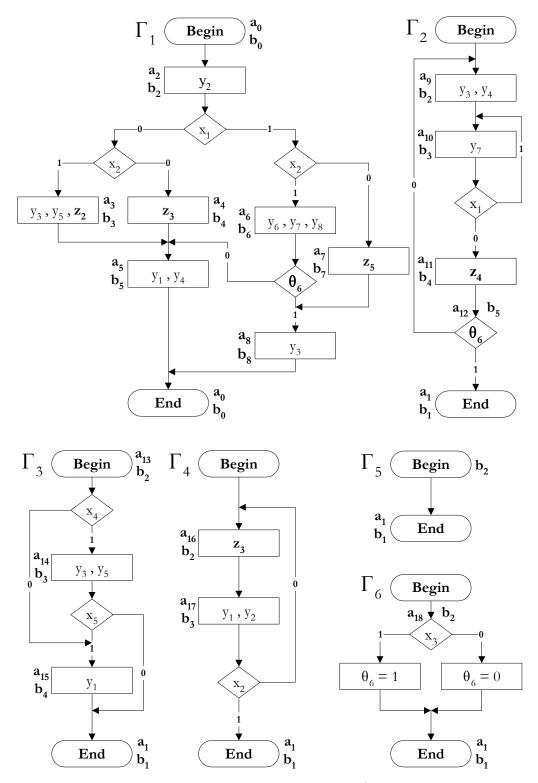

| Figure 5.1   | A set of HGSs marked for synthesis as a Moore machine (s                        |          |

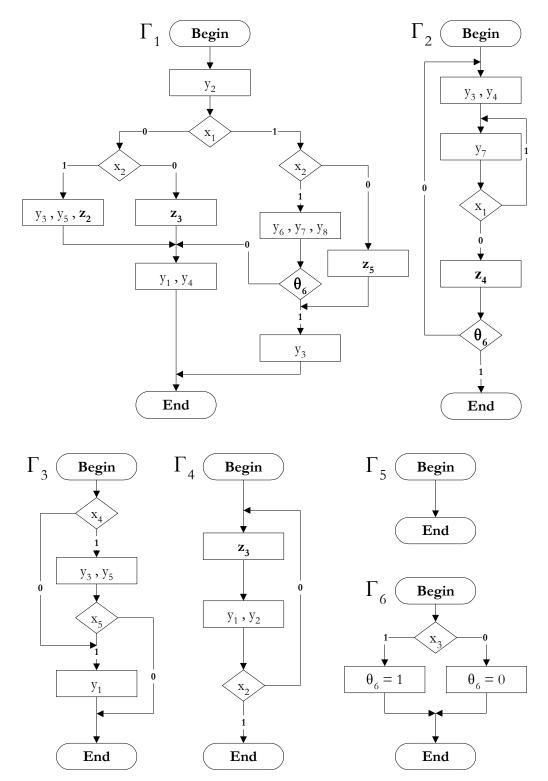

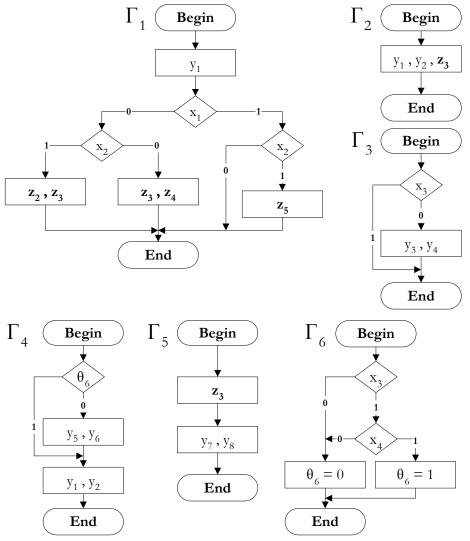

|              | for model 2, states b <sub>i</sub> for model 3).                                | 82       |

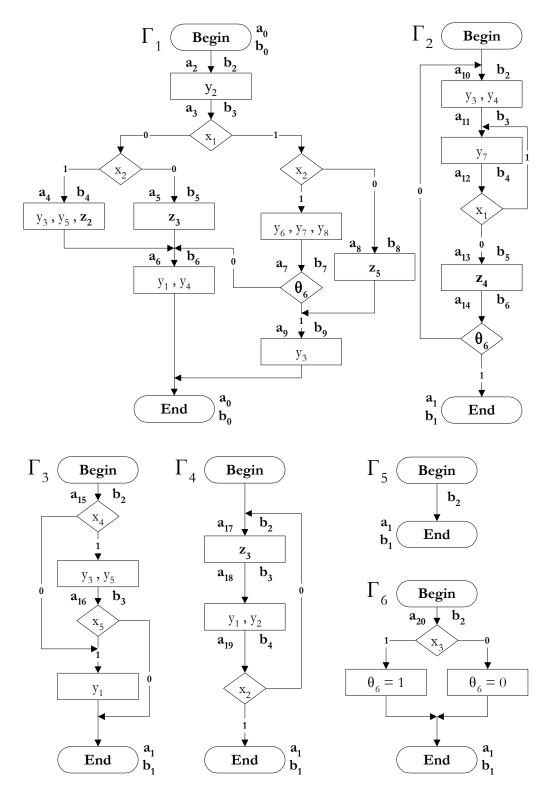

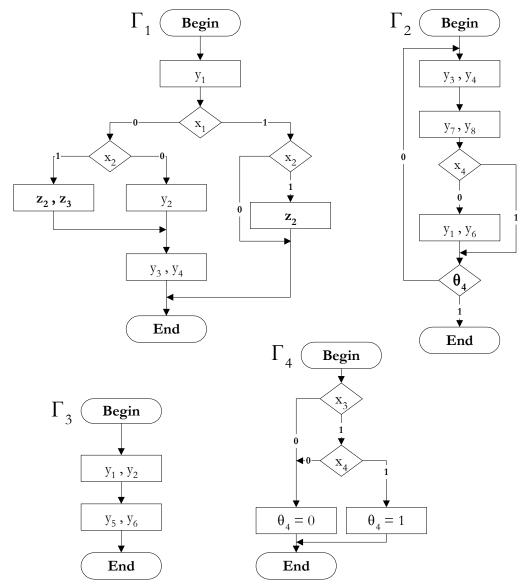

| Figure 5.2   | A set of HGSs marked for synthesis as a Mealy machine (s                        |          |

|              | for model 2, states b <sub>i</sub> for model 3).                                | 88       |

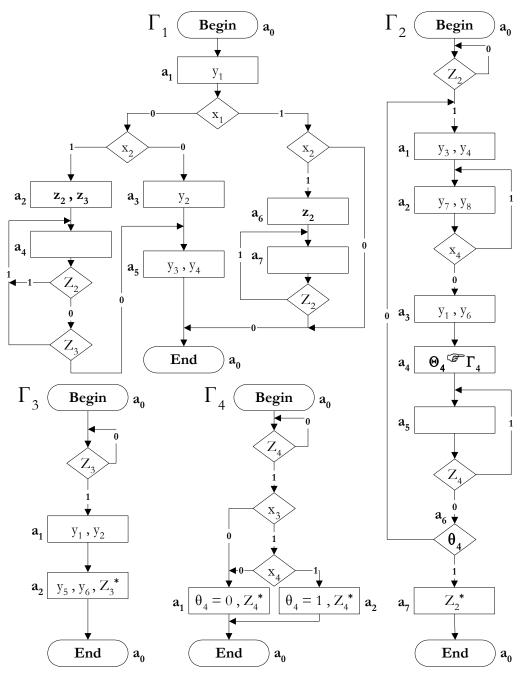

| Figure 5.3   | A set of HGSs marked for synthesis as a mixed Moore                             | /Mealy   |

|              | machine (states a <sub>i</sub> for model 2, states b <sub>i</sub> for model 3). | 93       |

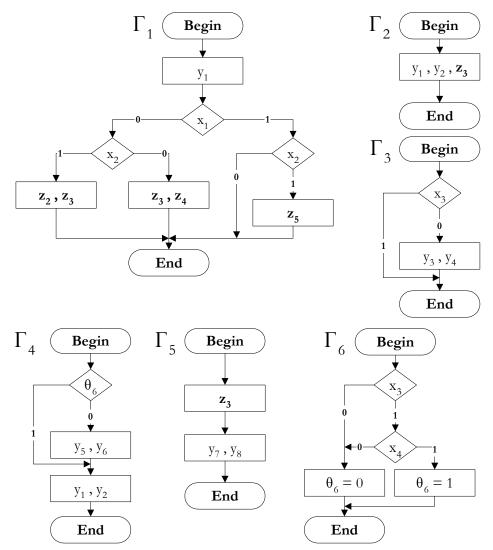

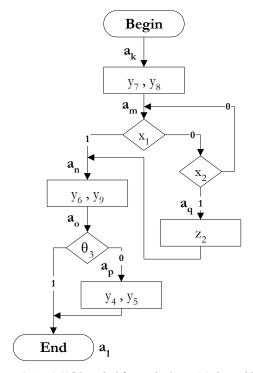

| Figure 5.4   | A set of PHGSs for implementing in a PFSM.                                      | 95       |

| Figure 5.5   | A set of extended PHGSs marked for synthesis as a Moore                         | PFSM.    |

|              |                                                                                 | 96       |

| Figure 5.6   | A set of PHGSs for implementing in a PHFSM.                                     | 99       |

| Figure 5.7   | A set of extended PHGSs marked for synthesis as a                               | Moore    |

| Ü            | PHFSM.                                                                          | 100      |

| Figure 5.8   | A cycle of conditional nodes.                                                   | 106      |

| 0            | State transition table generated by SIMULHGS for the                            | mixed    |

| S            | Moore/Mealy HFSM model 2.                                                       | 108      |

| Figure 5.10  | RE1 state transition table generated by SIMULHGS for the                        | mixed    |

| 0            | Moore/Mealy HFSM model 3.                                                       | 109      |

| Figure 5.11  | A HGS marked for synthesis as a Mealy machine.                                  | 110      |

|              | State transition table generated by SIMULHGS for the                            |          |

| 0            | HFSM model 2.                                                                   | 111      |

| Figure 5.13  | 3 Code Converter table generated by SIMULHGS for the                            |          |

| 1 18010 0110 | Moore/Mealy HFSM model 2.                                                       | 112      |

| Figure 5.14  | Code Converter table generated by SIMULHGS for the                              |          |

| riguic 5.1   | HFSM model 3.                                                                   | 113      |

|              | TH OM Model 3.                                                                  | 113      |

| Chapter 6    |                                                                                 |          |

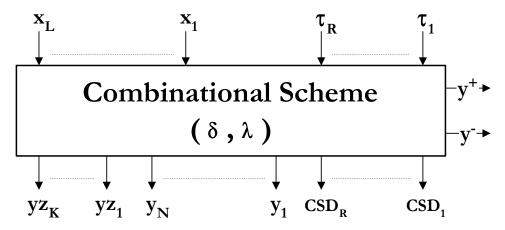

| 0            | Combinational Scheme.                                                           | 117      |

| Figure 6.2   | Decomposition of the Moore HFSM Combinational Scheme                            | e for a  |

|              | RAM-based implementation.                                                       | 118      |

| Figure 6.3   | Decomposition of the Mealy HFSM Combinational Schem                             | e for a  |

| -            | RAM-based implementation.                                                       | 118      |

| Figure 6.4   | Decomposition of the Moore PHFSM Combinational Schen                            | ne for a |

| -            | RAM-based implementation.                                                       | 119      |

LIST OF FIGURES VII

| Figure 6.5  | Karnaugh map for the special state encoding algorithm. 12         | 22 |

|-------------|-------------------------------------------------------------------|----|

| Figure 6.6  | Decomposition of the Moore HFSM combinational scheme using        | ng |

|             | the replacement of input variables and the special state encoding | ıg |

|             | algorithm. 12                                                     | _  |

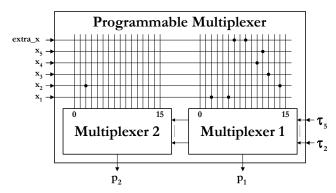

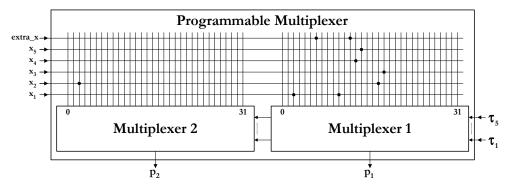

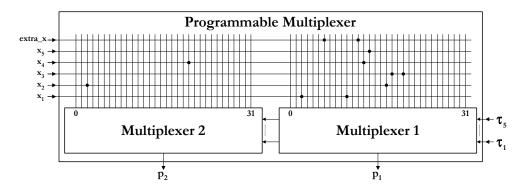

| Figure 6.7  | Programmable multiplexer. 12                                      | 23 |

| 0           | Applying the state splitting technique. 12                        | 24 |

|             |                                                                   |    |

| napter 7    | D                                                                 | VТ |

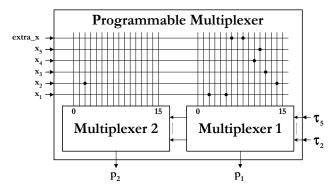

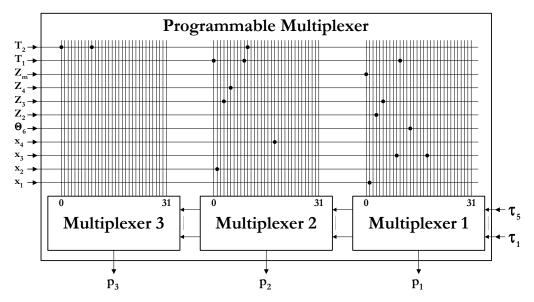

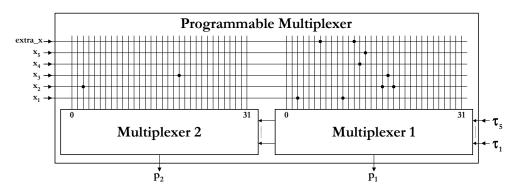

| Figure 7.1  | Programmable multiplexer for the mixed Moore/Mealy HFSI           |    |

| Б. 7.0      | model 2 with binary state encoding.                               |    |

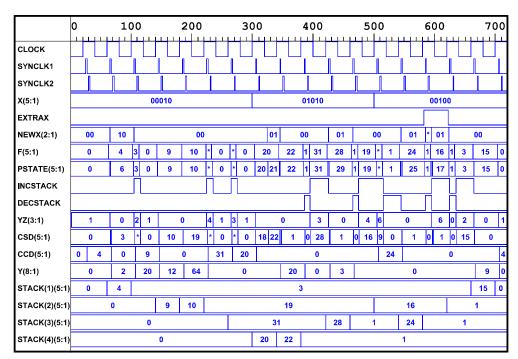

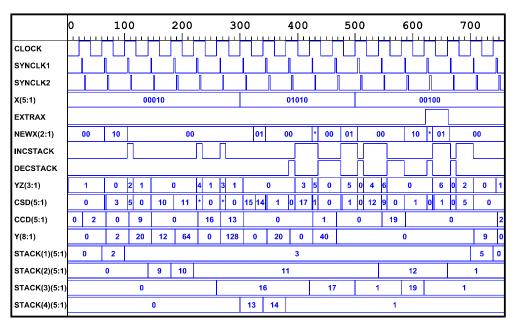

| Figure /.2  | Waveform of the mixed Moore/Mealy HFSM model 2 with binar         | -  |

| Б. 7.0      | state encoding. 13                                                |    |

| Figure 7.3  | Programmable multiplexer for the mixed Moore/Mealy HFSI           |    |

|             | model 2 with special state encoding.                              |    |

| Figure 7.4  | Waveform of the mixed Moore/Mealy HFSM model 2 for the            |    |

|             | special state encoding. 13                                        |    |

| Figure 7.5  | Programmable multiplexer for the Mealy HFSM model 2 with          |    |

|             | binary state encoding. 13                                         |    |

| Figure 7.6  | Waveform of the Mealy HFSM model 2 with the binary star           |    |

|             | encoding. 13                                                      | 3  |

| 0           | Waveform of the mixed Moore/Mealy HFSM model 3. 13                |    |

| Figure 7.8  | Waveform of the Mealy HFSM model 3.                               |    |

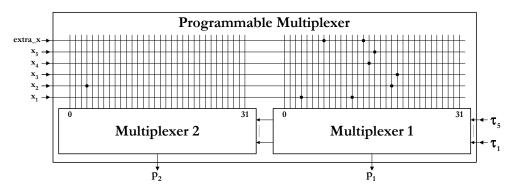

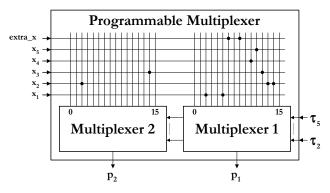

| Figure 7.9  | Programmable multiplexer for the Moore PFSM. 13                   | 57 |

| Figure 7.10 | Waveform of the Moore PFSM.                                       | 8  |

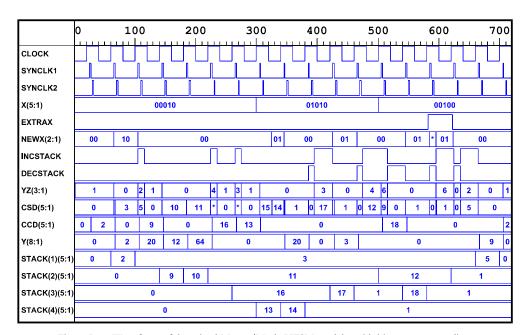

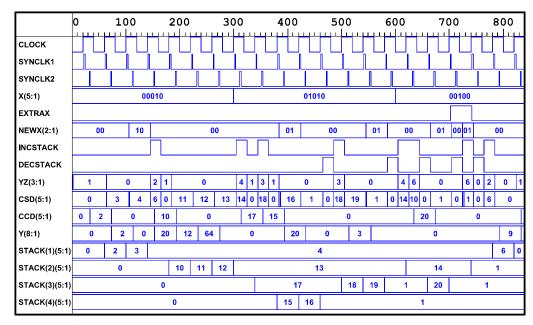

| Figure 7.11 | Programmable multiplexer for the Moore PHFSM. 13                  | 9  |

| Figure 7.12 | First waveform of the Moore PHFSM.                                | -0 |

| Figure 7.13 | Second waveform of the Moore PHFSM.                               | -1 |

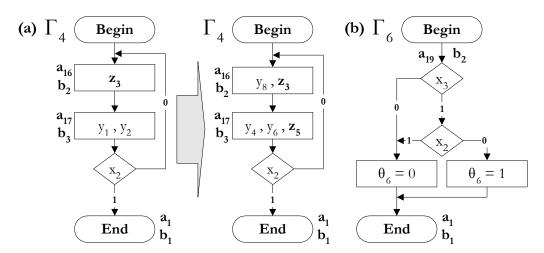

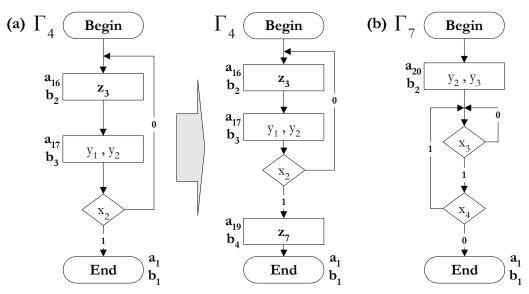

| Figure 7.14 | (a) New implementation of the macrooperation z <sub>4</sub> .     |    |

|             | (b) New version of the logic function $\theta_6$ .                | -2 |

| Figure 7.15 | New implementation of the programmable multiplexer for the        | ne |

|             | mixed Moore/Mealy HFSM model 2 with binary state encoding in      |    |

|             | order to provide flexibility.                                     | -3 |

| Figure 7.16 | Waveform of the mixed Moore/Mealy HFSM model 2 with the           | ne |

|             | changes that provide flexibility.                                 | 4  |

| Figure 7.17 | Karnaugh map for state encoding.                                  | -5 |

| Figure 7.18 | New implementation of the programmable multiplexer for the        | ne |

|             | mixed Moore/Mealy HFSM model 2 with special state encoding in     | in |

|             | order to provide flexibility.                                     |    |

| Figure 7.19 | (a) New implementation of the macrooperation z <sub>4</sub> .     |    |

| C           | (b) New macrooperation z <sub>7</sub> .                           | -7 |

| Figure 7.20 | New implementation of the programmable multiplexer for the        | ne |

| O           | mixed Moore/Mealy HFSM model 2 with binary state encoding in      |    |

|             | order to provide extensibility.                                   |    |

| Figure 7.21 | Waveform of the mixed Moore/Mealy HFSM model 2 with the           |    |

| U           | changes that provide extensibility.                               |    |

| Figure 7.22 | Ordinary GS equivalent to the set of HGSs presented in Figure 5.  |    |

| U           | 15                                                                |    |

# LIST OF TABLES

| Chapter 3  |                                                                                |                 |

|------------|--------------------------------------------------------------------------------|-----------------|

| Table 3.1  | Matrix scheme of algorithm.                                                    | 38              |

| Chapter 5  |                                                                                |                 |

| Table 5.1  | Moore extended state transition table.                                         | 84              |

| Table 5.2  | Moore ordinary state transition table.                                         | 84              |

| Table 5.3  | Moore model 2 Code Converter table.                                            | 85              |

| Table 5.4  | RE <sub>1</sub> Moore ordinary state transition table.                         | 86              |

| Table 5.5  | RE <sub>2</sub> Moore ordinary state transition table.                         | 86              |

| Table 5.6  | RE <sub>3</sub> Moore ordinary state transition table.                         | 86              |

| Table 5.7  | RE <sub>4</sub> Moore ordinary state transition table.                         | 86              |

| Table 5.8  | RE5 Moore ordinary state transition table.                                     | 86              |

| Table 5.9  | RE <sub>6</sub> Moore ordinary state transition table.                         | 86              |

| Table 5.10 | Moore model 3 Code Converter table.                                            | 86              |

| Table 5.11 | Mealy model 2 Code Converter table.                                            | 89              |

| Table 5.12 | Mealy extended state transition table.                                         | 90              |

| Table 5.13 | Mealy ordinary state transition table.                                         | 90              |

| Table 5.14 | RE <sub>1</sub> Mealy ordinary state transition table.                         | 91              |

| Table 5.15 | RE <sub>2</sub> Mealy ordinary state transition table.                         | 91              |

| Table 5.16 | RE <sub>3</sub> Mealy ordinary state transition table.                         | 91              |

| Table 5.17 | RE5 Mealy ordinary state transition table.                                     | 91              |

| Table 5.18 | RE <sub>4</sub> Mealy ordinary state transition table.                         | 91              |

| Table 5.19 | RE <sub>6</sub> Mealy ordinary state transition table.                         | 91              |

| Table 5.20 | Mealy model 3 Code Converter table.                                            | 91              |

| Table 5.21 | Mixed Moore/Mealy ordinary state transition table.                             | 92              |

| Table 5.22 | PFSM extended state transition table.                                          | 97              |

| Table 5.23 | PFSM ordinary state transition table.                                          | 97              |

| Table 5.24 | PHFSM extended state transition table.                                         | 102             |

| Table 5.25 | PHFSM ordinary state transition table.                                         | 102             |

| Table 5.26 | Moore PHFSM Code Converter table.                                              | 103             |

| Chapter 6  |                                                                                |                 |

| Table 6.1  | Ordinary state transition table with the replacement ovariables.               | of input<br>120 |

| Table 6.2  | State transition table without the extra state.                                | 124             |

| Table 6.3  | State transition table after inserting the extra state.                        | 124             |

| Chapter 7  |                                                                                |                 |

| Table 7.1  | Ordinary state transition table for the new version of t function $\theta_6$ . | the logic       |

| Table 7.2  | Ordinary state transition table for the new node                               |                 |

|            | macrooperation z <sub>4</sub> and the new macrooperation z <sub>7</sub> .      | 148             |

# 1 Introduction

# Summary

The goal of this thesis is the development of a methodology for the synthesis of reprogrammable control units from hierarchical specifications. The proposed methodology uses complex finite state machine models, i.e. hierarchical and parallel hierarchical finite state machines, that can provide such facilities as flexibility, extensibility and reusability and that can be easily reprogrammed.

This chapter starts by presenting an historical perspective of the evolution of the finite state machine model, starting from the Turing machine until the most recent proposals for hierarchical and parallel implementations of complex finite state machines.

Then it gives an overview of control units in particular those that can appear in embedded systems. Since control units are increasing in complexity their functionality should be specified in a top-down manner and therefore the advantages of such approach are explained. Control units can follow the finite state machine model but in order to simplify the implementation of complex control units several alternative architectures are presented. The automatic synthesis of digital circuits, with an emphasis on the sequential logic synthesis of control units, is also outlined.

Finally the objectives of the work and the structure of this thesis are presented.

#### 1.1 Outline of the Evolution of the Finite State Machine

Finite state machine (FSM) or finite automaton is a mathematical model of a system, with discrete inputs and outputs and a finite number of states. The state of the system summarises the information concerning past inputs that is needed to determine the behaviour of the system for future inputs. Associated with a finite machine is a direct graph called a state transition diagram, which is its graphical counterpart.

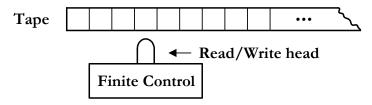

Alan Turing proposed the first model of a machine or automaton in 1936, even before the appearance of the first computers. Since Turing was a mathematician he was interested in defining the fundamental relationships involved in making computations [Booth67]. The basic model of a **Turing machine** (see Figure 1.1) is a finite control, an infinite input tape and a read/write head [Booth67, Kohavi70, AleHan75, HopUll79].

The machine head scans one cell of the tape at a time and it is allowed to read from or write on the cell directly under it and to move its position one cell at a time to the right or to the left. The tape, which represents the external information store, is divided into cells and each cell holds a blank symbol or one symbol from a finite set of symbols.

Figure 1.1 – General form of a Turing machine.

This machine can execute any process that is finitely described, consisting of discrete steps, each of which can be carried out mechanically and work as follows. During each cycle of operation the cell under the head is read to determine the symbol printed on the tape. After reading the symbol the control machine executes one of the four following possible moves: a new symbol can be written in the cell tape; the head is moved one position to the right of the current cell; the head is moved one position to the left of the current cell; the operation of the machine is halted.

Because the control element is a finite state machine, the actual operation performed will be influenced by the previous operations performed by the machine. The Turing machine can be considered a general-purpose machine and has been the base model of the finite automata.

Chapter 1: Introduction 3

However, a more attractive kind of machine is a Turing machine with multiple tapes, in particular the read-only machine. This kind of machine has an input tape, an output tape and a working tape and works as follows. The input tape can only move in a forward direction past its reading head, i.e. the machine can read the input tape but cannot write on the tape or recall past inputs. The output tape is similar to the input tape but it is initially blank and it can only be written when it passes through the printing head of the machine. The main tape of this machine is the working tape, which is both a read and a write tape on which all of the intermediate calculations are recorded and thus it represents the memory of the machine. Modified versions of Turing machines appear in [Booth67, HopUll79].

During the 1950s, several authors had proposed different types of read-only machines, being the two most know models the Moore and the Mealy machines. The former is due to the work of Huffman in 1954 and Moore in 1956, and the latter is due to the work of Mealy in 1955. In the **Moore machine** the symbol written in the output tape depends on the information stored in the working tape, while in the **Mealy machine** the symbol written in the output tape depends on the information stored in the working tape and on the symbol read from the input tape.

From the electronic point of view, a Moore (Mealy) machine is characterised by having a state register that holds its internal state, a next state logic function that generates the next state depending on the present state and on the inputs and an output logic function depending on the present state and in the case of Mealy depending also on the inputs. The formal definition of the FSM is presented in the Paragraph 2.3.2.

Oettinger in 1961 and Schutzenberger in 1963 conceptualised the **pushdown** automaton. The pushdown automaton is a second version of a read-only machine with a working tape that is restricted to be what is called a pushdown tape [Booth67, HopUll79]. This working tape can be written on, read from or moved in both directions, but as it moves from left to right past the reading head all the tape cells on the right are left blank [Booth67]. Such an arrangement is described as "last in first out" list. The pushdown automaton is also briefly presented in [AleHan75].

During the first half of the 1960s, Hartmanis and Stearns [HarSte66] and Kohavi [Kohavi70] have studied the **composition** and **decomposition** of finite state machines. There are three basic forms of machine composition/decomposition: **parallel, series** or **cascade** and **feedback** [Booth67, Kohavi70, Baranov79]. The decomposition of a FSM into several smaller interconnected FSMs is an alternative to a single monolithic implementation in order to deal with the complexity of a large machine.

The topic become less interesting during the 1970s due to the ROM-based implementation of machines, i.e. due to the use of microprogramming (concept first outlined by Wilkes in [Wilkes51]), but it had regained importance with the appearance of the first PLDs. Since they could not provide enough inputs or outputs or number of products to implement the next state and output functions of complex FSMs the realisation with a single PLD was not possible. Therefore, more recent authors [Bolton90, Baranov94, Katz94] have presented the decomposition of FSMs, with the introduction of idle states, in order to overcome the resource limitations of PLDs.

In order to deal with the increasing complexity of control units and since the state transition diagrams are not adequate to capture the notation of an algorithm, in 1973 Christopher R. Clare introduced the **algorithmic state machine** (ASM) in [Clare73]. The ASM looks like a program flowchart and it is an approach to move toward programming. Moreover, [Clare73] explores the use of ROMs in the synthesis of ASM-based designs, i.e. microprogramming. The ASM model, the synthesis of ASM-based designs and microprogramming are well documented in [WinPro80, Green86].

Clare also proposed the implementation of a finite state machine with several cooperating FSMs in [Clare73]. In other words FSMs can be linked in order to specify parallel algorithms. The linked FSMs can be completely independent or can communicate between them for synchronisation purposes and most commonly share the same clock. Linked FSMs are presented in [Clare73, Green86, Bolton90].

In 1974 Baranov proposed the **graph-scheme of algorithm**, which is very similar to the ASM, in [Baranov74]. In 1984 Sklyarov proposed an extension of the GS, the **hierarchical graph-scheme** (HGS) in [Sklyarov84]. The HGS adds support for hierarchical descriptions based on macro blocks, such as macrooperations and logic functions. This model is another step toward programming, in this case to procedural programming. The HGS can be used to describe the functionality of complex control units by decomposing them in a top-down manner, resembling an algorithmic decomposition using a structured programming language. The macrooperation can be seen as the hardware equivalent of the procedure in Pascal while the logic function as the hardware analogue of the function in Pascal.

For the hierarchical implementation once again the software model was imported and a hierarchical FSM with stack memory (HFSM), which is closely related with the pushdown automaton, was proposed in [Sklyarov84]. The stack memory controlled through push and pop instructions is used as the state register of the machine like it is used in a computer that executes a program specified with subprograms. Thus, when the execution of the machine must perform a macro block in a new hierarchical level, the stack keeps the present state unchanged and another register of the stack is used to hold the state during the execution of the macro block. When the macro block finishes executing the interrupted state of the

Chapter 1 : Introduction 5

previous hierarchical level is resumed. This HFSM can be seen as a procedural hardware implementation of a control unit.

In 1987, Sklyarov proposed an extension of the HGS, the **parallel hierarchical graph-scheme** (PHGS), which in addition to hierarchical descriptions also allows the parallel invocation of macrooperations, in [Sklyarov87]. This model can be seen as a set of FSMs that have their combinational schemes merged in a unique combinational scheme and with a state register composed of several state registers, one per machine, that are sequentially scanned by the FSM clock. The synchronisation of the parallel execution of the sub-FSMs is achieved through the introduction of waiting states. As a result a pseudo-**parallel FSM** (**PFSM**) that implements parallel tasks sequentially is achieved.

In 1987, Harel proposed the **Statechart** as an extension of the FSM state transition diagrams that allows hierarchical and concurrent descriptions in [Harel87]. And in 1989, he and Drusinsky proposed a hierarchical implementation based on a **tree of interconnected FSMs**, where each state at each level of the statechart hierarchy is represented by a machine implementing the FSM corresponding to its sub-states on the next immediate level, in [DruHar89].

In 1994, Micheli suggests representing a FSM diagram in a hierarchical way (hierarchical FSM) by splitting it into sub-diagrams, in [Micheli94]. Each sub-diagram, except the root has an entry and an exit state and it is associated with one or more calling states from other sub-diagrams. Each transition to a calling state is equivalent to a transition into the entry state of the corresponding sub-diagram and a transition to an exit state of the sub-diagram corresponds to return to the calling state. For the implementation of this hierarchical specification he proposes, a control unit built by interconnecting independent control units, each implementing a sub-diagram and having its own activation signal which start or halt its execution, in [Micheli94].

Also in 1994, Gajski proposes a hierarchical concurrent finite state machine (HCFSM) as an extension of the FSM with support for hierarchy and concurrency in [Gajski94]. According to him the statecharts model is well adapted to specify a HCFSM but he does not suggest any implementation.

#### 1.2 Control Units Overview

#### 1.2.1 Introduction

Embedded systems can be defined as computing and control systems dedicated to a certain application [Micheli94]. They are parts of larger systems [MicGup97] and they are widely used in the manufacturing industry, in consumer products, in vehicles, in communication systems, in industrial automation, in aerospace, etc. They are often used in life critical situations, where reliability, availability and safety are more important criteria than performance [Edwards97, MicGup97].

In the general case, an embedded system is composed of microcontrollers, application-specific integrated circuits (ASIC), field-programmable gate arrays (FPGA), as well as other programmable computing units such as digital signal processors (DSP) [Edwards97]. Since embedded systems interact with an analogue environment they often integrate components that implement A/D and D/A conversions [Edwards97, MicGup97].

The behaviour of an embedded system is defined by its interaction with the environment in which it operates [Gajski94] and in most cases they have to react continuously to their environment at the speed of the environment. These systems are called reactive systems [Micheli94, Edwards97]. Real-time systems implement functions that must execute satisfying timing constrains [Micheli94].

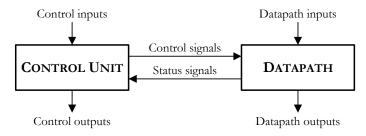

There are many kinds of devices that can be decomposed into a **datapath** (execution unit) and a **control unit** (see Figure 1.2) [Gajski94, Micheli94]. A particular kind of execution unit that can appear in an embedded system is a device depending on input data provided by sensors in the outside environment and generating output data that usually regulate mechanical components also in the outside environment via actuators. The actuators and sensors can be electronic, optical, mechanical, etc.

Figure 1.2 – Embedded system block diagram.

The datapath consists of registers, multiplexers and functional units such as ALUs, multipliers and shifters. A typical operation in the datapath reads the operands from the registers or external memory, computes the result in the functional units and writes the result into a destination register. The datapath is connected with external memory, being all memory accesses routed through registers with load and store operations.

The control unit is usually modelled as a FSM and consists of the state register, the next state logic to compute the next state to be stored in the state register and the control logic to drive its outputs. The control unit performs a set of instructions that depend on results of comparison operations carried by status signals from the datapath or external conditions carried by control inputs supplied by sensors in the outside environment and generates the control signals and the control outputs. The former defines what operations must be applied to which operands stored in the datapath while the latter controls actuators in the outside environment.

Chapter 1 : Introduction

### 1.2.2 Specification of Control Units

There are two different approaches for implementing a system from simple components, namely **bottom-up assembly** and **top-down decomposition**.

Systems can be built using a bottom-up assembly procedure where primitive building blocks are clustered into more complex blocks until the desired functionality of the system is achieved. But, since it is easier to understand the operation of a whole system by looking to its components and their interactions, the top-down decomposition is a more attractive approach and it is a good strategy for constructing any kind of complex system.

Top-down decomposition is the application of the principle of "divide and conquer", which is the basic way of breaking down complexity. A top-down decomposition allows the decomposition of a complex problem into smaller pieces until manageable pieces are found. The main advantage of a top-down approach is the great flexibility allowed in the exploration of possible designs [McFKow90]. The design process starts with an initial solution where the most important decisions are made and more refinements are added at each step thus allowing the exploration of alternatives. The design representation is also simplified in a top-down decomposition, because it is never necessary to deal simultaneously with multiple levels of the design or with multiple design representations [McFKow90].

However, the specification of a complex system in a top-down manner requires the use of hierarchy. Hierarchical specifications are therefore essential to manage the complexity of systems in terms of specification size and readability and have the following advantages:

- to master the complexity through the creation of hardware (software) macro blocks using encapsulation;

- to allow the reuse of hardware (software) macro blocks;

- to allow for the migration of complex algorithms normally implemented in software to hardware.

The appropriate requirements for the specification of control units are presented in the next chapter.

The behaviour of control-dominated systems, such as embedded real-time reactive control systems, is more naturally represented in the form of states and transitions between them provoked by external events. Therefore, a state-oriented model is more suitable to describe the functionality of control-dominated systems. There are several state-oriented models and they are presented in the next chapter. However, since the FSM is the most popular state-oriented model generally the design of control units follows the FSM model. The next paragraph presents several FSM-based implementations of a control unit.

#### 1.2.3 Implementation of Control Units

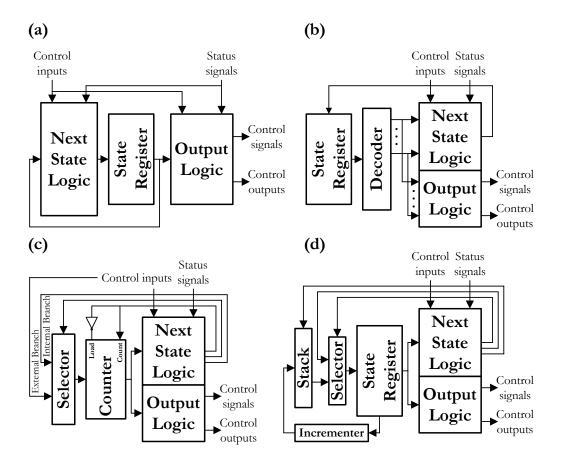

A control unit can follow the FSM model and therefore consisting of a state register, a next state logic and an output logic (see Figure 1.3a). But if a control unit has thousands of states this approach becomes very complex and the three alternative architectures depicted in Figure 1.3 and presented in [Gajski97] can be used to simplify the implementation of complex control units.

Figure 1.3 – (a) Control unit model. (b) Control unit with decoder. (c) Control unit with counter. (d) Control unit with stack.

The first architecture (see Figure 1.3b) uses a decoder, in order to simplify the next state and output logic implementation. Since each state is identified by a state signal, which is 1 when the state register is in that particular state and 0 otherwise, the signals generated in the next state and output logic blocks, i.e. the next state, the control signals and the control outputs will fall in two situations. If they only depend on the present state they can be implemented with n-input OR gates where n represents the number of states in which each signal is asserted. If they depend on the present state and on input signals, i.e. the control inputs and the status signals, they can be implemented with AND-OR logic, having the AND gates normally only two inputs, one being the state signal and the other being the input signal.

Chapter 1 : Introduction

If a control unit has many unconditional state sequences in which each state has only one next state, and if the states are encoded in a way that each state encoding can be obtained by incrementing the state encoding of its previous state, then the state register can be replaced with a counter (see Figure 1.3c). In this architecture, two more signals must be added to the next state logic [Gajski97]. A load/count signal that controls the counter behaviour, i.e. incrementing the state or loading a predefined state (branch state) to branch out of the sequence. A selector control signal that will select the proper value of the branch state, that can be supplied internally by the next state logic or provided externally through the control inputs.

In order to modularise the implementation of the control unit, frequently used tasks can be encoded as subroutines, instead of repeating the same sequence several times. For this purpose it is necessary a stack memory, which will save the state that follows the subroutine call (see Figure 1.3d). This architecture demands two more signals to be added to the next state logic [Gajski97]. A selector control signal that will select the proper state to be loaded in the state register, i.e. the next state or the state previously stored in the stack, and a push/pop signal to control the stack actuation. The state that follows the subroutine call that is saved on the stack is obtained by incrementing the state encoding of the previous state in the incrementer block.

A final strategy to simplify the control unit implementation is to replace the next state and the output logic blocks by read-only memories (ROM). When using this approach the state register acts as the ROM address register. In order to reduce the size of the next state ROM, it is very important to reduce the number of control inputs and status signals used in the next state generation. That can be done by selecting the minimal input signals with the introduction of a conditional selector in the above architecture [Gajski97]. This architecture of a control unit is usually called microprogrammed control and the task of converting state transition diagrams or ASM charts into ROM words is microprogramming.

However, all these three architectures suggested in [Gajski97] are flattened implementations and cannot provide such facilities as flexibility, extensibility and reusability. Moreover, they cannot be implemented from a hierarchical specification, unless it is flattened into a non-hierarchical specification first.

## 1.2.4 Synthesis of Control Units

The synthesis process of a control unit always starts with the specification of its intended functionality and ends with the implementation of the control unit. During the process the control unit acquires different representations, which differ in the type of information they highlight.

At the specification step (behavioural representation) the control unit is viewed as a black box with inputs and outputs and its functionality is specified behaviourally by means of an algorithm or using a state-based formal model, like for example finite state machine diagrams or the equivalent state transition tables.

After the synthesis process the control unit is viewed as a set of components and their connections (**structural representation**). The components can be simple logic gates or alternatively programmable logic devices (PLD) such as PALs, PLAs, ROMs and basic memory elements such as flip-flops to serve as the control unit memory. Nowadays, designers can take advantage of sophisticated field-programmable devices such as FPGAs. Not only can they provide a large number of logic gates and flip-flops that can be connected in various ways, but some of them can also be reprogrammed as many times as the designer needs.

The process of generating a structural view of a logic level model with an interconnection of logic primitives is called (**sequential**) **logic synthesis** [Gajski94, Micheli94].

The first design methodology was based on a **capture-and-simulate** approach [Gajski94]. In this methodology an initial architectural block diagram specification would be produced and each functional block would be converted into a circuit schematic that could be captured by a schematic tool and then its functionality could be verified through simulation.

In recent years logic synthesis became an integral part of the design process and once logic synthesis was accepted by the design community, designers began to use Boolean expressions and finite state machine diagrams to describe logic, instead of capturing gates with schematic tools. Finally, this new methodology encouraged the practice of capturing a design through behavioural descriptions based on hardware description languages and the capture-and-simulate methodology has given way to a **describe-and-synthesise** methodology [Gajski94].

In this new methodology the design structure is generated by automatic synthesis using CAD tools instead of by manual synthesis that is very tedious for all but trivial circuits. Since this methodology can be applied on several levels of abstraction it had evolved to higher levels of abstraction with large productivity gains [Gajski94].

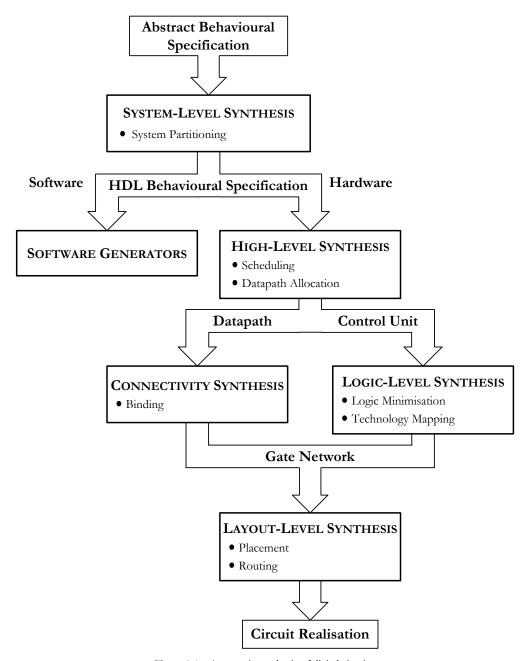

The automatic synthesis of digital circuits is normally divided into the four main steps depicted in Figure 1.4.

The first step is the **system-level synthesis**. At this level, the abstract functionality of a system is decomposed into different tasks, which are partitioned between hardware and software implementation. A lot of research is currently being developed and the system-level synthesis of embedded systems is normally named as software-hardware codesign or software-hardware cosynthesis [GupMic93, ThoAdaSch93, Wolf94, IsmJer95, MicGup97, StaWol97].

CHAPTER 1: INTRODUCTION 11

Figure 1.4 – Automatic synthesis of digital circuits.

The second step is the **high-level synthesis** (sometimes called behavioural or architectural synthesis). The tasks to be implemented in hardware are described behaviourally using a hardware description language (HDL) and the result is both a structural view of the datapath and a logic-level specification of the control unit. There are two basic tasks at this step. The **allocation** task determines the type and quantity of resources used in the datapath. The **scheduling** task makes the partition of the behavioural description into control steps (states) so that the allocated resources can compute all the variable assignments in each state. Highlevel synthesis is well documented in [McFParCam90, CamWol91, Gajski92, MicLauDuz92, GajRam94, Micheli94, WalCha95].

The third step is **logic-level synthesis** and it is divided in two parts. The **datapath synthesis** consists of a complete binding of the datapath, defining the interconnection among the resources, steering logic circuits like multiplexers or busses, registers, input/output ports and the control unit [Micheli94]. The **control unit synthesis** consists in the generation of a state register and the logic that generates the next state and the outputs of the control unit. The logic synthesis tasks are **logic minimisation** and **technology mapping**. Logic minimisation is used to reduce the size or delay of the logic and technology mapping transforms a technology independent logic network generated during the logic minimisation step into a network of standard gates from a particular library.

Since the control unit is modelled as a FSM, the first task of the logic-level synthesis also known as **sequential logic synthesis**, is further divided into the three following tasks normally used in the optimisation of FSMs:

- 1. **state minimisation** is used to decrease the number of states of the FSM, by replacing equivalent states with a single state. It is a very important task, since the number of states determines the size of the state register and combinational logic;

- 2. **state encoding** assigns binary codes to the abstract states of the FSM, with the purpose of minimising the next state and output functions;

- 3. **logic minimisation** is used to reduce the size or delay of the combinational logic that implements the next state and output functions.

Logic-level synthesis is well documented in [AshDevNew92, MicLauDuz92, Micheli94].

Finally, the **layout-level synthesis** step consists in generating the layout of the chip. The major tasks are **placement** of the components and wiring them also known as **routing** [Micheli94].

# 1.3 Objectives of the Work

With the increasing complexity of control units, many authors have proposed hierarchical specification models. However, the hierarchical implementations proposed for the synthesised control units did not support the versatility of the specification models.

Therefore, the goal of this thesis is the development of a methodology for the synthesis of reprogrammable control units from hierarchical specifications described with HGSs, i.e. to propose hierarchical FSM models based on the HFSM with stack memory, which can provide such facilities as flexibility, extensibility and reusability. And also to propose a FSM model that can combine hierarchy and parallelism.

Another goal is to propose a sequential logic synthesis methodology that can convert the hierarchical specification of control units in the proposed hierarchical

Chapter 1: Introduction 13

FSM models. Since, the sequential logic synthesis of a FSM is a well known subject, the proposed methodology will consist in the transformation of the hierarchical specification into a state transition table already minimised in terms of states, i.e. to implement automatically the first step of sequential logic synthesis. Since, manual synthesis is very tedious and error prone for all but trivial circuits, another purpose of this thesis is to create a tool that can automatically implement this synthesis methodology.

In order to validate the proposed models and the synthesis methodology, the VHDL simulation for an implementation based on lookup tables will be used.

# 1.4 Organisation of the Thesis

This thesis is organised as follows:

- Chapter 2 is devoted to the specification of control units. The specification requirements needed to conceptualise embedded reactive control units are described. The chapter presents the most common state-based formal models and the main characteristics of the VHDL hardware specification language.

- Chapter 3 describes in detail the graph-schemes of algorithms and how they

can be used to synthesise Moore and Mealy finite state machines. The

hierarchical graph-schemes and the parallel hierarchical graph-schemes are

presented in detail. The facilities provided by the tool SIMULHGS for the

verification and simulation of algorithms described by hierarchical graphschemes are presented.

- Chapter 4 starts by introducing the implementation of a hierarchical algorithm in a finite state machine with stack memory. The first models of the hierarchical and the parallel finite state machines are briefly explained and the new proposed models are fully described. The new facilities provided by them and the concept of a virtual hierarchical finite state machine are presented. Finally a full description of the proposed synchronisation mechanism for the different machines is made.

- Chapter 5 is devoted to the synthesis of the proposed hierarchical and parallel

machines. The steps that must be performed in order to transform a

hierarchical algorithm to an ordinary state transition table are enumerated and

explained in detail. The facilities provided by the tool **SIMULHGS** to

perform the automatic synthesis of hierarchical machines are presented.

- Chapter 6 describes the internal decomposition of the machines and the optimisation techniques used for a RAM-based implementation.

- Chapter 7 presents the VHDL simulation results of the hierarchical and parallel machines and explains how to provide flexibility, extensibility and reusability. The comparison between a hierarchical and a non-hierarchical implementation of an algorithm is made.

- Finally, chapter 8 presents the final conclusions and proposes future work.

# 2 Specification of Control Units

## Summary

The aim of this chapter is to survey the specification of control units in particular those that can appear in embedded real-time reactive control systems.

The design process of an embedded system begins with the specification of its intended functionality. Since, in most cases embedded systems are very complex and heterogeneous, designers need a precise manner of capturing this functionality in order to ensure correct implementations of a system. The best way to achieve the level of precision required is to use a **formal model**. There are different kinds of formal models, but a state-oriented model is more suitable for describing control-dominated systems.

However, since a model is basically a theoretical concept, designers need to use a **hardware description language** in order to capture these formal models in a concrete form. There are different description languages, **VHDL** being the most widely used by the academic community.

There are a variety of formal models and hardware description languages. Hence, for choosing the more appropriate model and language it is necessary to first understand the **specification requirements** for conceptualising embedded systems.

### 2.1 Introduction

System design is the implementation of a desired functionality with a set of physical components, and the whole process starts by specifying the desired functionality. Since a natural language description is often ambiguous and incomplete, designers need a more precise way to specify the system functionality. The best way to achieve the level of precision required is to consider the system as a set of simpler objects. There are different methods for decomposing the functionality into simpler objects. They differ in the type of the objects and the rules for assembling the system functionality. Each particular method is called a (formal) model [Gajski94, Edwards97]. Moreover, in order to master the design complexity and heterogeneity, the use of formal models is recommended to ensure implementations that are correct by construction [Edwards97].

However, to establish the formal model more appropriate for capturing the functionality of control units, in particular those that can appear in embedded real-time reactive control systems, it is necessary to establish a relation between the specification requirements of the embedded systems and the characteristics of the formal models.

# 2.2 Specification Requirements

The requirements appropriated for conceptualising embedded systems are the following [Gajski94, GupLia97].

#### 2.2.1 State transitions

Embedded systems are best conceptualised as a set of modes or states, where each mode represents a state of being or some arbitrary computation. They are constantly responding to external events computing their outputs as a function of their inputs and their present state. The transitions between states are determined by external events.

### 2.2.2 Concurrency

In many situations the representation of the system behaviour with only sequential sub-behaviours would result in complex and unnatural descriptions that can be difficult to understand. Therefore, embedded systems are more easily conceptualised as a set of concurrent sub-behaviours that collaborate with each other in order to achieve the desired functionality.

# 2.2.3 Hierarchy

The "Divide and conquer" principle is the basic way of handling complexity. The hierarchical specification of a system allows it to be described as a set of smaller subsystems and enables the designer to focus on one subsystem at a time. There are two kinds of hierarchy namely, structural and behavioural [Gajski94].

**Structural hierarchy** is defined as the process of decomposing a system as a set of interconnected components, each one of them can in turn have its own internal decomposition. It allows the designer to generate a new component from a set of already existing components. Structural hierarchy is closely related to concurrency.

**Behavioural hierarchy** is defined as decomposing the system behaviour into distinct sub-behaviours that can be either sequential or concurrent. It allows the designer to break down the system complexity into manageable parts.

Both structural hierarchy and behavioural hierarchy are required to allow the specification of a complex embedded system and they are essential to manage the complexity of systems in terms of specification size and readability.

#### 2.2.4 Non-determinism

**Non-deterministic** behaviour is the quality of a system to be unpredictable and yielding different results from the same sequence of events. Although often non-determinism is simply the result of an imprecise eventually incorrect specification, it can be an extremely powerful mechanism to reduce the complexity of a system by abstraction [Edwards97], since it eliminates all details that are not essential to a high-level description.

However, the behaviour of a system should be predictable and even if behaviour may be non-deterministic, when there is not the complete information to predict its exact behaviour, it can be decomposed into deterministic parts [GupLia97].

There are two types of non-deterministic behaviour in conceptual models [Gajski94]: **selection non-determinism** refers to non-deterministic selection of exactly one of several choices; **ordering non-determinism** involves a non-deterministic ordering of several actions that have to be executed.

#### 2.2.5 Behavioural Completion

**Behavioural completion** is defined as the ability to indicate that the behaviour has completed, i.e. that all the computations in the behaviour have been performed, and that other behaviours can detect this completion [Gajski94].

Behavioural completion is achieved in a state-based specification with the explicit definition of a set of final states, and with the control flowing to one of these final states. When using programming language constructs behavioural completion occurs when the last statement in the program has been executed.

The specification of behavioural completion has two advantages [Gajski94]: it helps conceptualising each hierarchical level of description as an independent module, facilitating its analysis and verification; it allows a natural decomposition of behaviour into sequential sub-behaviours.

#### 2.2.6 Programming Constructs

Certain sub-behaviours of embedded systems can be specified more easily by means of mathematical expressions or an algorithm. There are several notations to describe algorithms, but programming language constructs are more usually used.

These constructs include assignment statements, branching statements (if, case statements), iteration statements (while, repeat and for loops), and subroutines (functions and procedures). The support of structured data types such as records, arrays and linked lists that allow for the modelling of complex data structures is also a very useful feature.

#### 2.2.7 Communication

If the behaviour of a system is described as a set of concurrent sub-behaviours or processes they need to communicate with each order, in order to achieve the desired functionality. This kind of communication between them is usually conceptualised in term of the **shared memory** or the **message passing** paradigms [Gajski94].

In the shared memory model, each sending process writes to a shared medium, such as a global variable or port, which can be read by all receiving processes [Gajski94]. The shared medium can be **persistent** or **non-persistent**.

A persistent shared medium is one that retains the value written by one process, until that value is rewritten by another process, while in a non-persistent shared medium the data is only available at the instance when it is written, since it is not retained by the medium between two successive writes [Gajski94].

In the message-passing model, the data is transferred between processes over an abstract medium called a **channel**, using send-receive primitives [Gajski94].

#### 2.2.8 Synchronisation

When the behaviour of a system is described as a set of concurrent subbehaviours or processes, each process may generate data and events that need to be recognised by the other processes. In such cases, data exchanged between processes or actions performed by different processes at the same time may need to be synchronised [Gajski94]. There are two synchronisation methods namely, control-dependent and data-dependent.

In a control-dependent synchronisation mechanism, the control structure of the process is responsible for the synchronisation [Gajski94]. In addition to that, the synchronisation can be achieved by means of the following inter-process communication methods [Gajski94]: **shared-memory based synchronisation**; **synchronisation by common event**; **synchronisation by status detection**; **synchronisation by message passing**.

#### 2.2.9 Exceptions

In some cases, the occurrence of a certain external event, like a reset or an interrupt, demands that a behaviour will be immediately terminated rather than having to wait for the computation to complete, and that a predefined behaviour will be executed instead.

#### **2.2.10 Timing**

Since in real-time systems the performance is measured in terms of how well it respects the timing constraints, it is important the notion of timing to reflect real implementations, i.e. by specifying time the simulation results obtained are more realistic. There are two ways of specifying timing information namely, **functional timing** and **timing constrains** [Gajski94].

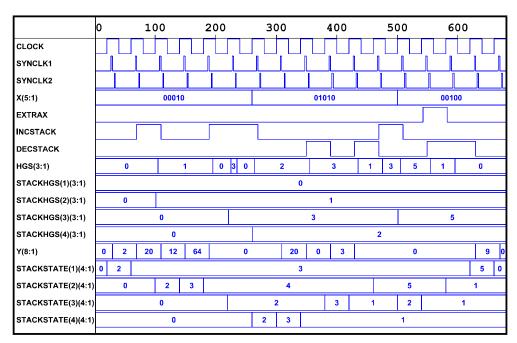

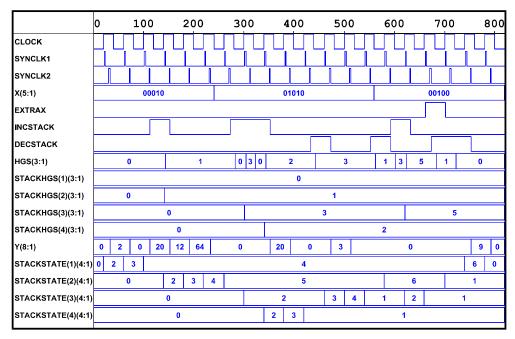

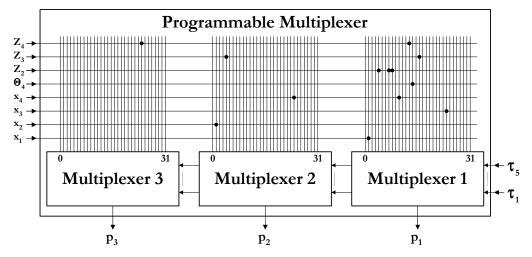

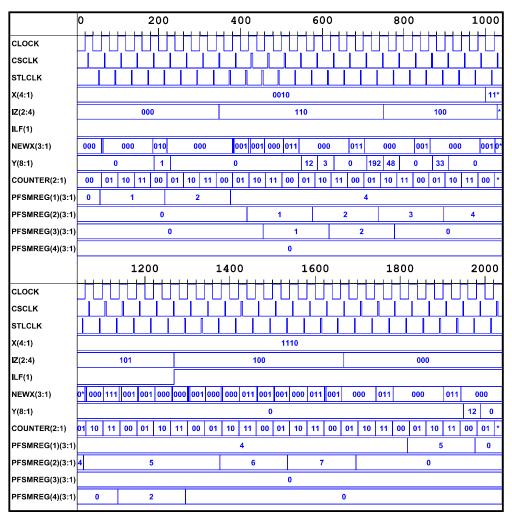

Functional timing is defined as all timing information that affects the simulation output of the system specification, and therefore adding functionality to the system. Timing constrains are utilised in the specification of a system in order to be used by simulation and synthesis tools.