Cristiano Ferreira Gonçalves Amplificadores de Potência para Radiofrequência Insensíveis à Impedância de Carga

Load Insensitive Radio Frequency Power Amplifiers

### **Cristiano Ferreira** Gonçalves

## Amplificadores de Potência para Radiofrequência Insensíveis à Impedância de Carga

### Load Insensitive Radio Frequency Power Amplifiers

Tese apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Doutor em Engenharia Eletrotécnica, realizada sob a orientação científica do Doutor Pedro Miguel da Silva Cabral, Professor Auxiliar do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro e coorientação científica do Doutor José Carlos Esteves Duarte Pedro, Professor Catedrático do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro.

> Este trabalho foi financiado pela Fundação para a Ciência e a Tecnologia (FCT) e pelo Ministério da Educação e Ciência (MEC) por fundos nacionais através do Projeto PTDC/EEI-TEL/30534/2017 e também pela bolsa de doutoramento com a referência SFRH/BD/130728/2017 atribuída pela Fundação para a Ciência e a Tecnologia (FCT) através do orçamento de estado e pela União europeia através do Fundo Social europeu (FSE) segundo o Programa Operacional Regional do Centro.

a Tecnologia

### o júri

| presidente | <b>Doutora Anabela Botelho Veloso</b><br>Professora Catedrática da Universidade de Aveiro (por delegação da Reitora da<br>Universidade de Aveiro) |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| vogais     | <b>Doutora Zoya Popovic</b><br>Distinguished Professor da University Of Colorado Boulder                                                          |

|            | <b>Doutor José Ángel García García</b><br>Professor Titular do Departamento de Ingeniería de Comunicaciones da Universi-<br>dade de Cantábria     |

|            | <b>Doutor José Alberto Peixoto Machado da Silva</b><br>Professor Associado da Universidade do Porto - Faculdade de Engenharia                     |

|            | Doutor João Nuno Pimentel da Silva Matos<br>Professor Associado da Universidade de Aveiro                                                         |

|            | Doutor Pedro Miguel da Silva Cabral (Orientador)                                                                                                  |

Professor Auxiliar da Universidade de Aveiro

agradecimentos Agradeço à minha família e à minha namorada por todo o apoio.

Agradeço aos meus orientadores pelo acompanhamento cuidado deste trabalho.

Agradeço à Universidade de Aveiro e ao Instituto de Telecomunicações pela disponibilização das condições necessárias à realização do trabalho descrito nesta tese.

Por último, agradeço aos Doutores Luis Carlos Cótimos Nunes e Filipe Miguel Esturrenho Barradas que, embora não pertencendo à minha equipa de orientação, tiveram um papel fundamental neste trabalho e no meu crescimento como investigador.

palavras-chave

resumo

Amplificadores de potência, amplificadores Doherty, insensibilidade à carga, malhas de adaptação sintonizáveis, medição de impedância, modulação de tensão de alimentação.

Os amplificadores de potência de estado sólido (SSPAs) evoluíram significativamente nas últimas décadas, principalmente devido à utilização de novas tecnologias de transístores, como os transístores de alta mobilidade (HEMTs) de nitreto de gálio (GaN), de ferramentas muito avançadas de projeto assistido por computador (CAD) e de algoritmos de pré-distorção digital (DPD) muito evoluídos. Isto levou a uma melhoria de desempenho considerável, em termos de eficiência energética, potência de saída e linearidade. Normalmente, para obter estes níveis de desempenho, os engenheiros projetam os amplificadores permitindo que os transístores utilizados operem muito perto do seu limite físico de funcionamento seguro e considerando que vão operar para uma carga fixa. No entanto, os amplificadores projetados são utilizados em diversas aplicações industriais e/ou telecomunicações e, em alguns casos, como por exemplo fornos micro-ondas ou estações base 5G, a sua carga de saída pode variar devido a várias causas, que podem ser previsíveis ou imprevisíveis. Neste cenário não ideal, os transístores utilizados operam para cargas não ótimas e o desempenho dos amplificadores pode ser muito degradado. Além disso, em projetos muito otimizados, onde os transístores são operados perto do seu limite de funcionamento seguro, a sua durabilidade pode ser reduzida ou, em casos extremos, podem até ser permanentemente danificados. Portanto, para melhorar o desempenho dos amplificadores em cenários de carga variável, são necessárias novas arquiteturas e/ou técnicas que visam reduzir a variação da carga vista pelos transístores utilizados. Esta tese apresenta várias estratégias para melhorar a insensibilidade dos amplificadores em relação à variação de carga. As técnicas apresentadas são baseadas em malhas de adaptação dinâmicas (TMNs) e na variação da tensão de alimentação dos amplificadores. As malhas de adaptação desenvolvidas permitiram reduzir a variação de carga vista pelo amplificador e a variação da sua tensão de alimentação permitiu melhorar o desempenho para operação com cargas não ótimas. Estas abordagens foram testadas e validadas em amplificadores baseados num só transístor, e, posteriormente, com base nas suas vantagens e desvantagens, a técnica mais promissora – a modulação da tensão de alimentação – foi selecionada para o projeto de um amplificador Doherty, que é imprescindível para telecomunicações. Além disso, como em algumas aplicações a variação da carga de saída pode ser imprevisível, também desenvolvemos um sistema completo que inclui um circuito de medida de impedância e compensação do desempenho do amplificador em tempo real.

keywords

abstract

Doherty amplifiers, impedance measurement, load insensitivity, power amplifiers, supply voltage modulation, tunable matching networks.

Solid state power amplifiers (SSPAs) evolved significantly over the last few decades, mainly, due to the use of new transistor technologies, such as gallium nitride (GaN) high-electron-mobility transistors (HEMTs), very advanced computer-aided design (CAD) software, and very effective digital pre-distortion (DPD) algorithms. This led to a considerable performance improvement, in terms of energy efficiency, output power, and linearity. To achieve this performance, power amplifier (PA) designers normally push the used transistors very close to their physical safe operating limits, and consider them to operate for a fixed output load. However, the designed PAs are used for many different industrial and/or telecommunication applications, and, in some cases, such as, for example, microwave cooking or massive multiple-input multiple-output (MIMO) fifth generation (5G) base stations (BSs), the output load of these amplifiers can change. Under this nonoptimal scenario, the used transistors will operate for non-nominal loads, and the PAs performance can be severely degraded. Moreover, in highly optimized designs, where the transistors are operated close to their safe limits, their reliability can be reduced or, in extreme cases, they can even be permanently damaged. Therefore, load insensitive PA architectures, and/or techniques that aim at reducing the load variation seen by the PA, are necessary to improve the performance under load varying scenarios. This thesis presents various strategies to improve load insensitiveness of PAs. The presented techniques are based on tunable matching networks (TMNs) and on the amplifiers' drain supply voltage  $(V_{DS})$  variation. The developed TMNs successfully reduced the load variation seen by the PA, and its performance was greatly improved, for non-optimal loading, by also using the derived load dependent  $V_{DS}$  variation. These different approaches were tested and validated on single-ended PAs and then, based on their advantages and disadvantages, the most promising technique – the supply voltage modulation – was selected for the design of a Doherty power amplifier (DPA), which is of paramount importance for telecommunication applications. Moreover, since in some applications the output load variation can be unpredictable, we also developed a complete quasi-load insensitive (QLI) PA system that includes an impedance tracking circuit and an automatic real-time compensation of the amplifier performance.

## Contents

| Co       | onten        | its              |                                   | i   |

|----------|--------------|------------------|-----------------------------------|-----|

| Lis      | st of        | Figure           | es                                | iii |

| Lis      | st of        | Tables           | 5                                 | v   |

| Li       | st of        | Acron            | lyms                              | vii |

| 1        |              | oducti           |                                   | 1   |

|          | $1.1 \\ 1.2$ | Motiva<br>Outlin |                                   | 5 7 |

| <b>2</b> | Stat         | e-of-tl          | he-Art                            | 9   |

|          | 2.1          | Load I           | Insensitive PA Architectures      | 11  |

|          |              | 2.1.1            | Quasi-Load Insensitive Class E    | 11  |

|          |              | 2.1.2            | Balanced PAs                      | 12  |

|          |              | 2.1.3            | Digital Doherty PAs               | 13  |

|          | 2.2          | Isolati          | on at OMN                         | 17  |

|          |              | 2.2.1            | Magnetic Isolator                 | 17  |

|          |              | 2.2.2            | Compression Networks              | 17  |

|          |              | 2.2.3            | Tunable Matching Networks         | 19  |

|          | 2.3          | Compa            | act Impedance Measurement         | 23  |

|          |              | 2.3.1            | Coupler Based                     | 23  |

|          |              | 2.3.2            | Sampled Line Based                | 25  |

| 3        | Obj          | ective           | and Main Goals                    | 27  |

| 4        | Loa          | d Inse           | nsitive Power Amplifier Solutions | 29  |

|          | 4.1          | Tunab            | le Matching Network               | 31  |

|          | 4.2          | Imped            | ance Tracking                     | 35  |

|          | 4.3          | Supply           | y Voltage Modulation              | 39  |

|          |              | 4.3.1            | Single-Ended PA                   | 39  |

|          |              | 4.3.2            | Doherty PA                        | 41  |

| 5        | Mai          | n Con            | tributions and Innovations        | 45  |

| 6        | Con          | clusio           | ns                                | 49  |

| 7                | Future Work                                              | 51  |

|------------------|----------------------------------------------------------|-----|

| Bi               | bliography                                               | 53  |

| $\mathbf{A}_{j}$ | ppendices                                                | 59  |

| A                | Tunable Matching Network                                 | 61  |

| в                | Impedance Measurement                                    | 73  |

| С                | Supply Voltage Modulation on Single-Ended PAs            | 85  |

| D                | Supply Voltage Modulation on Single-Ended PAs - Extended | 91  |

| $\mathbf{E}$     | Supply Voltage Modulation on Doherty PAs                 | 105 |

| $\mathbf{F}$     | Supply Voltage Modulation on Doherty PAs - Extended      | 111 |

# List of Figures

| 1.1  | a) Likely scenario for massive MIMO deployment, where different types of an-<br>tenna arrays can be spotted, from [7]. b) Mutual coupling between antenna<br>elements and its effect on the PA output load (where $b_{2,n}$ and $a_{2,n}$ are, respec-<br>tively, the incident and reflected waves on each antenna element) | 2  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | LP contours of an idealized class B PA. The DE is shown in red and the output                                                                                                                                                                                                                                               | 2  |

| 1.2  | power in blue                                                                                                                                                                                                                                                                                                               | 2  |

| 2.1  | LP analysis of a class E PA based on the design equations for a $q = 1.3$ . Drain efficiency in red and output power in blue.                                                                                                                                                                                               | 12 |

| 2.2  | Balanced PA block diagram                                                                                                                                                                                                                                                                                                   | 12 |

| 2.3  | Output power LP contours and opposite phase load variations, which correspond to the $\Gamma$ seen by each amplifier composing the balanced PA                                                                                                                                                                              | 13 |

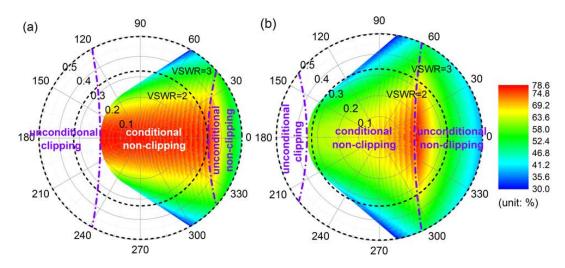

| 2.4  | Compensated (a) and original (b) LP analysis of the digital DPA, for FP operation, from [22].                                                                                                                                                                                                                               | 14 |

| 2.5  | Compensated (a) and original (b) LP analysis of the digital DPA, for the 3dB OBO level, from [22].                                                                                                                                                                                                                          | 14 |

| 2.6  | Compensated DPA FP (a) and 3dB OBO (b) DE, from [22], for an asymmetrical DPA.                                                                                                                                                                                                                                              | 15 |

| 2.7  | PA connected to the output load through an isolator, in this example $Z_0$ is equal to 50 $\Omega$ .                                                                                                                                                                                                                        | 17 |

| 2.8  | (N+1) port compression network                                                                                                                                                                                                                                                                                              | 18 |

| 2.9  | Transmission line compression network.                                                                                                                                                                                                                                                                                      | 18 |

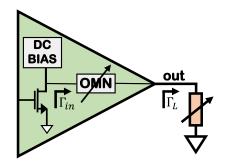

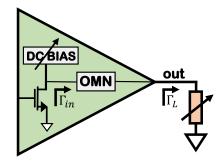

| 2.10 | PA design including a tunable OMN                                                                                                                                                                                                                                                                                           | 19 |

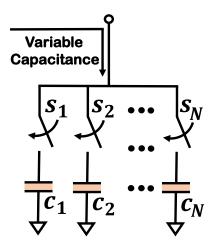

| 2.11 | Example of a widely used capacitor bank circuit topology                                                                                                                                                                                                                                                                    | 20 |

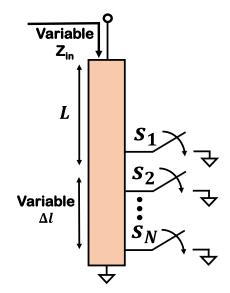

| 2.12 | Scheme of a variable length stub                                                                                                                                                                                                                                                                                            | 20 |

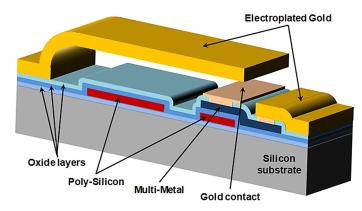

| 2.13 | Scheme of a typical MEMS switch structure, from [39]                                                                                                                                                                                                                                                                        | 22 |

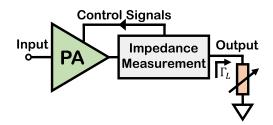

| 2.14 | Typical application of an impedance measurement circuit between the PA and its output load                                                                                                                                                                                                                                  | 23 |

| 2.15 | Typical system architecture for the measurement of the reflection coefficient amplitude and phase, in a) and b), respectively                                                                                                                                                                                               | 24 |

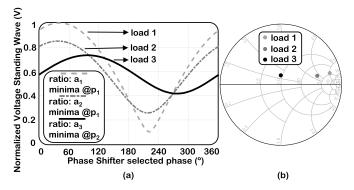

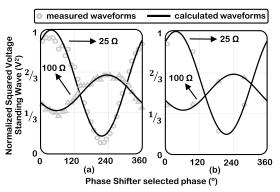

| 2.16 | a) Sampled line typical topology. b) Normalized voltage standing wave pattern for a short circuit termination (dashed) and open circuit termination (continuous).                                                                                                                                                           | 25 |

| 4.1  | a) Contours of the calculated necessary parallel reactance to eliminate the imag-<br>inary part of each load. b) Schematic diagram of the idealized compensation                                                                                                                                                          |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | network                                                                                                                                                                                                                                                                                                                   | 31 |

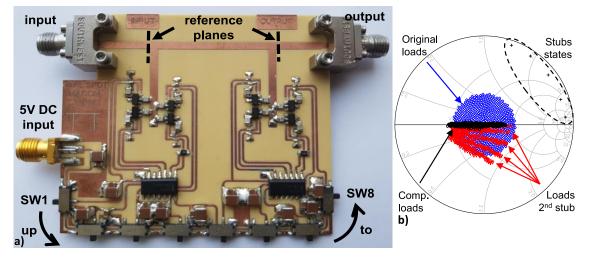

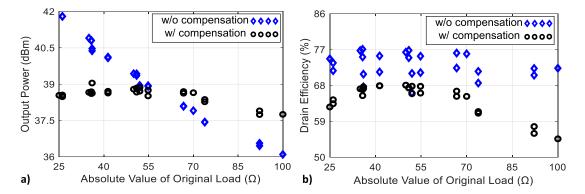

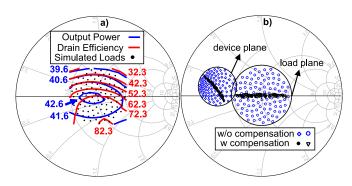

| 4.2  | a) Photography of the fabricated RCN. b) Original output loads, in blue, and compensated loads, in black.                                                                                                                                                                                                                 | 32 |

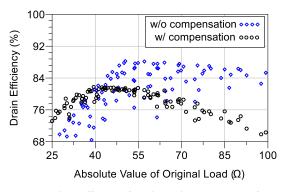

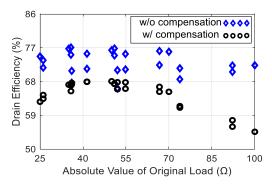

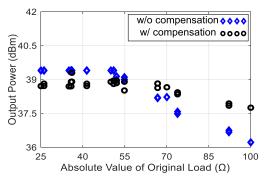

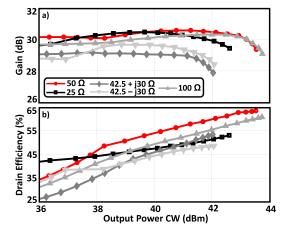

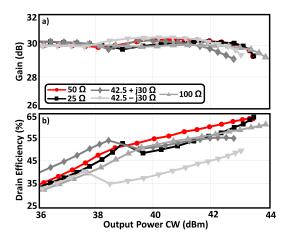

| 4.3  | a) Measured output power of PA 1, with and without the compensation net-<br>work. b) Measured DE of PA 1, with and without the compensation network.                                                                                                                                                                      | 33 |

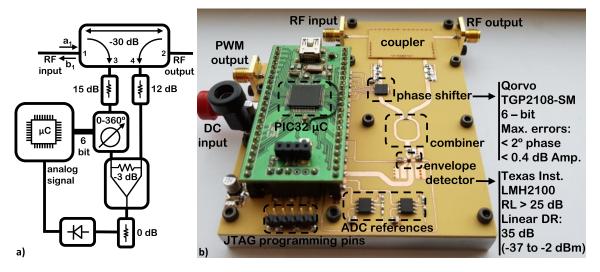

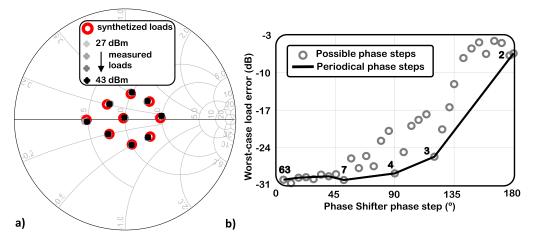

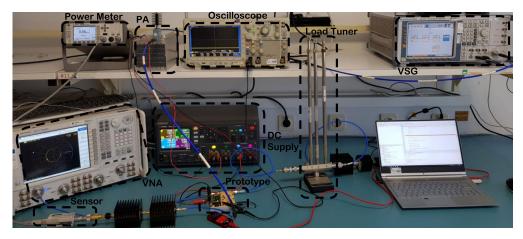

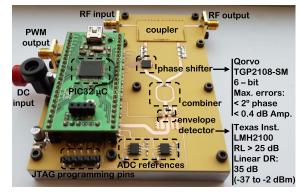

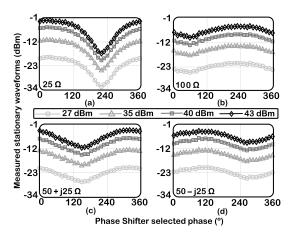

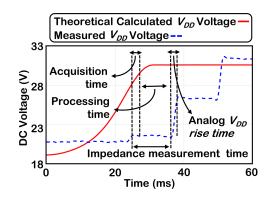

| 4.4  | a) Impedance measurement circuit schematic. b) Fabricated impedance measurement circuit and brief description of its main components                                                                                                                                                                                      | 35 |

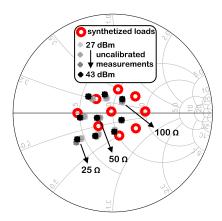

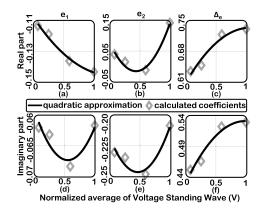

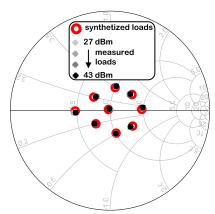

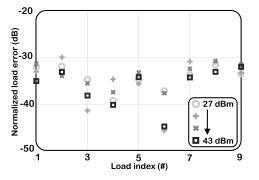

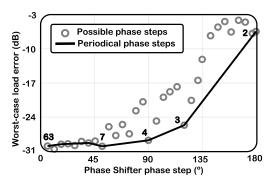

| 4.5  | a) Synthesized (red circles) and measured loads (gray scale dots) for various PA output power levels, using a $11.2^{\circ}$ phase shifter step. b) Worst-case measurement error for all the possible phase shifter steps. In black we show the available periodical phase steps and the correspondent number of measured |    |

|      | samples.                                                                                                                                                                                                                                                                                                                  | 36 |

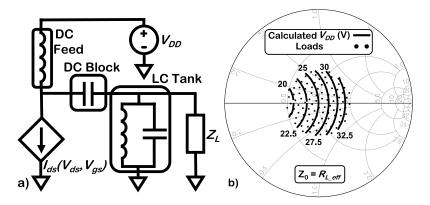

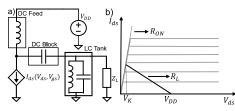

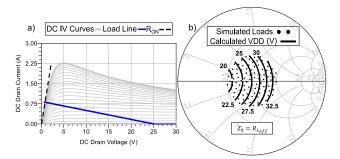

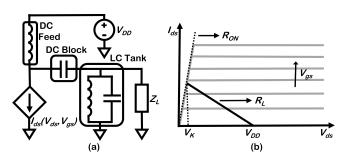

| 4.6  | Schematic of a RF PA with an adaptive drain supply voltage                                                                                                                                                                                                                                                                | 39 |

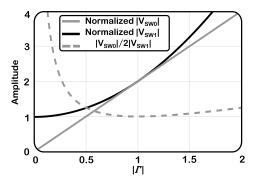

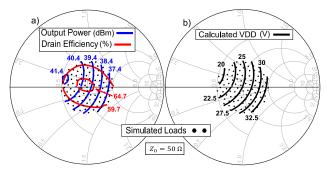

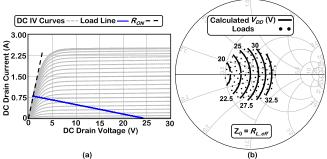

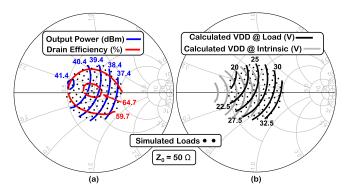

| 4.7  | a) Simplified PA output circuit considered during the theoretical analysis. b)                                                                                                                                                                                                                                            |    |

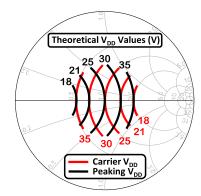

|      | Calculated $V_{DD}$ values for the used Wolfspeed device and for a nominal $V_{DD_0}$ of 25 V                                                                                                                                                                                                                             | 40 |

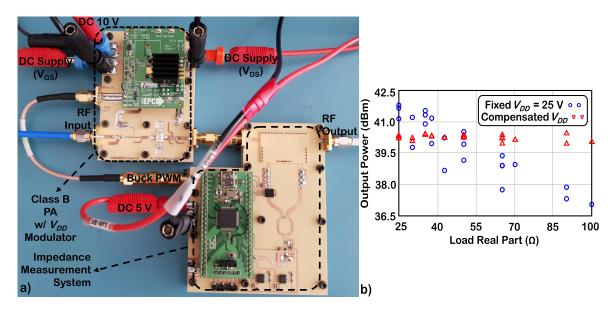

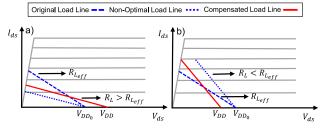

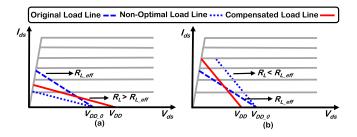

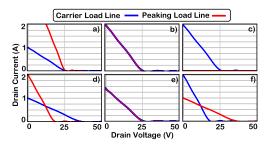

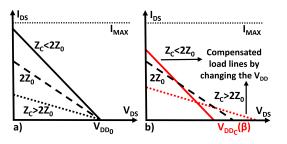

| 4.8  | Load line explanation of the compensation method for higher real loads, in a),                                                                                                                                                                                                                                            |    |

|      | and for lower real loads, in b)                                                                                                                                                                                                                                                                                           | 40 |

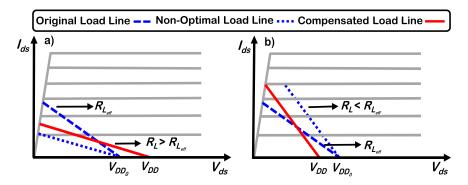

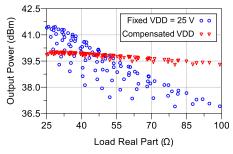

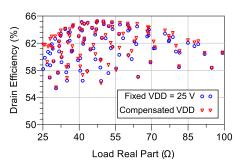

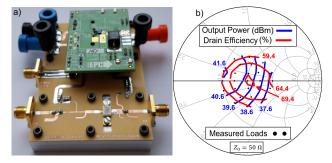

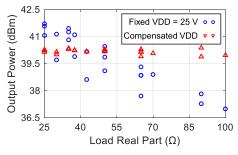

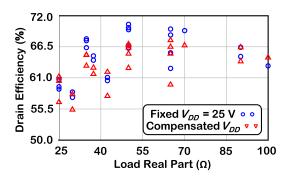

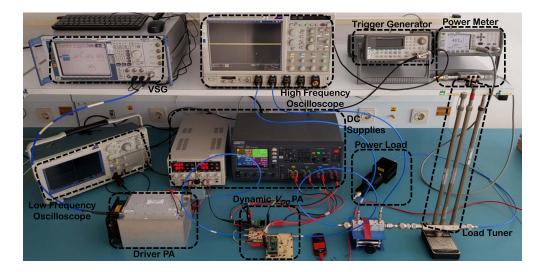

| 4.9  | a) Photography of the final prototype, which includes the $V_{DD}$ modulated class<br>B PA prototype and the impedance meter of Section 4.2. b) Measured output<br>power of the implemented PA prototype for a fixed $V_{DD}$ of 25 V, and for the                                                                        |    |

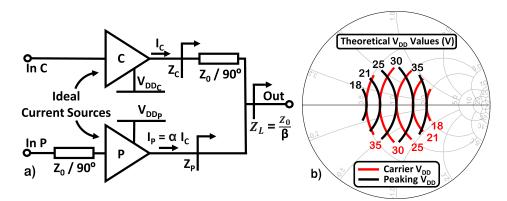

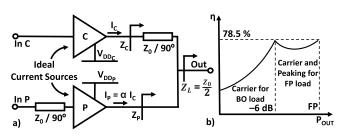

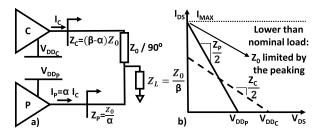

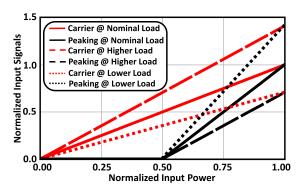

| 4.10 | optimal derived values                                                                                                                                                                                                                                                                                                    | 41 |

|      | analysis. b) Theoretical $V_{DD}$ values for the carrier and peaking devices, for a nominal $V_{DD_0}$ of 25 V. Note that the Smith chart reference $Z_0$ is the nominal                                                                                                                                                  |    |

|      | design load of the DPA.                                                                                                                                                                                                                                                                                                   | 42 |

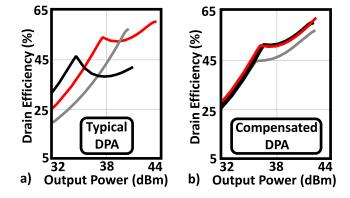

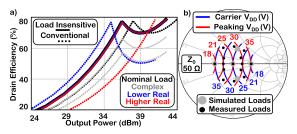

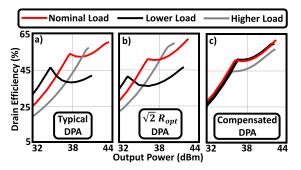

| 4.11 | a) DE profile of a typical DPA operating for the nominal load (red), half the nominal load (black), and twice the nominal load (gray). b) DE profile of the                                                                                                                                                               |    |

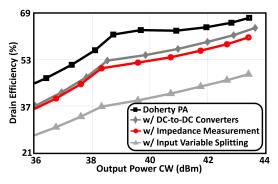

|      | proposed QLI DPA for the same loads                                                                                                                                                                                                                                                                                       | 43 |

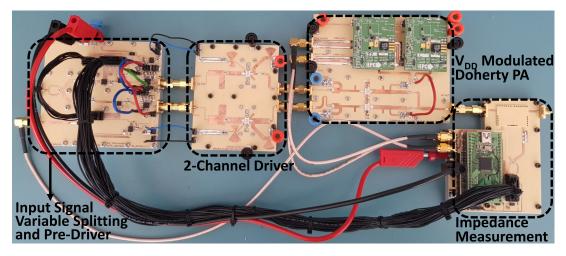

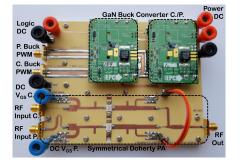

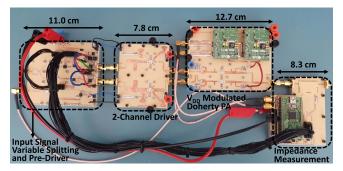

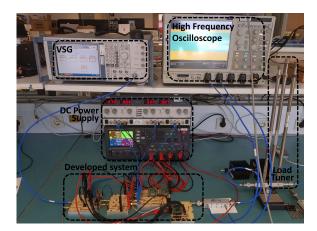

| 4.12 | Photograph of the fabricated system, including $V_{DD}$ modulation, impedance                                                                                                                                                                                                                                             |    |

|      | tracking and input splitting control.                                                                                                                                                                                                                                                                                     | 44 |

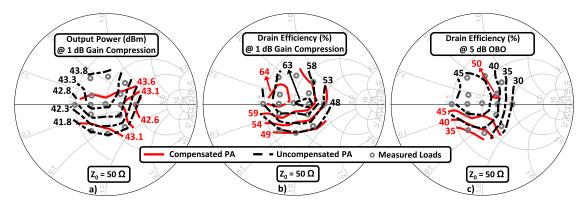

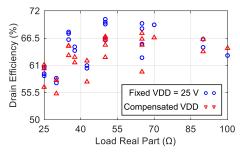

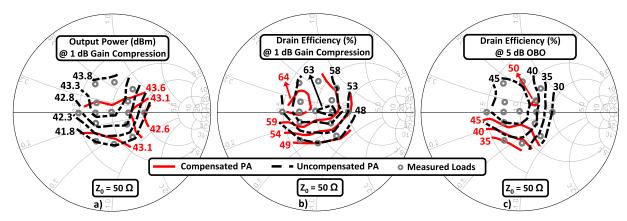

| 4.13 | LP of the fabricated prototype with and without $V_{DD}$ compensation. The                                                                                                                                                                                                                                                |    |

| -    | output power and DE at FP are presented in a) and b), respectively, and the                                                                                                                                                                                                                                               |    |

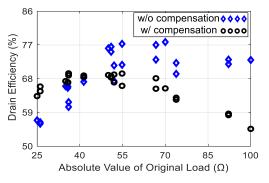

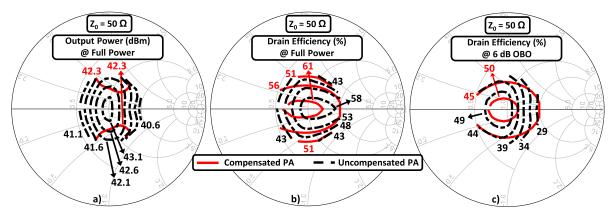

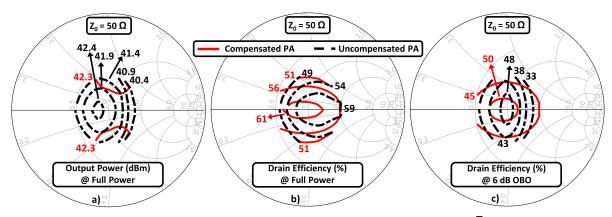

|      | BO DE in c)                                                                                                                                                                                                                                                                                                               | 44 |

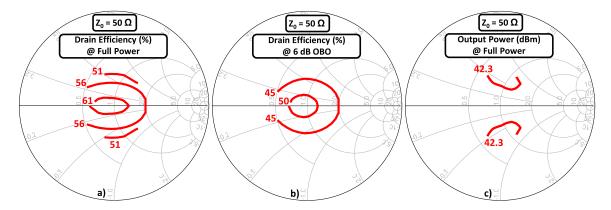

| 7.1  | Simulated DE of the developed QLI DPA prototype at FP, a), and BO, b),                                                                                                                                                                                                                                                    |    |

|      | and FP output power capability, c).                                                                                                                                                                                                                                                                                       | 51 |

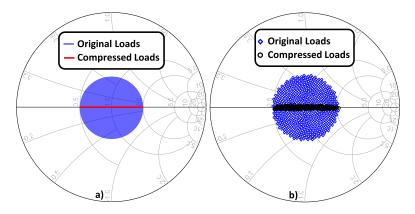

| 7.2  | a) Desired load compression for improvement of the developed DPA proto-<br>type performance. b) Simulated load compression obtained from the network                                                                                                                                                                      |    |

|      | designed in the first task of this PhD work.                                                                                                                                                                                                                                                                              | 52 |

# List of Tables

| 2.1 | CMOS FET switches state-of-the-art, from [40]                                                    | 22 |

|-----|--------------------------------------------------------------------------------------------------|----|

| 4.1 | Simulated improvement results for PA 1 and PA 2, with and without the com-<br>pensation network. | 32 |

| 4.2 | Summarized performance improvement of the proposed QLI DPA                                       |    |

## List of Acronyms

4G fourth generation 5G fifth generation ACPR adjacent channel power ratio BO back-off  ${\bf BS}\,$  base station **BST** barium strontium titanate **CAD** computer-aided design CMOS complementary metal-oxide-semiconductor **CW** continuous wave dc direct current  $\mathbf{D}\mathbf{C}$  duty-cycle **DE** drain efficiency **DLM** dynamic load modulation **DPA** Doherty power amplifier **DPD** digital pre-distortion  $\mathbf{FET}$  field effect transistor **FP** full power GaAs gallium arsenide GaN gallium nitride **HBT** heterojunction bipolar transistor **HEMT** high-electron-mobility transistor **IBO** input power back-off **IL** insertion loss

LDMOS laterally-diffused metal-oxide semiconductor

LMBA load modulated balanced amplifier

${\bf LP}\,$  load pull

**MEMS** micro-electromechanical systems

MIMO multiple-input multiple-output

**MMIC** monolithic microwave integrated circuit

$\mathbf{mmWave}$  millimeter-wave

$\mathbf{MCU}$  microcontroller unit

$\mathbf{OMN}$  output matching network

**OBO** output power back-off

$\mathbf{PA}$  power amplifier

**PAE** power added efficiency

PAPR peak-to-average power ratio

**PECVD** plasma-enhanced chemical vapor deposition

${\bf PWM}\,$  pulse-width modulation

**QAM** quadrature amplitude modulation

**QLI** quasi-load insensitive

**RCN** reactance compression network

$\mathbf{RF}$  radio frequency

SiGe silicon-germanium

**SOI** silicon on insulator

**SSPA** solid state power amplifier

**TLRCN** transmission line compression network

$\mathbf{TMN}$  tunable matching network

TOMN tunable output matching network

$V_{DS}$  drain supply voltage

**VNA** vector network analyzer

**VSWR** voltage standing wave ratio

# Chapter 1 Introduction

Nowadays, power amplifiers (PAs) are used for various applications and their performance has a considerable impact on the overall system operation. Therefore, in order to achieve the best performance possible in terms of output power density, direct current (dc) to radio frequency (RF) conversion efficiency, and linearity, often, the used transistors are used close to their physical safe operation limits. This design approach results in better performance for operation under the expected nominal output load. However, for specific operating conditions, PAs can be forced to operate under varying output load scenarios. In this non-optimal regime, the PA performance is degraded, mainly in terms of output power, drain efficiency (DE) and linearity. Moreover, since the devices are used close to their safe operation limits, changes to the PA expected operation environment can lead to severe reliability degradation or even permanent damage.

This non-optimal operating regime can happen due to various causes, and in different scenarios. Some of these scenarios include industrial applications of PAs, such as:

#### • microwave cooking,

where a high power solid state power amplifier (SSPA) is used as the microwave energy source for heating food in the oven cavity. In these applications, the PA output load, which is the cavity impedance, shows a strong dependency with the type of food that is inside the oven [1];

#### • plasma-enhanced chemical vapor deposition (PECVD),

where plasma conditions inside the deposition chamber are required to vary during the deposition process. This variation also leads to changes in the output impedance of the RF generator [2];

#### • particle accelerators,

where charged RF cavities are used to accelerate charged particle beams. In this case, the amount of reflected power changes due to the interaction between the cavity and the charged particle beam, causing an output impedance variation from the RF generator perspective [3].

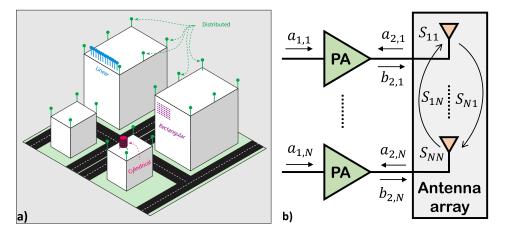

Other load variation scenarios can be found in **telecommunication applications**, where the PA output load can also change due to moving objects on the antenna proximity, e.g., the hand effect [4], or also due to mutual coupling between different antenna elements on fifth generation (5G) massive multiple-input multiple-output (MIMO) base stations (BSs) [5]. In the case of massive MIMO scenarios, as illustrated on Fig. 1.1, each antenna element is affected by its neighboring elements due to mutual coupling, which will cause an apparent load change for the PAs in each transmit path [6]. So, while the use of antenna arrays enables beamforming, which leads to an overall system efficiency improvement, this load variation results in PA performance degradation, making the use of such systems less viable.

Figure 1.1: a) Likely scenario for massive MIMO deployment, where different types of antenna arrays can be spotted, from [7]. b) Mutual coupling between antenna elements and its effect on the PA output load (where  $b_{2,n}$  and  $a_{2,n}$  are, respectively, the incident and reflected waves on each antenna element).

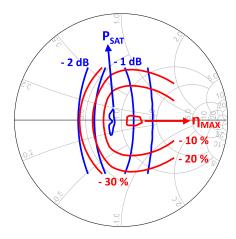

The described scenarios have demonstrated the importance of considering non-optimal output load variations during the design stage of PAs. However, most of the described applications are very complex and it is impracticable for PA designers to replicate these operating conditions. Therefore, in order to quantify the performance degradation of PAs operating in these scenarios, the respective impedance variations can be mimicked by load pull (LP) analysis. Figure 1.2 shows a typical simulated LP analysis of an idealized single-ended class B PA. For practical measurements, various non-optimal impedances need to be synthesized in the laboratory using a load tuner.

Figure 1.2: LP contours of an idealized class B PA. The DE is shown in red and the output power in blue.

In Fig. 1.2 the LP analysis was performed for non-optimal loads distributed within a 3.0 maximum voltage standing wave ratio (VSWR) circle. Even for this very simplified PA, the DE is degraded by around 30% and the output power is reduced by more than 2 dB, for the worst-case loads. In the following chapter, dedicated LP analyses based on practical implementations of state-of-art PAs are presented and discussed.

#### 1.1 Motivation

In [8], the authors have compared the performance degradation of different PA architectures, all of them based on devices operating in ideal class B, under output load mismatch. The simulated architectures were the typical single-ended amplifier, a Doherty power amplifier (DPA), a balanced amplifier, and a load modulated balanced amplifier (LMBA). This demonstrates that different types of amplifiers have distinct behavior under load mismatch, and, therefore, different levels of performance degradation.

DPAs are widely used in fourth generation (4G) telecommunication systems and believed to continue to be very useful for the next generation 5G BSs. Therefore, their output load sensitivity is an important performance characteristic. In [9] and [10] the authors analyzed the performance degradation of a 2 GHz DPA, for mismatched loads within a worst-case 2.2 VSWR circle. Even for this small mismatch value, the power added efficiency (PAE) was reduced by around 35%, at 6 dB of input power back-off (IBO), and the output power degraded by 1.5 dB. They also showed considerable gain variations, which certainly affect the linearity of the amplifier.

Very efficient single-ended amplifiers, based on, for example, class E operation, are also very interesting for industrial applications, were continuous wave (CW) signals, or signals with very low peak-to-average power ratio (PAPR), are used. In [11] the authors evaluated the load mismatch sensitivity of class E PAs under a maximum VSWR of 10. They have developed a general class E theoretical model that was used to evaluate the output power, PAE, and reliability degradation. The performed simulations and practical measurements have shown very similar results, with up to 10 dB of output power degradation and 50% of efficiency reduction. The amplifier reliability was evaluated by measuring the maximum drain voltage applied to the device, which can increase to extremely high values for mismatched class E operation, and cause serious reliability issues. The authors measured a worst-case maximum voltage of 4.5 times the nominal drain supply voltage  $(V_{DS})$ .

These examples shown how important can be the impact of output load mismatch on the performance of PAs. In order to solve this problem, various researchers have started to evaluate different ways to isolate PAs from their output loads, so that load variations do not affect the PA performance. Unfortunately, typical magnetic isolators are unwanted, since they do not maintain the PA output power, and reduce the compound efficiency due to the reflected power dissipation on a dummy load. Moreover, they are difficult to integrate in monolithic microwave integrated circuits (MMICs) and are too bulky and heavy when compared to the PA itself [12], [13]. The last argument is especially important for telecommunication applications, where the integration of the whole RF chain is very important to reduce the cost of 5G BSs, which is decisive since they are expected to be mass deployed.

Therefore, RF engineers need to design non-typical isolators, novel load insensitive PAs architectures or specific adaptive output matching networks (OMNs). Otherwise, the output power, efficiency and linearity of PAs will be severely degraded, and, consequently, impact the system performance for the various described applications.

#### 1.2 Outline

In Chapter 2, the state-of-the-art on techniques for the compensation of PAs operating under non-optimal loading is described. The first section presents various PA architectures that are, naturally, more insensitive to load variations in terms of output power or efficiency. The second section describes techniques that improve isolation at the PAs OMN. Some of the presented techniques are the dynamically adjustable matching networks, which are based on variable or switchable components. Therefore, we also present a brief state-of-the-art on these components and their technologies. The third section is devoted to a brief description of the latest compact and dedicated impedance measurement techniques for application on PAs.

In Chapter 3, based on the motivation that was presented during the introduction of this thesis, and on the existent state-of-the-art solutions, we define the main objective and goals of this work.

In Chapter 4, we present the developed work, and highlight its main contributions. In the second section, we introduce the implemented tunable matching network (TMN), based on switched shunt stubs, that is fully described in the paper of appendix A. The third section presents a novel technique that allows to measure the output impedance of PAs without introducing prohibitive losses. This technique is completely described and explained on the paper of appendix B. On the fourth section we introduce a new concept to compensate the performance of SSPA, without introducing additional OMN losses. The proposed technique is based on the correct variation of the transistor's  $V_{DS}$ . This concept was validated for single-ended PAs, as shown in the papers of appendices C and D. Later, it was also expanded for DPA operation, where it was shown to improve the back-off (BO) and full power (FP) amplifiers' performance, as shown in appendices E and F.

In Chapter 5, the innovative contributions of the developed work are summarized and the published papers are enumerated.

Lastly, Chapter 6 identifies the main conclusions of this PhD thesis and in Chapter 7 we propose relevant next steps to continue this research topic, and improvement tips for the developed prototypes.

# Chapter 2 State-of-the-Art

This chapter presents the most recent findings on load insensitive PA topologies, and the most recently developed techniques that can be included in PA designs to improve their load insensitiveness. The first section of this chapter describes some PA architectures that are, naturally, more insensitive to load variations. On the second section, various types of matching networks with isolation or compression characteristics are shown, and its possible implementation on PAs OMNs is discussed. Lastly, on third section, some compact and low loss impedance measurement techniques are described, and evaluated for application at the output of high power amplifiers.

#### 2.1 Load Insensitive PA Architectures

As previously explained, load insensitive PAs have great value for next generation MIMO transceivers and many other applications. Typical architectures and classes of operation are heavily affected by dynamic load variations, as shown in [9–11]. During this section various state-of-the-art load insensitive PA designs will be introduced and briefly described.

#### 2.1.1 Quasi-Load Insensitive Class E

Class E amplifiers have been widely studied during the last years, mainly because of their high conversion efficiency. In [14], a variable slope operation mode was analyzed. This is a more general class E operation, which forces a switching  $\left(t = \frac{2\pi}{w}\right)$  zero voltage condition, as defined in equation (2.1), while allowing a variable slope condition  $(k \neq 0)$ , as presented in equation (2.2) for the operating frequency, w, and drain voltage,  $V_{DD}$ . This allows for more relaxed designs while maintaining high efficiency. In [15], different modes of operation were also deduced as a function of the resonance factor, q. This factor, defined in equation (2.3), represents the ratio between the resonance frequency of the class E parallel LC tank and the operating frequency, w.

$$V_c\left(\frac{2\pi}{w}\right) = 0\tag{2.1}$$

$$\frac{dV_c(t)}{dt}_{\left(t=\frac{2\pi}{w}\right)} = wV_{DD}k \tag{2.2}$$

$$q = \frac{1}{w\sqrt{LC}} \tag{2.3}$$

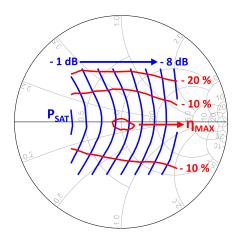

Later, in [16] and [17], Qureshi *et al*, using the conditions derived in [14] and [15], shown that for a q = 1.3, the class E operation maintains optimum efficiency over a wide range of load resistances (purely real output impedances). In fact, when the design parameters are chosen for this specific value of q, the efficiency load pull contours become aligned with the real axis of the Smith chart. Therefore, optimum efficiency is achieved for real loads, as shown in Figure 2.1. The authors named this particular operation as quasi-load insensitive (QLI) class E, and it was demonstrated to be very useful for the design of Doherty and Outphasing PAs, due to the high efficiency achieved throughout the dynamic load modulation (DLM).

However, a QLI class E cannot maintain high efficiency when applied to general load variations, where the load can also become complex. A single ended QLI class E is also unable to maintain the output power constant for real load variations, since the output power contours are perpendicular to the real axis of the smith chart, as shown in Figure 2.1.

Figure 2.1: LP analysis of a class E PA based on the design equations for a q = 1.3. Drain efficiency in red and output power in blue.

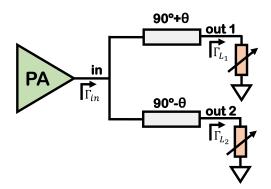

#### 2.1.2 Balanced PAs

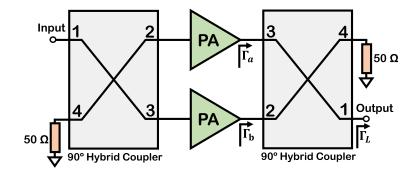

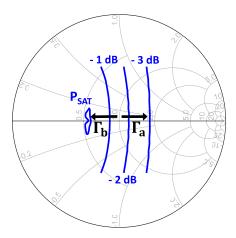

Balanced PAs, as shown in Figure 2.2, composed by two amplifiers and two quadrature couplers, are known to be insensitive to load variations in terms of output power and gain. It can be shown that, for an hybrid coupler defined by the S-parameters of equation (2.4), the reflection coefficient observed by each of the amplifiers composing the balanced PA has opposite phase for any output load variation, as presented in equation (2.5). Therefore, each amplifier will experience load variations with equal amplitude but opposite phase. Consequently, if the PAs are not designed for the maximum power load, the output power of one PA will decrease, while the other's will increase, producing a constant combined output power. In figure 2.3 the output power LP contours and impedance variation of each PA is shown for better visualization of the phenomenon.

Figure 2.2: Balanced PA block diagram.

$$[S] = \begin{bmatrix} 0 & \frac{e^{-j\frac{\pi}{2}}}{\sqrt{2}} & \frac{e^{-j\pi}}{\sqrt{2}} \\ \frac{e^{-j\frac{\pi}{2}}}{\sqrt{2}} & 0 & 0 \\ \frac{e^{-j\pi}}{\sqrt{2}} & 0 & 0 \end{bmatrix}$$

(2.4)

$$\Gamma_a = \Gamma_L \ and \ \ \Gamma_b = \Gamma_L e^{-j\pi} \tag{2.5}$$

Figure 2.3: Output power LP contours and opposite phase load variations, which correspond to the  $\Gamma$  seen by each amplifier composing the balanced PA.

In [18], the authors designed a balanced silicon-germanium (SiGe) heterojunction bipolar transistor (HBT) amplifier. It operates at 835 MHz with an output power of 28.5 dBm and a single tone PAE of 51%. The PA maximum output power and gain variations are 1.5 dB under a load mismatch correspondent to a maximum VSWR of 4:1.

A balanced architecture was also used in [19] and [20]. The designed complementary metal-oxide-semiconductor (CMOS) amplifier operates at 1.95 GHz with a maximum output power of 26.4 dBm and a peak PAE of 35 %. In this case, the load sensitivity analysis was performed for a VSWR of 2.5. The obtained gain variation was 1 dB for the balanced PA, while each single-ended amplifier composing it presented a 6 dB variation for the same load mismatch.

However, for unmatched output loads, the isolation port of the quadrature coupler can receive power that is dissipated on a dummy load, reducing the efficiency. In [21] the authors included an RF-to-dc rectifier between the isolation port of the coupler and the  $V_{DS}$  source to restore the power that would be dissipated at the isolation load. For a 50  $\Omega$  output load, the amplifier's single tone output power was 37 dBm with 65 % of PAE, at 836.5 MHz. Using this technique, the amplifier's efficiency variation (at 25 dBm of output power) was reduced by 4 % for a 2:1 VSWR circle and by 6 % for 4:1. This technique was proven to be very advantageous to reduce the load mismatch sensitivity of balanced amplifiers in terms of efficiency.

#### 2.1.3 Digital Doherty PAs

DPAs are widely used in telecommunication systems, operating with high PAPR signals, due to their improved BO efficiency. However, their analog typical implementation has several disadvantages, mainly due to imperfect interaction between the carrier and peaking amplifiers, such as non-optimal phase delays or gain unbalances. Multi-input DPAs have been proposed to solve this problem. In these amplifiers the amplitude and phase of the input signals can be controlled independently, providing another degree of freedom, to achieve the best possible performance. Since their DLM can be digitally controlled, it can also be explored to dynamically compensate output load variations.

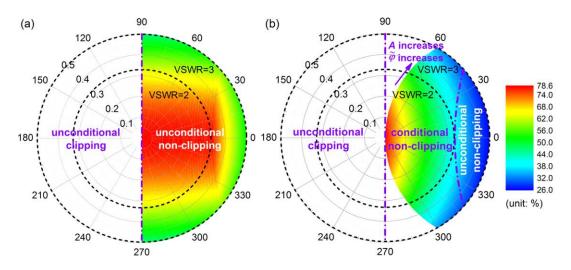

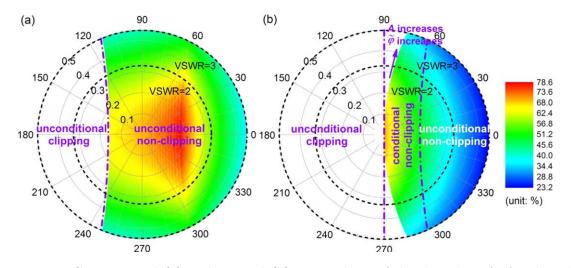

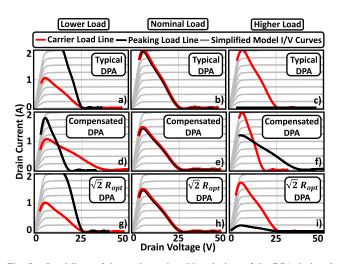

In [22], the authors demonstrated that by varying the relative phase and amplitude of the carrier and peaking input signals, the performance degradation caused by non-optimal loading can be mitigated. For higher than optimal output loads, which are inverted and seen as smaller by the carrier amplifier, the peaking load modulation effect must be reduced by decreasing the peaking maximum current. Thus, the carrier FP load is not decreased below its optimal value. However, the amplifier's BO level is reduced, due to the decreased peaking and carrier amplifier currents ratio and, consequently, reduced load modulation. This compensation effect can be seen in Fig. 2.4 and Fig. 2.5, for FP and BO, respectively. In Fig. 2.5, for BO, the compensation is much less effective, due to the BO level reduction, as explained before.

Figure 2.4: Compensated (a) and original (b) LP analysis of the digital DPA, for FP operation, from [22].

Figure 2.5: Compensated (a) and original (b) LP analysis of the digital DPA, for the 3dB OBO level, from [22].

On the other hand, for lower than optimal output loads, the carrier will see higher loads and consequently a stronger peaking load modulation would be necessary to reduce the load further. For this case, the compensation is done by increasing the peaking current. However, this can only be done during back-off operation, since the peaking is not yet providing its maximum RF current. In this scenario, the peaking current reaches its maximum value before FP, and so, after this point the carrier amplifier will become saturated by voltage at the transistor's triode region. This effect is also shown in Fig. 2.4 and Fig. 2.5, where the authors identified the left part of the Smith as an unsafe voltage clipping area and did not characterize the amplifier for these loads. However, this region can be reduced by increasing the peaking current capability (or reducing the carrier maximum current level). This allows to further reduce the carrier load, and prevent it from voltage clipping, as shown in Fig. 2.6, where the authors considered an asymmetrical DPA with a peaking device size correspondent to twice the carrier size.

Figure 2.6: Compensated DPA FP (a) and 3dB OBO (b) DE, from [22], for an asymmetrical DPA.

So, for higher than optimal output loads, the DPA efficiency can be compensated at FP, by reducing the carrier load modulation, however the BO level is reduced and the output power decreased, due to the lower peaking contribution. Note that, in Fig. 2.6 b), the efficiency appears to be compensated at BO, for higher loads, because it is analyzed only for the 3 dB level. However, instead of reducing the load modulation, if we increase the carrier device size, the BO performance and full power level can also be restored. For this compensation method to be effective, the carrier maximum current must change depending upon the load, thus, for the nominal load only part of the available device current capability should be used.

In [23], the authors present a DPA where both the carrier and peaking drain current capability and phases can be adjusted using switched parallel transistors at the output stage, and tunable phase delay lines at the input, respectively. This design grants a good performance compensation for higher than optimal loads, but they go a step further, and design a combiner that allows to change the carrier and peaking roles to compensate the other "half" of the Smith chart, i.e. smaller than optimal loads. The reconfigurable series/parallel DPA combiner is based on a quadrature coupler, which includes a switch at the isolation port to change the operation mode. Moreover, the bias voltage sources are adaptive so the gate biasing is also interchangeable between the devices. The authors can achieve a worst-case output power and FP PAE degradation of 1.7 dB and approximately 10 %, respectively, for loads across a 3:1 VSWR circle. Note also that the drain current capability of the carrier/peaking devices is set to approximately half of the maximum value for operation with a 50  $\Omega$  nominal load, as expected.

### 2.2 Isolation at OMN

None of the analyzed PA architectures is completely load insensitive in terms of efficiency, gain and output power. Therefore, since some performance degradation is still expected, it may be helpful to further improve the load insensitiveness by increasing the isolation between the PA and its output load. For this purpose, during this section, various TMN topologies and techniques are described, and their possible application on PA OMNs is discussed.

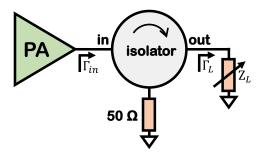

### 2.2.1 Magnetic Isolator

The typical magnetic isolator between the PA and its load, as shown in Figure 2.7, is still used in modern systems. Its ideal S-parameters are presented in equation 2.6. This ideal isolator delivers the incident wave to the antenna, and, in case of any load mismatch, the reflected wave is entirely delivered to the isolation load. Therefore, the amplifier do not see non-optimal load variations. However, note that real isolators have considerable insertion loss (IL) and finite isolation. Moreover, since the reflected power is dissipated at a dummy load, for large mismatch levels, the compound efficiency is greatly reduced and the delivered power to the load is decreased.

Another problem, which is very decisive for telecommunication applications, is that typical isolators are difficult to integrate in MMICs, and the RF chain of future networks will probably be fully integrated in order to reduce implementation costs. To avoid large and costly MMICs or big and heavy hybrid circuits, an effort is being made in the research for different solutions. Notice that, in order to be competitive, these solutions must protect the PA, providing satisfactory isolation, and have an acceptable IL. Unfortunately, most of the state-of-the-art integrated active isolators still have very high IL ( $\approx 2.5$  dB), dramatically reducing the compound efficiency [12, 24, 25].

Figure 2.7: PA connected to the output load through an isolator, in this example  $Z_0$  is equal to 50  $\Omega$ .

$$[S] = \begin{bmatrix} 0 & 0\\ 1 & 0 \end{bmatrix}$$

(2.6)

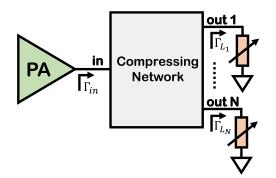

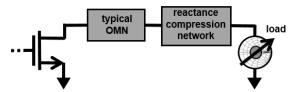

### 2.2.2 Compression Networks

Compression networks are capable of reducing the impedance variation at one port. However, it can be proved that, for having compression with passive and reciprocal networks they must have more than 2 ports, as shown in Figure 2.8. For this case, the input reflection coefficient,  $\Gamma_{in}$ , can be smaller than all the output ones,  $\Gamma_{L_1} - \Gamma_{L_N}$ , with  $N \geq 2$ .

Figure 2.8: (N+1) port compression network.

One approach that has been widely explored is the network presented in Figure 2.9, based on two parallel reactive branches, one inductive and other capacitive. This network can compress load variations as long as they are equal and synchronous at both output ports [26]. It was firstly implemented in [26], with lumped elements and applied to the rectifier stage of resonant dc-to-dc converters. The objective was to improve the conversion efficiency by reducing the load variation seen by their transforming stages. The authors were able to compress load variations of 100:1 and 2:1 into 5.05:1 and 1.06:1, respectively.

After, in [27], the authors used an rf-to-dc converter at the isolation port of an outphasing PA combiner. The objective was to restore some power that otherwise would be dissipated at the isolation load. However, the rf-to-dc converter input impedance variation decreases the isolation of the PA combiner. In order to reduce this load variation, a compression network was added to the rectifier stage of the converter. The implemented system improved the overall efficiency of the outphasing PA from 17.9 % to 42 % under a 16-quadrature amplitude modulation (QAM) signal with a PAPR of 6.5 dB.

Figure 2.9: Transmission line compression network.

Later, in [28], this compression network was implemented using transmission lines, as shown in 2.9. The authors have achieved a compression of 6.7x, from an original 20:1 load variation to a compressed value of 3:1. These transmission line compression networks (TLRCNs) raised the interest of researchers due to its easier implementation at higher frequencies, and possible use on various applications, such as microwave rectifiers [29].

For the problem presented in this PhD thesis, TLRCNs would be tremendously beneficial. However, in order to use them, at least two independent and identically varying output loads are necessary. So, for the envisaged applications, TLRCNs are not straight forward to implement, requiring the connection of one PA to two identical loads with synchronous variations.

### 2.2.3 Tunable Matching Networks

TMNs perform an impedance matching that can be dynamically modified by adjusting variable components, controlled by analog or digital inputs. During this section, the use of TMN techniques at the OMN of amplifiers, as shown in Figure 2.10, will be discussed.

Figure 2.10: PA design including a tunable OMN.

The objective of tunable output matching networks (TOMNs) is to adjust the load presented to the transistor in order to achieve better performance for operation under specific environments. They have been successfully used for different purposes, such as:

- perform DLM, in order to improve the BO performance of amplifiers without using more complex PA architectures, such as DPAs or outphasing amplifiers;

- keep the load presented to the transistor constant, in order to maintain the PA performance under output load variations;

- change the frequency behavior of the PA to switch between different working frequency bands.

For the application presented on this PhD thesis, TOMNs are useful to restore the optimal device impedance under operation for non-optimal output loads, thus improve the PA performance under this scenario. Therefore, the control inputs of such networks should be dependent on the output mismatch level. Then, in order to make matching networks adjustable, it is necessary to dynamically change some of their components' values. Transmission lines length and width cannot be varied easily and coils are not very good at higher frequencies. However, the impedance matching of networks can be changed by using variable capacitors, variable length stubs or switched parallel transmission lines.

In what concerns variable capacitors, there are many different available technologies, as for example, varactors and barium strontium titanate (BST) capacitors. Switches can also be used to implement variable capacitor banks, using various fixed value capacitors, as shown in Fig. 2.11.

Figure 2.11: Example of a widely used capacitor bank circuit topology.

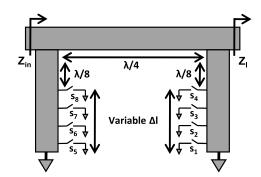

The same switch technologies can also be used to implement switched variable length stubs or switched parallel transmission lines. For example, in [30], the authors change the characteristic impedance of transmission lines by using switches to connect various lines in parallel or to change the ground plane of these microstrip lines. The length variation of shunt stubs can also be used to change their inductive or capacitive input impedance. This can be done by using shunt switches that change the effective length of the stub, as shown in Fig. 2.12.

Figure 2.12: Scheme of a variable length stub.

Concluding, TMNs can be implemented with many different topologies and using various components and/or technologies. The isolation capability is obtained by dynamically changing the impedance transformation, however, further research is necessary on the added losses of these networks and on the used variable capacitors or switching elements. Varactors are known to suffer from non-linearity effects and require power from the control source. microelectromechanical systems (MEMS) switches offer the lowest losses, however, they still need improvement in the manufacturing process and suffer from reliability issues. CMOS switches are reliable and easy to integrate but need further research in order to reduce their losses.

Following, we present some practical implementations. Although they are used with different objectives, the aim is to evaluate the advantages and disadvantages of each technology, considering the possibility to implement them on the application that is presented during this PhD thesis.

### Varactors

Varactor diodes are used as analog variable capacitors, in which the capacitance can be continuously changed by the inverse voltage applied to its terminals [31]. Therefore, TOMNs implemented with varactors can be continuously varied, while switched implementations only allow for step variations. However, varactors characteristic capacitance versus voltage is non-linear, requiring for more complicated characterization processes and control circuits. Under large signal operation they can suffer from linearity issues due to the undesired self-bias that causes a capacitance variation. Moreover, high power varactors require high control voltages (up to 70 V) and a non negligible control power [32].

In [33], the authors implemented a varactor based TOMN in order to realized a multiband class AB PA with high back-off efficiency. The amplifier could be tuned to work from 900 MHz to 2100 MHz with more than 30 % of efficiency at 10 dB of output power backoff (OBO). The disadvantage of this design is the OMN extra IL. Depending on the output power, the losses can vary between 1 dB and 2.5 dB, which corresponds to 12 % and 30 % of efficiency degradation, respectively.

In [34], a varactor based TOMN was also explored for DLM of PAs. The authors proposed the design of a 1 GHz class E laterally-diffused metal-oxide semiconductor (LDMOS) PA with improved back-off efficiency. More than 20 % of improvement at 10 dB of OBO was expected considering the optimal load modulation and a lossless network. However, the measured results shown only 10 % of improvement at the same power back-off level, and more than 0.4 dB of losses in the varactors.

#### **MEMS** Switches

MEMS switches behave as micrometer mechanical relays. They also have metal contacts, as seen in Figure 2.13, however, they are actuated by electrostatic force instead of electromagnetic force. Due to the mechanical relay-like action, they have low IL, high isolation and broadband operation, which are great advantages for the design of tunable RF matching networks [35].

MEMS switches have been used to select different capacitors and realize a frequency reconfigurable OMN [36]. In this work, the network was used to design a frequency reconfigurable PA that can operate in different bands between 8 GHz and 12 GHz.

In [37], the authors used MEMS to realize a 5-bit switched capacitor bank and correct the output impedance change due to extreme hand-effects in mobile devices. The PA was implemented at 900 MHz and 1800 MHz for a nominal output load of 50  $\Omega$ , and was able to operate under worst case output impedances of -75 j  $\Omega$ .

In [38], the authors implemented a variable length switched stub with MEMS switches, and designed a TMN capable of covering the entire Smith chart. Unfortunately, no comments were made about the IL in this work.

Figure 2.13: Scheme of a typical MEMS switch structure, from [39].

#### **Transistor Switches**

Transistors are also used to implement switched matching network designs. These switches impose a small resistor,  $R_{on}$ , when set ON, and a small capacitor,  $C_{off}$ , at the OFF state. For a predetermined technology, the  $R_{on}$  can be decreased at the expense of increasing  $C_{off}$ , or vice-versa, but the  $[R_{on} \cdot C_{off}]$  value is constant and independent of the gate width, [40]. Based on this benchmark metric, different CMOS field effect transistor (FET) technologies have been tested, and are presented in table 2.1.

| Technology           | $R_{on}[\Omega\cdot mm]$ | $C_{off}[fF/mm]$ | $R_{on} \cdot C_{off}$ |

|----------------------|--------------------------|------------------|------------------------|

| $0.5-\mu m pHEMT$    | 1.5                      | 240              | 360                    |

| $0.15-\mu m pHEMT$   | 1.5                      | 290              | 435                    |

| $0.5$ - $\mu m SOS$  | 2.8                      | 270              | 756                    |

| $0.25$ - $\mu m SOS$ | 1.6                      | 280              | 448                    |

| $0.28$ - $\mu m$ SOI | 1.2                      | 330              | 396                    |

Table 2.1: CMOS FET switches state-of-the-art, from [40].

In [41], the authors have implemented a TOMN in order to realize DLM and achieve higher back-off efficiency. They have implemented a switched capacitor bank using silicon on insulator (SOI) CMOS switches. The drain efficiency of the amplifier has been improved by 34 % for 6 dB of OBO, at 2.4 GHz.

In [42], the authors also used SOI CMOS switches to implement a capacitor bank. In this work the objective was to correct linearity issues. The implemented PA was capable of improving the adjacent channel power ratio (ACPR) by 13.7 dB at 1.95 GHz, for an output power of 28.3 dBm.

In [43], the authors compensated the PAE and output power degradation due to antenna mismatch for a maximum reflection coefficient of 0.3. They used CMOS switched capacitors to implement a TOMN for a 2.4 GHz PA, improving the minimum PAE by 14 % and the output power by 3 dB.

In [44], the authors develop tunable transmission lines, based on variable length switched stubs, using MOS and Bipolar switches.

### 2.3 Compact Impedance Measurement

Most of the described TMN design techniques require analog or digital control signals, which depend on the actual PA output load. Some of the presented PA architectures also require load-dependent reconfigurable circuits and load-dependent input RF signals. Therefore, it is imperative to have real-time information about the output load of the PA. In some cases, as, for example, massive MIMO antenna arrays, where the load variation depends on the mutual coupling between different antenna elements, the load variation can be predicted or pre-characterized by knowing the selected beamforming angle. However, for most of the described applications, this pre-characterization can be difficult or the load variation can be signal dependent. Consequently, it is necessary to, directly or indirectly, measure the output impedance that is actually presented to the PA in real-time.

There are various techniques and commercial equipment capable of measuring the impedance of RF circuits. However, for this application, where the PA output load needs to be measured in real-time and for high power levels, as shown in Fig. 2.14, it is more adequate to design dedicated impedance measurement circuits taking into account specific requirements:

- The acquisition hardware must have **very low IL**. This is an extremely important characteristic for this application, since the circuitry losses added between the PA and its load reduce the delivered output power, and, consequently, have a major detrimental impact on the overall PA efficiency;

- The measurement algorithm should have **low complexity**. Therefore, it will run faster in low cost microcontroller units (MCUs), and also use less power;

- The impedance measurement system should be **low cost**. This is specifically important in systems where various measurement units are necessary.

Figure 2.14: Typical application of an impedance measurement circuit between the PA and its output load.

### 2.3.1 Coupler Based

The latest vector network analyzers (VNAs) are complex systems, and also very bulky and expensive. Some implementations are more miniaturized now, but, even in this case, they are still composed of many sub-circuits and sub-systems, which increase the system cost and add complexity. In [45], the authors developed an Arduino-based miniaturized VNA. They have measured the reflection coefficient of an iPhone 5 antenna, for mismatch levels up to a VSWR of 10.0, and achieved a worst-case amplitude and phase measurement errors of 0.2 dB and  $4^{\circ}$ , respectively. However, the used couplers introduce a worst-case IL of 0.36 dB, which is too high for higher power applications. The impedance measurement time varies between some 100 ms and 20 ms.

Throughout time many other measurement systems, also based on bi-directional couplers, have been developed. However, the simplest ones, with lower IL and more compact implementations, have low accuracy. Moreover, some of them are not able to measure both the amplitude and phase of the reflection coefficient. These simpler ones are designed to measure only the amplitude or phase information. More accurate measurement solutions are based on more complex designs, leading to scalability issues and, consequently, an increased production cost.

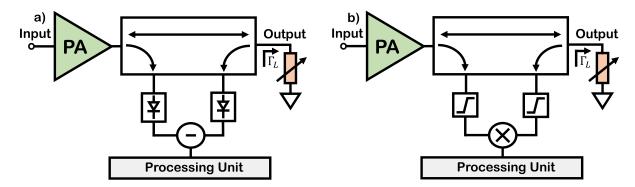

In [46], the authors use a bi-directional coupler, two RF power detectors, and an analog subtractor to measure only the reflection coefficient amplitude, similarly as illustrated in the block diagram of Fig. 2.15 a).

Figure 2.15: Typical system architecture for the measurement of the reflection coefficient amplitude and phase, in a) and b), respectively.

In [47], the authors were able to measure the reflection coefficient phase. However, they were not interested in measuring amplitude variations. The developed system is based on a bi-directional coupler, a  $90^{\circ}$  fixed phase shifter, two amplitude limiters, and an analog multiplier, as shown in Fig. 2.15 b).

In [48], the authors used two separated circuits to measure both the amplitude and phase of the reflection coefficient. These circuits are based on the same principle as the ones described before, on [46] and [47]. However, since the phase measurement circuit is based on comparators, the authors were only able to detect if the load was inside one region of the Smith chart. This design choice leads to increased complexity and scalability issues for higher resolution measurements, due to the necessity for more hardware to reduce the Smith chart detection regions.

In [49], the authors calculated the reflection coefficient amplitude and phase and compared the obtained values with a fixed reference. The amplitude and phase references were measured, using similar circuitry, from the incident and reflected waves at the output of a reference PA, that is fed with the same signal and operates for a fixed reference load. It was claimed that this architecture performs better for measurements using non-constant envelope signals. However, the circuit is very complex and it requires one extra amplifier, operating for a dummy fixed load.

### 2.3.2 Sampled Line Based

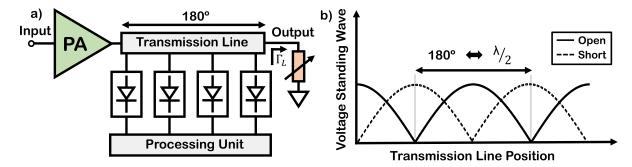

Some other measurement systems that have been developed a long time ago, as, for example, slotted lines, are bulky and composed of many mechanical moving parts. The biggest disadvantage of these older measurement systems is that some of the parts must be fabricated with very precise machining processes, which are expensive. Moreover, the measurement is mostly done manually, which is time consuming. The measurement is based on the voltage standing wave, which is obtained by measuring the voltage on several positions along a  $\lambda/2$ line. Then, the standing wave information (amplitude, average value and minimum position) is used to compute the output load. Some other approaches, as sampled lines [50], are based on the same principle, but, instead of using moving components along a line, the voltage is sampled by various fixed power detectors placed on a  $\lambda/2$  line, as shown in Fig. 2.16. However, since various detectors are required, the introduced IL is, normally, too high for the required high efficiency applications [50].

Figure 2.16: a) Sampled line typical topology. b) Normalized voltage standing wave pattern for a short circuit termination (dashed) and open circuit termination (continuous).

Six-port reflectometers can also be implemented with similar sampling architectures. Using specific algorithms, it is possible to compute the reflection coefficient from, at least, four sampling ports. This measurement technique can be implemented with various power detectors placed along a line, as sampled lines, and also from voltage samples obtained directly at different locations of the PA OMN [51], [52]. However, the OMN IL is usually increased too much due to the added power detectors, and, in some cases, the measurement accuracy is worse than it is on coupler based solutions. Moreover, the measurement circuit needs to be closely designed with the amplifier OMN, increasing the OMN complexity and adding extra constrains to its design.

# Chapter 3 Objective and Main Goals

From the presented state-of-the-art we conclude that both the academia and industry already developed various PA architectures and other techniques, such as TMNs, that can be used to reduce the amplifier's performance degradation for operation under non-optimal loads. However, none of the developed PA architectures is insensitive in terms of both output power and efficiency, for real and also complex output loads. TOMNs can be used to further increase load insensitiveness of amplifiers, by increasing the isolation provided by the OMN, but variable components introduce considerable losses on the matching networks, reducing the total amplifier's efficiency.

Based on this state-of-the-art analysis and on the motivation behind the work, we present the main objective of this doctoral program. The aim is to study and develop a load insensitive PA topology, or novel methods to turn the existing architectures more insensitive to output load variations. To achieve this overall objective the following specific goals are defined:

- The PA performance degradation, for operation under non-optimal loads, should be studied and quantified, for existing PA architectures. The key figures of merit to evaluate this performance degradation are the energy conversion efficiency and the output power capability, which are of paramount importance in all PA applications. Moreover, the linearity should also be considered, which is a decisive factor for telecommunication applications;

- Tunable matching networks (TMNs) will also be studied and evaluated in terms of losses and matching range. Their possible implementation in the OMN of PAs will be considered, in order to further reduce the load variation seen by the used transistors.

- Based on the identified problems for each PA architecture, or class of operation, novel techniques should be developed to reduce the output load sensitivity of amplifiers. These techniques should be included in the design of a single-ended PA and validated with simulations and laboratory measurements.

- The developed techniques should be extended for more complex PA architectures with high efficiency at BO, such as Doherty or Outphasing amplifiers, so that, they can be implemented in telecommunication applications, where high PAPR signals are used.

- The final aim is to design a complete PA system that should be insensitive to unpredictable output load variations. Ideally, this system should not depend on any external

hardware, being able to keep its performance by itself. From the user perspective, it should behave as if it were always operating for the nominal load, providing a seamless performance. Since it should work for predictable and unpredictable load variations, an impedance measurement solution must also be designed to track the load and provide the amplifier stage with the necessary feedback.

### Chapter 4

## Load Insensitive Power Amplifier Solutions

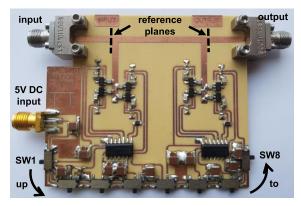

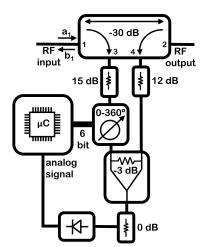

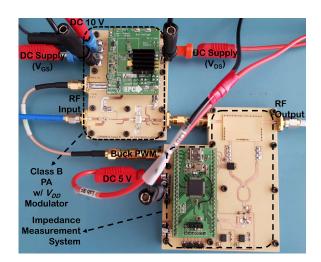

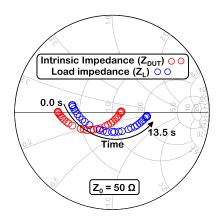

This chapter presents the work developed during this PhD thesis, highlighting the main innovations. As previously said, the main objective of this PhD work is to develop a novel load insensitive PA architecture. This was accomplished by carrying out various steps towards the established final objective. In the beginning, we have started by studying the existing solutions, and the actual PA performance degradation for various classes of operation, which was crucial to implement our first prototype, based on TMNs. Then, we realized that it was very important to develop a low-loss impedance measurement system, and so, we came up with an innovative solution based on a MCU, which was adequate for implementation with various load compensation techniques due to the possibility of generating a diverse range of load-dependent control outputs. Lastly, we have developed a novel technique, based on the PA  $V_{DS}$  variation, to compensate the degradation caused by the studied PA non-optimal loading. Finally, a complete QLI DPA system was developed, including:

- real-time tracking of the DPA output stage load;

- compensation of the efficiency and output power degradation by controlling the transistors'  $V_{DS}$ ;

- an adaptive input stage to adjust the input RF signals, keeping the Doherty behavior and increasing the linearity under non-optimal loads;

- a common mode gain adaptation to keep the small signal gain constant under output load variations.

This chapter is organized as follows. In Section 4.1, we evaluate the advantages and disadvantages of a quasi load insensitive PA architecture combined with a low loss TMN based on adjustable length stubs. In Section 4.2, we introduce a dedicated compact and low-loss impedance measurement circuit that can track the amplifier's output impedance in real-time. Section 4.3.1 presents a novel technique to increase PAs performance under non-optimal loading based on the optimal transistors'  $V_{DS}$  variation, which was derived for single-ended class B amplifiers. Finally, Section 4.3.2 presents the extended application of te derived transistors'  $V_{DS}$  variation to DPAs, and also the complete QLI DPA system.

### 4.1 Tunable Matching Network

After analyzing the existing literature on load insensitive PA architectures and TMNs, we had the idea of combining a PA architecture that is already robust to load variations with a TMN, to increase the PA load insensitiveness. So, in this first part of the work, we studied different classes of operation and we have opted for a QLI class E PA due to its high efficiency under real loads. Then, the idea was to use a simpler TMN, which was required to transform any load inside the considered VSWR circle into real loads. This way, the complexity of this network is lower, since it is only used to remove the imaginary part of the output loads, and, consequently, it can be designed with less losses.

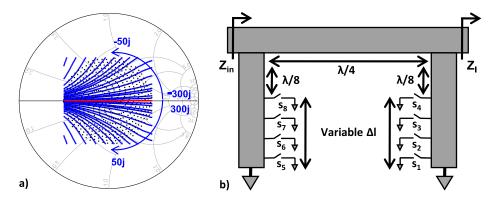

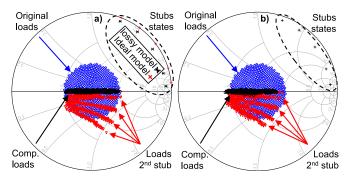

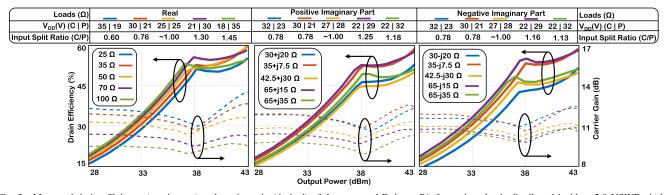

The designed network, which we named "reactance compression network (RCN)", is built by adding a variable parallel element to the complex output load. The necessary parallel reactance was calculated (Appendix A) for each load inside the worst-case considered VSWR circle and is shown in Fig. 4.1 a). The worst-case load variation considered for compensation was a 2.1 VSWR circle, which is a good estimate of the actual load variation obtained in state-of-the-art 5G massive MIMO antenna arrays [53], which is one of the most important applications for the developed work.

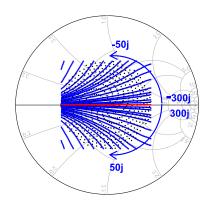

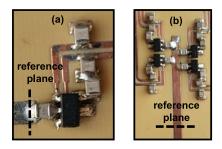

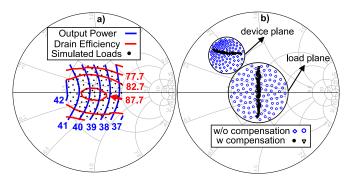

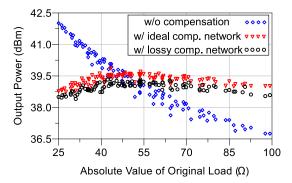

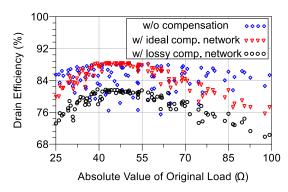

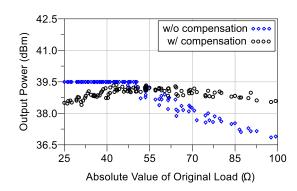

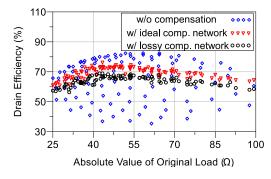

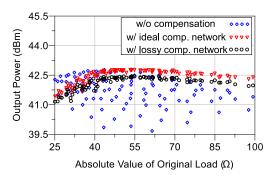

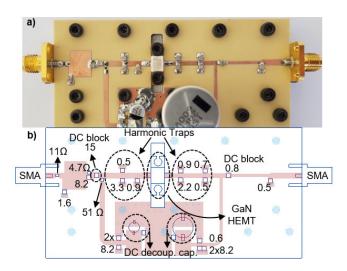

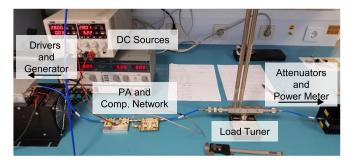

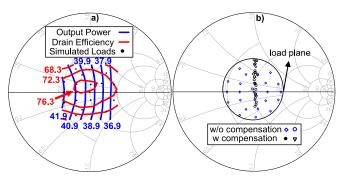

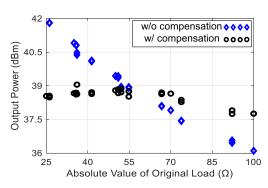

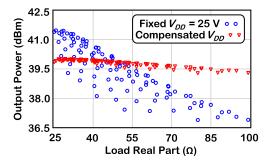

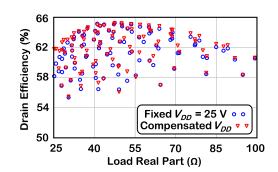

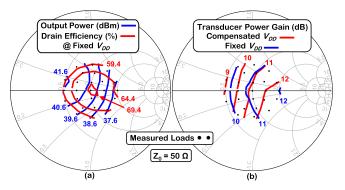

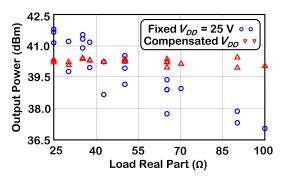

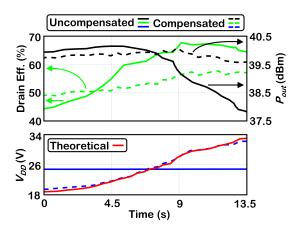

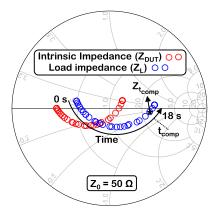

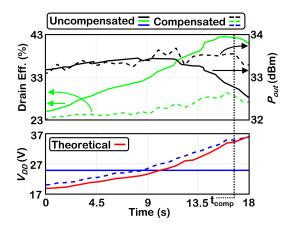

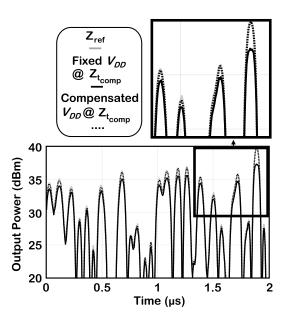

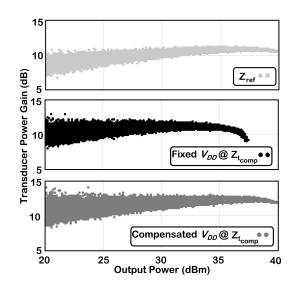

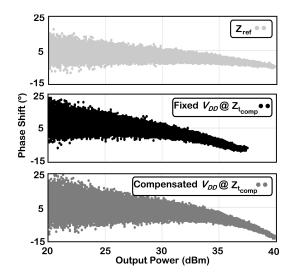

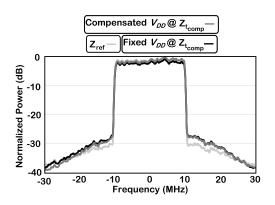

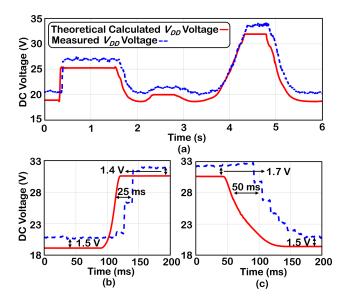

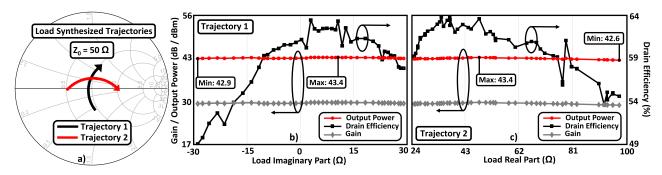

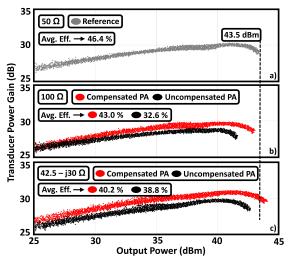

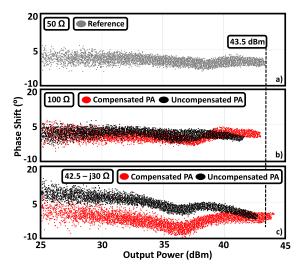

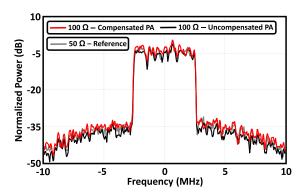

Figure 4.1: a) Contours of the calculated necessary parallel reactance to eliminate the imaginary part of each load. b) Schematic diagram of the idealized compensation network.