# Single Mach-Zehnder Interferometer based Optical Boolean Logic Gates

Cláudia Reis,<sup>1,\*</sup> Tanay Chattopadhyay,<sup>2</sup> Paulo André,<sup>1,3</sup> and António Teixeira<sup>1,4</sup>

<sup>1</sup>Instituto de Telecomunicações, Campus de Santiago, 3810-193 Aveiro Portugal <sup>2</sup>Kolaghat Thermal Power Station, WBPDCL, 721137, West Bengal, India

<sup>3</sup>Departmento de Física, Universidade de Aveiro, Campus Universitário de Santiago, 3810-193 Aveiro, Portugal

<sup>4</sup>Departmento de Electrónica, Telecomunicações e Informática, Universidade de Aveiro, Campus Universitário de Santiago, 3810-193 Aveiro, Portugal \*Corresponding author: <u>creis@av.it.pt</u>

In this paper, we demonstrate different optical logic gates using a single Mach-Zenhder interferometer (MZI) with controlled phase modulators in each arm. The operational conditions to obtain 16 optical logic circuits, using the same design, are investigated and are a result of a constructive or destructive interference process. The proposed configuration presents significant low complexity and high scalability and its feasibility is evaluated through numerical simulations.

OCIS codes: 200.4660; 230.2090

#### 1. Introduction

Optical logic gates have been widely investigated in the last few years since they can be used in a variety of signal processing applications, such as optical bit pattern recognition, optical time division demultiplexing, as well as in optical binary adders and optical counters [1-5].

Several approaches have been proposed up-to-date to demonstrate different optical logic operations and mostly are based on highly nonlinear optical fibers (HNLFs) or on nonlinear effects in semiconductors optical amplifiers (SOAs), integrated or not in interferometric structures [6-11]. SOA-based logic gates schemes although showing high potential for photonic integration present, however, speed limitation and latency, primarily due to the slowly recovery time of the SOAs.

In this paper, we present for the first time, to our knowledge, a novel configuration that provides 16 optical logic operations, based on a single MZI with controlled phase modulators in each arm, without changing the setup scheme. Conventional logical circuits are designed with one output, so each logic operation can only be realized once at a time. This means that the output port can present the '0' logic level, i.e., no light, although the circuit is fed with light signal at its inputs. As an example, for AND operation, the output port is '0' except when the inputs are <1, 1>. Therefore the input data is destroyed during this operation for some input combinations. Data loss can be prevented if is designed a circuit with two outputs, in which one is the complement of the other. The proposed scheme uses both interferometric output ports of the MZI, so every input data can reach any of the ports, with no data loss [12-13]. Since both output ports are complementary, for the same operational conditions we can obtain, simultaneously, two different optical logic gates. The proposed configuration presents very low

complexity and power consumption, and suggests high integration potential. The system performance is investigated through numerical simulations, using the Optisystem® 7.0 software.

This paper is organized as follows: in Section 2, the proposed logic circuit with the mathematical model is presented. In this section, is also described the operational conditions to implement 16 logical operations. The simulation results for each logic gate are presented on Section 3. In Section 4, a discussion regarding the performance feasibility of the different logic operations is realized before and after introducing a thresholder function. Finally, in Section IV the conclusions are drawn.

#### 2. Optical logic gates based on a single MZI

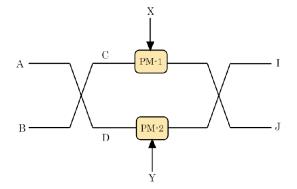

Fig. 1 depicts the proposed configuration of the 16-Boolean optical logic circuit and it consists of a single MZI, with a phase modulator (PM) in each arm.

The operating principle can be explained as follows. When an optical signal is launched into port #A of the 3-dB input coupler, its power is distributed, equally, through both MZI arms, but with a phase shift of  $\pi/2$  between the two branches of the interferometer. Then, the signals experiment an optical phase change caused by phase modulators placed in each MZI arm. The input signals X and Y will program the phase modulators, in order to control the phase change in the arms of the interferometer. The phase modulators are mostly based on the electro-optic effect, in which an electrical field is applied to an electro-optic element, creating a change in its refractive in index [14].

Finally, when the optical signals arise at the output 3-dB coupler, they will suffer another phase shift of  $\pi/2$  and, at the MZI output ports, different output levels are obtained. Therefore, since the 3-dB couplers of the MZI introduce always the same phase shift, the sixteen logic

circuits are obtained by simply adjusting the voltage of the controlled phase modulators in the setup, in order to get the desired optical phase change in the MZI arms.

#### A. Theoretical model

Considering that the path length of the two arms of the interferometer is the same (L), and that both signals present the same wavelength ( $\lambda$ ), the MZI arms have a phase difference  $\Delta\theta$  that can be described by

$$\Delta \theta = \frac{2L\pi}{\lambda} (n_1 - n_2) = \frac{2L\pi}{\lambda} \Delta n = \theta_1 - \theta_2 \tag{1}$$

Assuming that the scattering matrix (also called propagation matrix) of a 2x2 guided-wave coupler is given by [15]

$$\begin{bmatrix} \sqrt{1-\varepsilon} & j\sqrt{\varepsilon} \\ j\sqrt{\varepsilon} & \sqrt{1-\varepsilon} \end{bmatrix}$$

(2)

Then, according to the latter expression, the output fields intensities of the ideal 3-dB input coupler (50/50 coupling ratio, i.e,  $\varepsilon = 0.5$ ) can be calculated as

$$\begin{bmatrix} E_C \\ E_D \end{bmatrix} = \begin{bmatrix} \frac{1}{\sqrt{2}} & j\frac{1}{\sqrt{2}} \\ j\frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix} \cdot \begin{bmatrix} E_A \\ E_B \end{bmatrix}$$

(3)

Considering that the propagation matrix of a phase shifter is given by [16]

$$\begin{bmatrix} e^{j\frac{\Delta\theta}{2}} & 0\\ & e^{-j\frac{\Delta\theta}{2}} \end{bmatrix}$$

(4)

Then the transfer matrix of a MZI can be defined as

$$\begin{bmatrix} \frac{1}{\sqrt{2}} & j\frac{1}{\sqrt{2}} \\ j\frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix} \cdot \begin{bmatrix} e^{j\frac{\Delta\theta}{2}} & 0 \\ e^{-j\frac{\Delta\theta}{2}} \end{bmatrix} \cdot \begin{bmatrix} \frac{1}{\sqrt{2}} & j\frac{1}{\sqrt{2}} \\ j\frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix}$$

(5)

Note that the output coupler has also 50/50 coupling factor.

Equation (5) can be re-written as

$$\begin{bmatrix} \frac{1}{2}e^{j\frac{\Delta\theta}{2}} - \frac{1}{2}e^{-j\frac{\Delta\theta}{2}} & j\frac{1}{2}e^{j\frac{\Delta\theta}{2}} + j\frac{1}{2}e^{-j\frac{\Delta\theta}{2}} \\ j\frac{1}{2}e^{j\frac{\Delta\theta}{2}} + j\frac{1}{2}e^{-j\frac{\Delta\theta}{2}} & -\frac{1}{2}e^{j\frac{\Delta\theta}{2}} + \frac{1}{2}e^{-j\frac{\Delta\theta}{2}} \end{bmatrix}$$

(6)

Knowing that  $e^{j\frac{\Delta\theta}{2}} = \cos\frac{\Delta\theta}{2} + j\sin\frac{\Delta\theta}{2}$ , equation (6) can be simplify and the electric fields of

the output of the interferometer can be calculated as

$$\begin{bmatrix} E_I \\ E_J \end{bmatrix} = \begin{bmatrix} j \sin \frac{\Delta \theta}{2} & j \cos \frac{\Delta \theta}{2} \\ j \cos \frac{\Delta \theta}{2} & -j \sin \frac{\Delta \theta}{2} \end{bmatrix} \cdot \begin{bmatrix} E_A \\ E_B \end{bmatrix}$$

(7)

In the absence of an optical signal in port #B, the output powers can be found by:

$$P_{I} = E_{I} \cdot E_{I}^{*} = \sin^{2} \left(\frac{\Delta\theta}{2}\right) P_{A}$$

$$P_{J} = E_{J} \cdot E_{J}^{*} = \cos^{2} \left(\frac{\Delta\theta}{2}\right) P_{A}$$

(8)

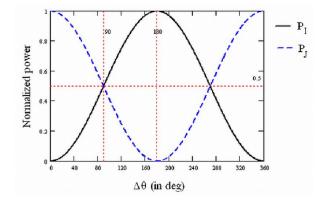

From these equations we can plot the normalized output powers  $P_I$  and  $P_J$  with  $\Delta\theta$ , as illustrated in Fig. 2. From this graph we can conclude that, at  $\Delta\theta = 180^{\circ}$ ,  $P_I =$  maximum and  $P_J =$  minimum. At  $\Delta\theta = 90^{\circ}$ ,  $P_I = P_J = 0.5$ , showing that is possible to vary the output power with  $\Delta\theta$ .

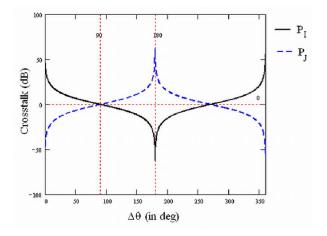

Hence, the crosstalk at the different MZI ports also varies, as illustrated in Fig. 3. Crosstalk is defined by the ratio of the powers at the non-targeted port ( $P_{nt}$ ) and targeted port ( $P_t$ ) of the MZI [17], i.e.

$$XT = 10\log\left(\frac{P_{\rm nt}}{P_{\rm t}}\right) \tag{9}$$

In an optical device, with a good performance, the crosstalk effect should be minimum. With our proposed configuration, we can create different output powers and crosstalk by applying different phases to the phase modulators.

For logical operation, it is not always required that the '0' logic level has a very low (nearly zero) optical power. In fact, we can adjust it by a threshold level, in which above this level we have the logic level '1' and below the logic level '0'. In this paper, we consider a power range between 0.75 - 1 as logic '1' state and 0 - 0.25 as logic '0' state.

#### **B.** 16-logic operation cases

The new concept proposed in this paper uses a very simple logic circuit, and is capable to perform different optical logic gates based on the phase difference between the two arms of a Mach-Zenhder interferometer. The data input signals X and Y will program the phase modulators, in order to control the phase change in the arms of the interferometer.

The operational conditions to implement an AND/NAND optical gate are demonstrated in Table I. When X or Y are equal to 1, the phase modulators introduce, respectively, an additional 300° and 60° in upper and down MZI arm; otherwise no additional phase shift is added. The powers at the output ports, P<sub>1</sub> and P<sub>3</sub>, presented in Table I, are obtained by solving equation (8).

Considering  $P_A$  equal to 1 a.u., when (X:Y) are (0:0); (0:1); (1:0) and (1:1), the powers at port #I are, respectively, 0; 0.25 a.u.; 0.25 a.u. and 0.75 a.u., which correspond to the output logic levels 0;0;0;1. Thus, the output port #I only have the logical value '1' when the input signals (X:Y) are simultaneously equal to 1. This correspond to the AND logical operation (*XY*). Since both output ports are complementary, for the same operational conditions we also obtain, simultaneously, at the output port #J, the NAND logic circuit.

All the possible 16-optical logic gates that can be implemented with the proposed configuration are illustrated in Table II, and they are performed based on the same operating principle described in AND/NAND optical gate. So, by changing the phase at the two arms of a Mach-Zenhder interferometer ( $\theta_1$  and  $\theta_2$ ), it is possible to obtain different logic functions at the MZI output ports, port #I and port #J.

#### 3. Simulation results of each logic gate

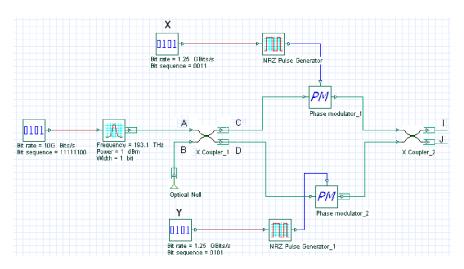

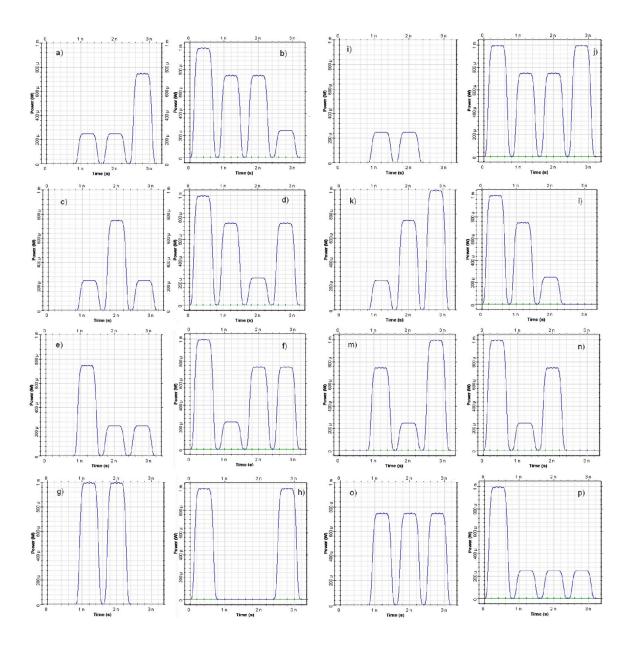

In order to analyze the proposed optical logic circuit, presented in Fig.1, under different phase conditions, without changing the setup design, we simulate the system shown in Fig. 4, using the Optisystem  $\mathbb{R}$  7.0 software. Each optical logic gate is obtained by properly setting the voltage in each phase modulator, in order to get the appropriate phase change that implements the desired logic operation. The input signals X and Y will control the phase modulators, and the data sequences used are X = [0011] and Y = [0101].

At the outputs ports of the MZI, we also introduce two attenuators, adjusted with same attenuation in both arms, in order to set the maximum power at 1mW.

Fig. 5 shows the graphs of simulated data measured from output ports #I and #J, for each logic gate. These results demonstrate that the optical pulse, injected into port #A will suffer a constructive or destructive interference, depending of the phase difference between the two MZI

arms. The phase change is obtained using phase modulators controlled by the input data signals, X and Y. Therefore, the different logic operations are obtained as a result of a combination of the chosen inputs.

The simulated results presented in Fig. 5 also show that the estimated output powers,  $P_I$  and  $P_J$  from Table II, obtained using the theoretical model (equation 8), are in good agreement with the simulated measured curves, which validates our concept.

#### 4. Discussion

Ideally, a 'high' logic level should be exactly equal to '1' and a 'low' logic level should be exactly equal to '0'. However, in real applications, is acceptable a slightly deviation from these ideal logic values.

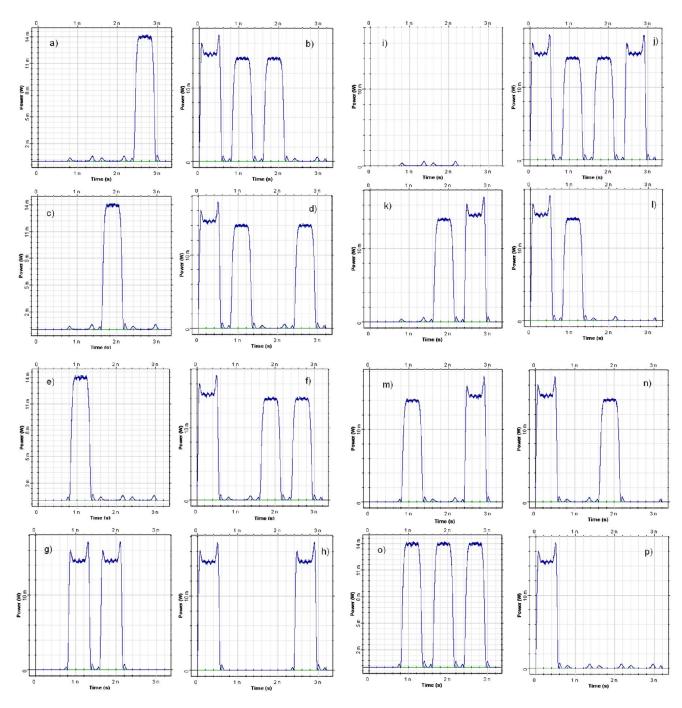

In this paper, we considered values between 0.75 - 1 as the logic 'high' state and values between 0 - 0.25, as the logic 'low' state. However is possible to reduce the variation of the 'high' output levels and suppress the 'low' logic levels shown in Fig. 5, using optical thresholding schemes. The thresholder function can also improve the extinction ratio values of different logic gates. In this context, an optical thresholder scheme [6] is connected by an Erbium Doped Fiber Amplifers (EDFA) to each one of the MZI output ports #I and #J of Fig. 4, in order to investigate the performance of each logic gate. The gain of both EDFAs is set to 22dB and the parameters of the two thresholders are almost the same. Both attenuators have an attenuation of 10 dB in order to guarantee asymmetrical losses. The HNLFs used have low dispersion slope, a fiber length of 0.5km and a nonlinear refractive index of  $2.6 \times 10^{-18}$  m2/W. However, their wavelengths are slightly different: HNLF1 wavelength is 1565nm and HNLF2 wavelength is 1566.6 nm. Fig. 6 shows the simulation results obtained, for each optical logic gate, after the thresholder function is introduced. It is possible to observe an almost complete suppression of the 0 pulses and, although some undesired peaks are presented, the 1 output pulses are almost equalized. Therefore, the two logic levels '0' and '1' are well defined.

The system performance is assessed with the calculation of the extinction ratio (ER) values for each Boolean gate, before and after the thresholder function. In Table III, is possible to observe that after using a thresholder circuit, the simulated ER increased for almost all the cases. The exception cases are the ones that before the thresholder circuit presented already only two optical powers. For these cases, the thresholder function is not needed since the ER achieved is superior to 10 dB. For all the other cases, we observed a significantly improvement in the ER values after introducing the thresholder circuit, since it almost suppresses completely the '0' levels and leads to a stabilization of the '1' logic level.

#### 5. Conclusions

In this paper, we proposed a novel scheme that performs 16-Boolean logic operations based on a single Mach-Zehnder interferometer, using the same design. We showed that through optical phase changes in MZI branches, using controlled phase modulators, is possible to successfully demonstrate different logic operations

We have explained the operation principle of our concept and assessed its performance against several operational criteria, through numerical simulation, which allowed to theoretically confirm our model.

#### Acknowledgments

The authors greatly acknowledge the support provided by the FP7 Network of Excellence project EURO-FOS.

### References

- R. Vilar, J.M. Martinez, F. Ramos, J. Marti, "All-optical DGD monitor for packet-switched networks based on an integrated active Mach–Zehnder interferometer operating as logic XOR gate", Opt. Commun., Vol. 281, No. 21, pp. 5330-5334, Nov. 2008.

- J. M. Martinez, Y. Liu, R. Clavero, A. M. J. Koonen, J. Herrera, F. Ramos, H. J. S. Dorren, and J. Marti, "All-optical processing based on a logic XOR gate and a flip-flop memory for packet-switched networks", IEEE Photon. Technol. Lett., Vol. 19, No. 17, pp. 1316-1318, Sept. 2007.

- 3. L. P.-Li, D. Huang, X. Zhang and G. Zhu, "Ultrahigh-speed all-optical half adder based on four-wave mixing in semiconductor optical amplifier", Opt. Exp, Vol. 14, No. 24, Nov. 2006.

- 4. N. Calabretta, H. Jung, H. Dorren, "All-optical label swapping techniques for optical packets at bit-rate beyond 160 Gb/s", Journal of Networks, Vol.5, No.11, pp. 1343-1349, 2010.

- F. Ramos, E. Kehayas, M. J. Martinez, R. Clavero, J. Marti, L. Stampoulidis, D. Tsiokos, H.Avramopoulos, J. Zhang, V. P. Holm-Nielsen, N. Chi, P. Jeppesen, N. Yan, T.I. Monroy, A. M. J. Koonen, M. T. Hill, Y. Liu, H. J. S. Dorren, R. Van Caenegem, D. Colle, M. Pickavet, and B. Riposati, "ISTLASAGNE:Towards all-optical label swapping employing optical logic gates and optical flip-flops", IEEE J. Lightwave Technol., Vol. 23, No.10, pp.2993-3011, Oct. 2005.

- Y. Miyoshi, K. Ikeda, H. Tobioka, I. Takashi, S. Namiki and K. Kitayama, "Ultrafast alloptical logic gate using a nonlinear optical loop mirror based multi-periodic transfer function", Opt. Exp, Vol. 16, No. 4, pp. 2570-2577, Feb. 2008.

- Y. Ishizaka, Y. Kawaguchi, K. Saitoh, M. Koshiba, "Design of optical XOR, XNOR, NAND, and OR logic gates based on multi-mode interference waveguides for binary-phaseshift-keyed signal", IEEE J. Lightwave Technol., Vol. 29, No. 18, pp. 2836-2846, Sept. 2011.

- Y. Wu and T. Shih, "New all-optical logic gates based on the local nonlinear Mach–Zehnder interferometer", Opt. Exp., Vol. 16, No. 1, pp. 248–257, Jan. 2008.

- Z. Li and G. Li, "Ultrahigh-speed reconfigurable logic gates based on four-wave mixing in a semiconductor optical amplifier", IEEE Photon. Technol. Lett., Vol. 18, No. 12, pp. 1341-1343, June 2006.

- K. Sun, J. Qiu, M. Rochette, L.R. Chen, "All-optical logic gates (XOR, AND, and OR) based on cross phase modulation in a highly nonlinear fiber", ECOC 2009, 3.3.7, Vienna, Austria 2009.

- 11. G. P. Agrawal, "Nonlinear fiber optics", 4th ed., Academic Press, 2006.

- J.Hardy, J.Shamir, "Optics inspired logic architecture", Optics Express, Vol. 15, No. 1, pp-150-165, 2007.

- 13. T.Chattopadhyay, "Optical programmable Boolean logic unit", Applied Optics, Vol. 52, No. 32, pp. 6049-6056, 2011.

- 14. L. Pavesi, G. Guillot, "Optical interconnects: the silicon approach", Springer, 2006.

- 15. R. März, "Integrated Optics: Design and Modeling", Artech House, p. 183, Boston, 1994.

- C.K.Madsen, P.Oswald, M.Cappuzzo, E.Chen, L.Gomez, A.Griffin, A.Kasper, E.Laskowski, L.Stulz and A.Wong-Foy, "Reset-free integrated polarization controller using phase shifters", IEEE journal of selected topics in quantum electronics, Vol. 11, no. 2, March/April 2005, pp-431-438.

- 17. T.Chattopadhyay, "All-optical cross-bar network architecture using TOAD based interferometric switch and using it to design reconfigurable logic unit", Optical Fiber Technology, Vol. 17, No. 6, 2011, pp-558-567.

## Legends

Fig. 1. Schematic diagram of proposed MZI based 16-logical operation circuit. PM: phase modulator

Fig. 2. Variation of normalized output power (a.u.) with  $\Delta \theta$  (in degree).

Fig. 3. Variation of crosstalk (in dB) with  $\Delta\theta$  (in degree).

Fig. 4. Proposed configuration of the optical 16-Boolean logic circuit based on a single MZI.

Fig. 5. Simulated curves for each logic gate. a) XY(AND); b)  $\overline{X} + \overline{Y}(NAND)$ ; c)  $X\overline{Y}$ ; d)

$\overline{X} + Y$ ; e)  $\overline{X}Y$ ; f)  $X + \overline{Y}$ ; g)  $X \oplus Y(XOR)$ ; h)  $\overline{X \oplus Y}(XNOR)$ ; i) 0(False); j) 1(True); k) X; l)

$\overline{X}$ ; m) Y; n) $\overline{Y}$ ; o) X + Y(OR); p)  $\overline{XY}(NOR)$

Fig.6. Simulated curves for each logic gate after thresholder function. a) XY(AND); b)  $\overline{X} + \overline{Y}(NAND)$ ; c)  $X\overline{Y}$ ; d)  $\overline{X} + Y$ ; e)  $\overline{X}Y$ ; f)  $X + \overline{Y}$ ; g)  $X \oplus Y(XOR)$ ; h)  $\overline{X \oplus Y}(XNOR)$ ; i) 0(False); j) 1(True); k) X; l)  $\overline{X}$ ; m) Y; n)  $\overline{Y}$ ; o) X + Y(OR); p)  $\overline{XY}(NOR)$ .

# Figures

Figure 1

# Figure 4

## **Tables**

| TABLE I<br>Optical AND/NAND Logic Gate |   |           |              |                 |                           |                    |  |  |  |

|----------------------------------------|---|-----------|--------------|-----------------|---------------------------|--------------------|--|--|--|

| Х                                      | Y | $	heta_1$ | $\theta_2$   | $\Delta \theta$ | $\mathbf{P}_{\mathrm{I}}$ | $P_{J}$            |  |  |  |

| 0                                      | 0 | 0         | 0            | 0               | 0                         | 1                  |  |  |  |

| 0                                      | 1 | 0         | $60^{\circ}$ | -60°            | $0.25 P_A$                | 0,75P <sub>A</sub> |  |  |  |

| 1                                      | 0 | 300°      | 0            | 300°            | $0.25 P_A$                | $0.75 P_A$         |  |  |  |

| 1                                      | 1 | 300°      | 60°          | 240°            | 0.75P <sub>A</sub>        | 0.25PA             |  |  |  |

TABLE II 16-Boolean Optical Gates using a Single MZI Output Port Output power when input  $\theta_2$ -Logic Gate  $\theta_1$ signal X:Y 0:0 0:1 1:1 1:0 XY(AND)60° 300° 0.25 0.25 0.75 Port I  $\theta$  $\overline{X} + \overline{Y}(NAND)$ 300° 60° 0.25 1 0.75 0.75 Port J 0.25 0.75 0.25  $X\overline{Y}$ 120° 60° Port I  $\theta$ 120° 0.25  $\overline{X}+Y$  $60^{\circ}$ Port J 1 0.75 0.75 $60^{\circ}$ 120° Port I 0 0.75 0.25 0.25  $\overline{X}Y$  $60^{\circ}$  $120^{\circ}$ Port J1 0.25 0.75 0.75  $X + \overline{Y}$  $X \oplus Y(XOR)$ 180° 180° Port I 0 1 1 0  $\overline{X \oplus Y}(XNOR)$ 180° 0 180° 0 1 Port J 1 0(False) $60^{\circ}$  $60^{\circ}$  $\theta$ 0.25 0.25  $\theta$ Port I l(True)  $60^{\circ}$  $60^{\circ}$ Port J 1 0.75 0.75 1 60°  $240^{o}$ 0.25 0.75 Port I  $\theta$ Х 1  $\overline{X}$ 240°  $60^{\circ}$ Port J 1 0.75 0.25 0  $60^{\circ}$ Y  $240^{o}$ Port I  $\theta$ 0.750.25 1  $\overline{Y}$ 60° 0.25 0  $240^{\circ}$ Port J 1 0.75 X + Y(OR) $240^{\circ}$  $120^{\circ}$  $\theta$ 0.750.75 0.75 Port I  $\overline{X}\overline{Y}(NOR)$  $240^{o}$ 120° Port J 1 0.25 0.25 0.25

| EXTINCTION RAT                                      | TIO BEFORE A       | ND AFTER TH | E THRESHOLD       | DER CIRCUIT |  |

|-----------------------------------------------------|--------------------|-------------|-------------------|-------------|--|

| Logic                                               | Before Thersholder |             | After Thresholder |             |  |

| functions (I/J)                                     | Ι                  | J           | Ι                 | J           |  |

| $\frac{XY(AND)}{\overline{X} + \overline{Y}(NAND)}$ | 4.23 dB            | 4.68 dB     | 12.34 dB          | 12.92 dB    |  |

| $X\overline{Y} / \overline{X} + Y$                  | 3.75 dB            | 4.24 dB     | 11.85 dB          | 12.36 dB    |  |

| $\overline{X}Y / X + \overline{Y}$                  | 4.03 dB            | 3.98 dB     | 12.1 dB           | 11.93 dB    |  |

| $\frac{X \oplus Y(XOR)}{X \oplus Y(XNOR)}$          | 16.99 dB           | 16.99 dB    | 11.5 dB           | 11.5 dB     |  |

| 0(False) /<br>1(True)                               | 11.3 dB            | 13.85 dB    | 7.67 dB           | 12.30 dB    |  |

| $X / \overline{X}$                                  | 4.24 dB            | 4.36 dB     | 12.30 dB          | 12.30 dB    |  |

| $Y/\overline{Y}$                                    | 4.29 dB            | 4.27 dB     | 12.37 dB          | 12.37 dB    |  |

| $\frac{\overline{XY}(NOR)}{X+Y(OR)}$                | 13.22 dB           | 7.12 dB     | 12.36 dB          | 11.91 dB    |  |

TABLE III Extinction Ratio Before and After The Thresholder Circuit