André da Silva Pinho rtfss: A Hardware Description Language for Digital Audio Processing

rtfss: Uma Linguagem de Descrição de Hardware para Processamento Digital de Áudio

#### André da Silva Pinho

# rtfss: A Hardware Description Language for Digital Audio Processing

# rtfss: Uma Linguagem de Descrição de Hardware para Processamento Digital de Áudio

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia de Computadores e Telemática, realizada sob a orientação científica do Doutor Tomás António Mendes Oliveira e Silva, Professor do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro

Dedico este trabalho aos meus pais, Armando e Alice.

#### o júri / the jury

| presidente / president       | <b>Professor Doutor Arnaldo Silva Rodrigues de Oliveira</b><br>Professor Auxiliar da Universidade de Aveiro                    |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| vogais / examiners committee | <b>Professor Doutor João Manuel Paiva Cardoso</b><br>Professor Catedrático da Faculdade de Engenharia da Universidade do Porto |  |  |

|                              | Professor Doutor Tomás António Mendes Oliveira e Silva<br>Professor Associado da Universidade de Aveiro (orientador)           |  |  |

## agradecimentos / acknowledgements

Esta tese não é apenas produto do meu esforço, mas também de todas as pessoas que me influenciaram de forma marcante ao longo da minha vida. Em primeiro lugar, quero agradecer profundamente aos meus pais, Armando Pinho e Alice Pinho, por todo o apoio que me deram durante o meu percurso académico. As condições por eles proporcionadas foram o fundamento do meu sucesso nos últimos cinco anos.

Quero agradecer ao Professor Tomás Oliveira e Silva, que aceitou ajudar-me a encontrar tópico e orientar esta tese. As suas ideias e sugestões foram bastante valiosas e desafiaram-me a elevar o trabalho ao nível que se apresenta agora. Tê-lo como orientador fez com que fosse o meu primeiro e último Professor do DETI neste curso. Gostava também de estender este agradecimento a todos os outros Professores da Universidade que contribuíram para a minha formação, e aos restantes membros do DETI.

Quero agradecer à Margarida, que foi uma das primeiras pessoas deste curso que se tornou minha amiga, e que me acabou por aturar na maior parte dos trabalhos das cadeiras. Devo a ela, entre outras coisas, a minha introdução à vida académica. Posteriormente, o Diego juntou-se a nós e a Dream Team foi formada. É de notar que foi por influência musical do Diego que acabei por ter a ideia do tema desta tese. Estimo todos os momentos que passámos juntos e espero que, no futuro, possamos voltar a juntar-nos para despejar WD-40 e fita-cola numa *hackathon* qualquer.

A estes dois amigos, junto o restante grupo de amigos que fiz ao longo de ECT, com quem me diverti imenso e partilhei inúmeras, longas, e por vezes desesperadas noites no DETI a fazer trabalhos. Ao Rodrigo, Dinis, Miguel, Francisco, Fred, Guilherme e demais, reservo um grande obrigado. Vimos o nosso último ano do curso ser parado subitamente graças a um vírus, mas fica o desejo de compensar quando houver hipótese.

Quero agradecer também ao André e ao Neves, dois amigos de longo termo, que, por muito que não tenhamos tido hipótese de fazer muita coisa nos últimos tempos, valorizo a nossa amizade e o apoio que recebo de ambos. Gostava também de agradecer aos meus Professores da Escola Mário Sacramento, especialmente à Professora Isabel Órfão, que durante o Ensino Se-

cundário me consolidou o conhecimento e o interesse em Matemática. Por fim, devo um agradecimento aos meus Professores do Conservatório de Música de Aveiro, com destaque ao Professor Nuno Caçote e à Professora Teresa Macedo. Estes, ajudaram-me a desenvolver a minha vertente artística e acabaram por, indiretamente, influenciar a minha escolha do tema de bastantes projetos desenvolvidos neste curso, incluindo, inevitavelmente, esta tese.

#### Resumo

O interesse em sintetização de áudio em circuitos digitais e sistemas computacionais remonta à época em que as linguagens de programação Lisp, COBOL e Fortran ainda estavam a ser conceptualizadas. Esta era (por volta de 1950) marca o surgimento da linguagem de programação MUSIC I. Desde então, dado o aumento do poder de computação, houve um influxo de novas linguagens capazes de sintetizar áudio. Atualmente, linguagens como SuperCollider, Pd (pure data), Max/MSP, ChucK e Faust estão no espetro das mais populares. Estas linguagens, apesar de terem diferentes abordagens e designs, têm um aspeto comum: são todas linguagens de computador. Embora este tipo de solução conceda bastante flexibilidade, ela apresenta um problema: restrições temporais, particularmente latência de áudio.

Neste documento, uma nova Linguagem de Processamento de Áudio, denominada *rtfss*, é introduzida. Esta linguagem foi concebida para ser compilada principalmente para dispositivos de *hardware*, de forma a tirar partido das suas capacidades de paralelismo. Para complementar a descrição formal da linguagem, será também apresentado um compilador capaz de lidar com um subconjunto das capacidades da linguagem. Este compilador é apto para analisar uma descrição feita em *rtfss* e de compilar para uma linguagem de nível inferior chamada VHDL. Um dos principais destaques de *rtfss* (e do seu compilador) é que a arquitetura de *hardware* sintetizada é segmentada (*pipelined*). Este formato de arquitetura digital é usado em circuitos lógicos para maximizar a frequência de funcionamento e a eficiência do design.

Ao longo deste documento, a descrição formal da linguagem e a implementação do compilador serão meticulosamente analisados e explicados. Serão também ilustrados alguns exemplos de casos de uso nesta linguagem, acompanhados pelo seu processo de compilação.

Neste documento é também descrita uma arquitetura mais simples de outra linguagem de processamento de áudio para *hardware*. Esta linguagem serviu como fundação ao desenvolvimento de *rtfss*. Do desenvolvimento desta arquitetura derivou uma coletânea de blocos de *hardware* em VHDL para tratamento de áudio e de MIDI.

#### Abstract

The pursuit of audio synthesis in digital circuitry and computing systems dates back to the time where programming languages such as Lisp, COBOL and Fortran were still being conceptualized. This era (the 1950s) marks the appearance of the MUSIC I programming language. Since then, and as the processing capabilities of computers kept rising, there was an influx of new languages capable of synthesizing audio. Languages such as SuperCollider, Pd (pure data), Max/MSP, ChucK and Faust are among the most popular ones, nowadays. These languages, although having different approaches and designs, have one aspect in common: they are all computer languages. Albeit these solutions grant great flexibility, they present an issue: timing constraints, particularly audio latency.

In this document, a new Audio Processing Language, called *rtfss*, is introduced. This language was designed to be compiled mainly to hardware targets, exploiting their inherent parallelism. To complement the formal description of the language, a compiler that implements a subset of the language's capabilities will also be presented. This compiler is capable of analysing a design description written in *rtfss* and compile it to the lower level hardware description language VHDL. One of the main highlights of *rtfss* (and its compiler) is that the hardware architecture it synthesizes is pipelined. This type of digital architecture is used in logic designs to maximize the working frequency and the efficiency of the design.

Throughout this document, both the language's formal specification and the compiler's implementation will be thoroughly analysed and explained. Some use-case examples of this language, accompanied by their compilation procedure, will also be illustrated and examined.

In this document, it is also described a simpler architecture of another Hardware Audio Processing Language, which served as a stepping stone towards the development of *rtfss*. As a product of its development, some useful VHDL Audio (and MIDI 1.0) related hardware blocks were implemented.

## Contents

| C             | onter | $\mathbf{nts}$ |                                | i            |

|---------------|-------|----------------|--------------------------------|--------------|

| $\mathbf{Li}$ | st of | Figur          | *es                            | $\mathbf{v}$ |

| $\mathbf{Li}$ | st of | Table          | es                             | vii          |

| 1             | Intr  | oduct          | cion                           | 1            |

|               | 1.1   | Motiv          | vation                         | <br>2        |

|               | 1.2   | Projec         | ct Evolution                   | <br>3        |

|               | 1.3   | Contr          | ributions                      | <br>4        |

|               | 1.4   | Docur          | ment Outline                   | <br>4        |

| <b>2</b>      | Bac   | kgrou          | and and Related Work           | 5            |

|               | 2.1   | FPGA           | A Device                       | <br>5        |

|               | 2.2   | VHDI           | L Language                     | <br>6        |

|               | 2.3   | ANTI           | LR Parser Generator            | <br>7        |

|               | 2.4   | MIDI           | Protocol                       | <br>7        |

|               | 2.5   | Comp           | outer Music Languages          | <br>10       |

|               |       | 2.5.1          | SuperCollider                  | <br>10       |

|               |       | 2.5.2          | Pd and Max/MSP                 | <br>11       |

|               |       | 2.5.3          | ChucK                          | <br>13       |

|               |       | 2.5.4          | Faust                          | <br>14       |

|               | 2.6   | Summ           | nary                           | <br>17       |

| 3             | The   | $e \ rtfss$    | Language                       | 19           |

|               | 3.0   | •              | al Specification               | <br>19       |

|               | 3.1   |                | ments Syntax                   | 20           |

|               | 3.2   | Pulse          | Statement                      | <br>20       |

|               | 3.3   | Stream         | m Statement                    | <br>21       |

|               |       | 3.3.1          | Numeric Literal Representation | <br>23       |

|               |       | 3.3.2          | Previous Stream Values         | <br>24       |

|               |       | 3.3.3          | Stream Synchronization         | <br>25       |

|               |       | 3.3.4          | Stream Buses                   | 26           |

|               |       | 3.3.5          | Cyclic Dependencies            | <br>27       |

|               |       | 3.3.6          | Numeric Stream Arithmetic      | <br>27       |

|               |       |                | + (Sum)                        | <br>28       |

|               |       |                | - (Subtraction)                | <br>28       |

|   |              |                    | - (Symmetric)                                                                                                                             | 8 |

|---|--------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|

|   |              |                    | * (Multiplication)                                                                                                                        | 9 |

|   |              |                    | / (Division)                                                                                                                              | 9 |

|   |              |                    | % (Modulus)                                                                                                                               | 9 |

|   |              |                    | <(Shift Left)                                                                                                                             |   |

|   |              |                    | >> (Shift Right)                                                                                                                          |   |

|   |              |                    | <pre>&lt;&lt; (Rotate Left)</pre>                                                                                                         |   |

|   |              |                    | >>> (Rotate Right)                                                                                                                        |   |

|   |              |                    | == != < > <= >= (Logic Comparisons)                                                                                                       |   |

|   |              |                    |                                                                                                                                           |   |

|   |              |                    |                                                                                                                                           |   |

|   |              |                    | $\& (Property Of) \qquad 33$                                                                                                              |   |

|   |              |                    | ' (Value At Instance) $\dots \dots \dots$ |   |

|   |              |                    | gap (Relative Stream Delay) 33                                                                                                            |   |

|   |              |                    | $(Casting)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              |   |

|   |              | 3.3.7              | midi Stream Arithmetic 32                                                                                                                 |   |

|   |              |                    | noteof (Note Number of Channel) 33                                                                                                        |   |

|   |              |                    | freqof (Frequency of Channel)                                                                                                             | 3 |

|   |              |                    | velof (Velocity of Channel) 33                                                                                                            | 3 |

|   |              |                    | patof (Polyphonic Aftertouch of Channel)                                                                                                  | 4 |

|   |              |                    | nntof (New Note trigger of Channel)                                                                                                       | 4 |

|   |              |                    | ccof (Controller of Channel)                                                                                                              | 4 |

|   |              |                    | pof (Program of Channel)                                                                                                                  | 4 |

|   |              |                    | cpof (Channel Pressure of Channel) 33                                                                                                     | 5 |

|   |              |                    | pbend (Pitch Bend of Channel)                                                                                                             |   |

|   |              | 3.3.8              | Stream Sizing on Contracted Operators                                                                                                     |   |

|   | 3.4          |                    | k                                                                                                                                         |   |

|   | 3.5          |                    | $tement \dots \dots$                |   |

|   | 3.6          |                    | atement                                                                                                                                   |   |

|   | $3.0 \\ 3.7$ |                    | t Syntax                                                                                                                                  |   |

|   |              | -                  |                                                                                                                                           |   |

|   | 3.8          | -                  |                                                                                                                                           |   |

|   | 3.9          | -                  | ble Designs in $rtfss$                                                                                                                    |   |

|   |              | 3.9.1              | IIR Filter Design Revisited    44                                                                                                         |   |

|   |              | 3.9.2              | Filtered Square Wave Design    44                                                                                                         |   |

|   | 3.10         | Summ               | ary                                                                                                                                       | 2 |

| 4 | The          | ntfaa              | Compiler 4:                                                                                                                               | 2 |

| 4 | 4.1          | Pream              | •                                                                                                                                         |   |

|   | 4.1          |                    |                                                                                                                                           |   |

|   |              | 4.1.1              | rtfss's Compiler Limitations                                                                                                              |   |

|   | 4.0          | 4.1.2              | Support Example                                                                                                                           |   |

|   | 4.2          | -                  | Tokenization and Syntactic Analysis    4'                                                                                                 |   |

|   |              | 4.2.1              | Lexical Analysis                                                                                                                          |   |

|   |              |                    | Support Example Analysis 50                                                                                                               |   |

|   |              | 4.2.2              | Syntactic Analysis                                                                                                                        |   |

|   |              |                    | Support Example Analysis                                                                                                                  | 4 |

|   | 4.3          | $\mathit{rtfss's}$ | Abstract Syntax Tree                                                                                                                      | 4 |

|   |              | 4.3.1              | Support Example Analysis                                                                                                                  | 0 |

|   | 4.4          | Consta             | ant Stream Solver                                                                                                                         | 0 |

|   |            | 4.4.1          | Support Example Analysis                                                                                                       |

|---|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

|   | 4.5        | Stream         | and Pulse Solver                                                                                                               |

|   |            | 4.5.1          | Support Example Analysis                                                                                                       |

|   | 4.6        | Assign         | ment Dependency Checker and Trimmer                                                                                            |

|   |            | 4.6.1          | Support Example Analysis                                                                                                       |

|   | 4.7        | Assign         | $ment Mover \dots \dots$ |

|   |            | 4.7.1          | Support Example Analysis                                                                                                       |

|   | 4.8        | rtfss's        | Architecture Graph                                                                                                             |

|   |            | 4.8.1          | rtfss's Architecture Graph Generator                                                                                           |

|   |            | 4.8.2          | Support Example Analysis                                                                                                       |

|   | 4.9        | rtfss's        | Final Representation Graph7878                                                                                                 |

|   |            | 4.9.1          | rtfss's Final Representation Graph Generator                                                                                   |

|   |            | 4.9.2          | Support Example Analysis                                                                                                       |

|   | 4.10       | Outpu          | t Language Generator                                                                                                           |

|   |            | 4.10.1         | Support Example Analysis                                                                                                       |

|   | 4.11       | Projec         | t Code Metrics $\ldots \ldots $     |

|   | 4.12       | Summ           | ary                                                                                                                            |

| - | C          | 1              |                                                                                                                                |

| 5 | <b>501</b> |                | io-Oriented Hardware Blocks97Audio Oscillator97                                                                                |

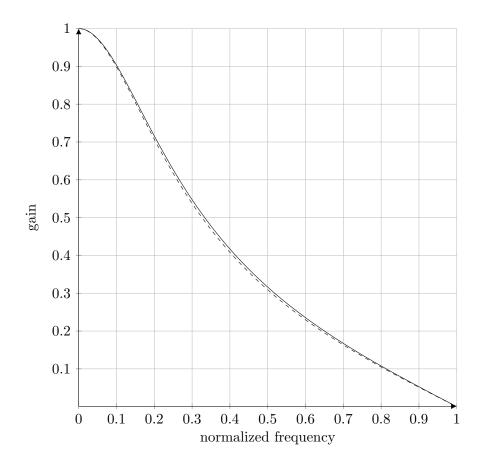

|   | 0.1        | 5.1.1          | Sine Module (sine)         97                                                                                                  |

|   |            | 5.1.1<br>5.1.2 | Generic Oscillator Module (generic_osc)                                                                                        |

|   |            | 5.1.2<br>5.1.3 | Sine Oscillator (sine_osc)                                                                                                     |

|   |            | 5.1.3<br>5.1.4 | Parameterizable Oscillator (param_osc)                                                                                         |

|   | 5.2        |                | Audio Filter         105                                                                                                       |

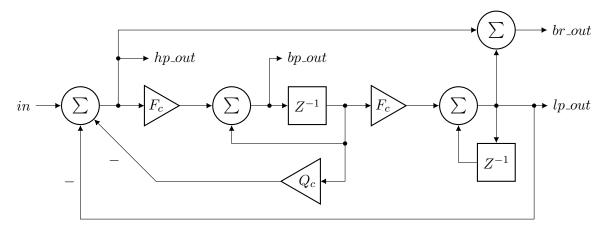

|   | 0.2        | 5.2.1          | State Variable Filter (state_var_filter)       105                                                                             |

|   | 5.3        |                | Audio Delay Line                                                                                                               |

|   | 0.0        | 5.3.1          | Basic Variable Delay Line (delay0)                                                                                             |

|   |            | 5.3.1<br>5.3.2 | Intermediate Variable Delay Line (delay0) 100                                                                                  |

|   |            | 5.3.2          | Complex Variable Delay Line (delay2)                                                                                           |

|   | 5.4        |                | Audio Utility                                                                                                                  |

|   | 0.4        | 5.4.1          |                                                                                                                                |

|   |            | 0.4.1          | Audio Amplifier (amp)       107         Saturation on the Unsigned Architecture       107                                      |

|   |            |                | Saturation on the Signed Architecture                                                                                          |

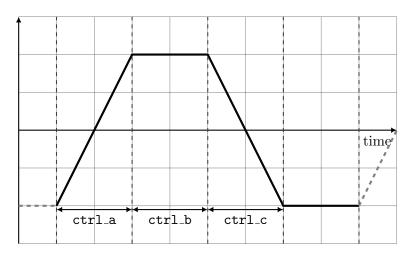

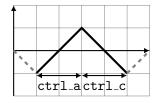

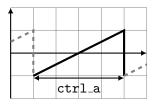

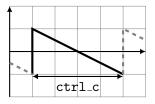

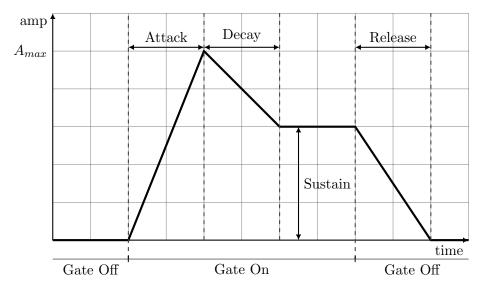

|   |            | 5.4.2          | Envelope Generator (env_gen)                                                                                                   |

|   |            | 5.4.2<br>5.4.3 | Tick / Pulse Generator (tick_creator)                                                                                          |

|   | 5.5        |                | MIDI Toolbox                                                                                                                   |

|   | 0.0        | 5.5.1          | MIDI Interpreter (midi_interpreter)                                                                                            |

|   |            | 5.5.1<br>5.5.2 | MIDI Voice Handler (midi_note)                                                                                                 |

|   |            | 5.5.2<br>5.5.3 | MIDI Note Frequency (midi_freq)                                                                                                |

|   |            | 5.5.3<br>5.5.4 | MIDI Note Frequency (midi_freq)                                                                                                |

|   |            | 5.5.4 $5.5.5$  | MIDI Control Handler (midi_control)                                                                                            |

|   |            | 5.5.6          | MIDI Pitch Bend Handler (midi_pitch)                                                                                           |

|   |            | 5.5.0<br>5.5.7 | MIDI Channel Pressure Handler (midi_pressure)                                                                                  |

|   | 5.6        |                | ary $\dots \dots \dots$        |

|   | 0.0        | Summ           | $a_1y$                                                                                                                         |

| 6            | Discussion and Future Work                                   | 115 |

|--------------|--------------------------------------------------------------|-----|

|              | 6.1 Final Remarks                                            | 115 |

|              | 6.2 Future Work                                              | 116 |

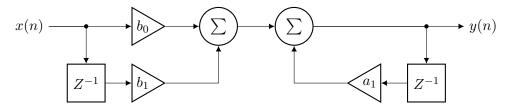

| $\mathbf{A}$ | Simple First-Order IIR Filter Example                        | 119 |

| в            | VHDL Code Generated for the Support Example of Section 4.1.2 | 121 |

| С            | Another Example in <i>rtfss</i>                              | 127 |

| D            | The <i>rtfss</i> ANTLR4 Grammar                              | 137 |

| Bi           | bliography                                                   | 143 |

## List of Figures

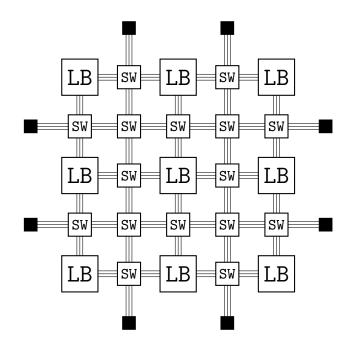

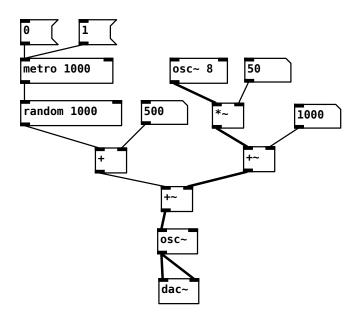

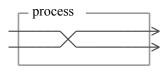

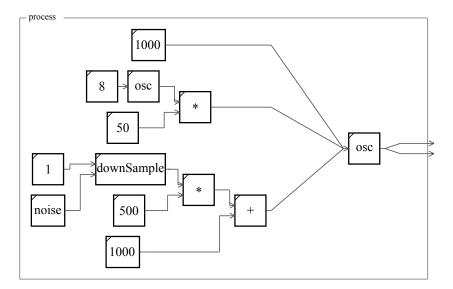

| <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ol> | Simplified diagram of the architecture of a FPGA [1] Example of an Audio Signal Patch in Pd for a frequency modulated sine wave.<br>Faust Channel Swapper Program Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6<br>12<br>17<br>17 |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

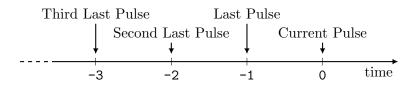

| 3.1                                                            | Stream Previous Instants timeline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                  |

| 3.2                                                            | Example diagram of <i>rtfss</i> Stream Arithmetics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                  |

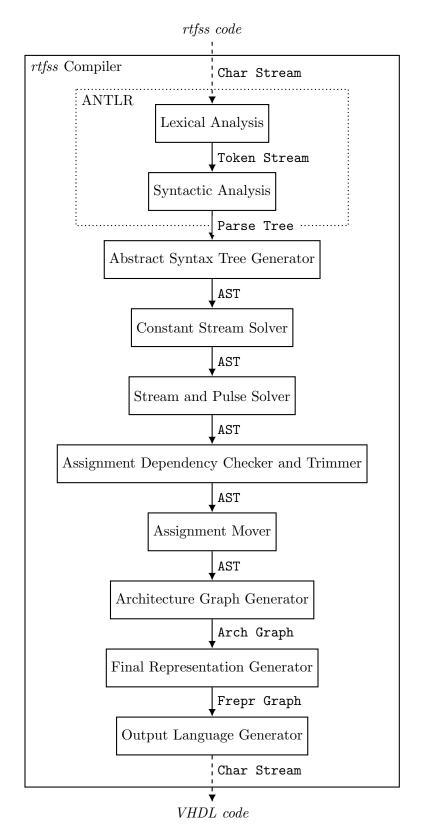

| $4.1 \\ 4.2$                                                   | Simplified diagram of <i>rtfss</i> compiler processing stages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                  |

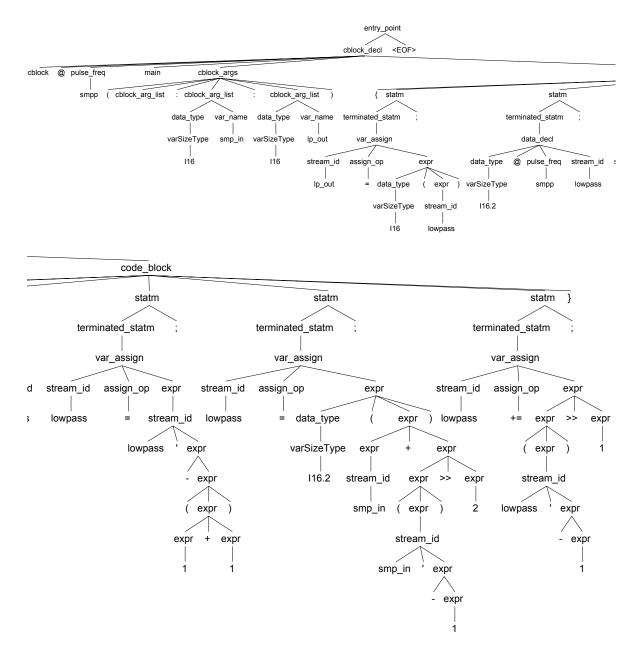

|                                                                | the <i>rtfss</i> grammar) of the example of Section 4.1.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55                  |

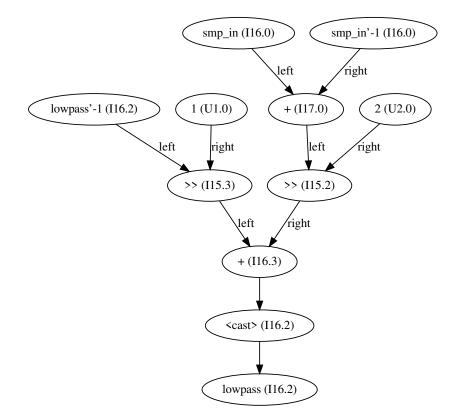

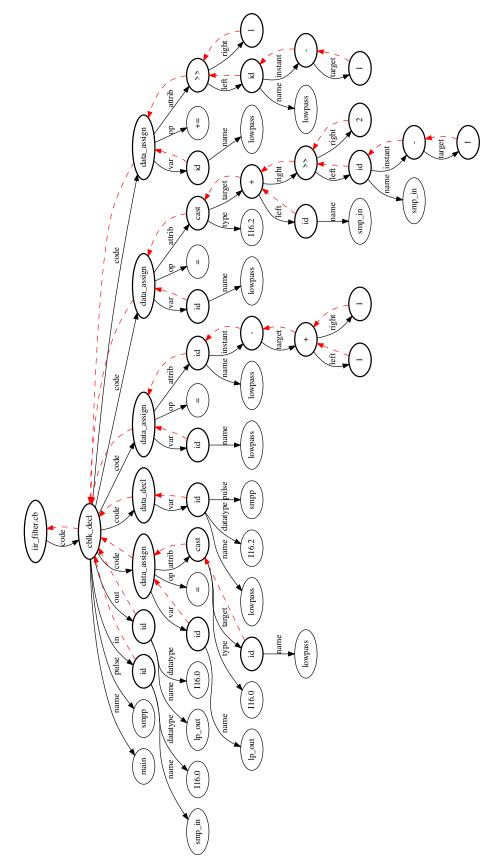

| 4.3                                                            | Full initial Abstract Syntax Tree of the example of Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61                  |

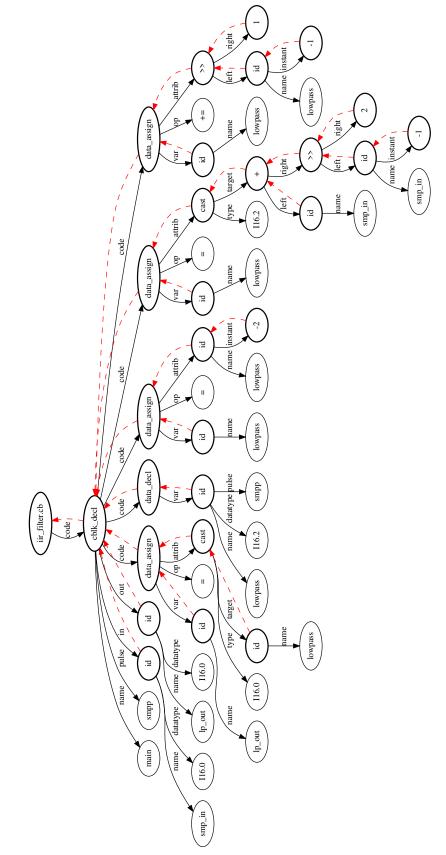

| 4.4                                                            | Full Abstract Syntax Tree after Constant Stream Solver of the example of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |

|                                                                | Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63                  |

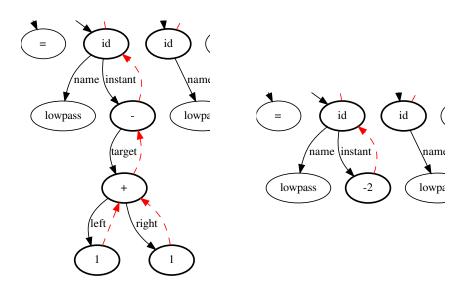

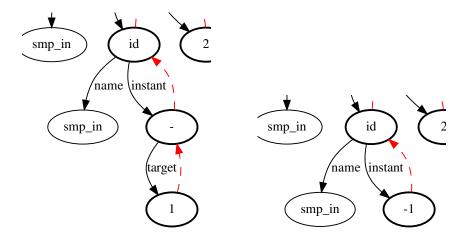

| 4.5                                                            | Detail 1 on the before and after modifications done on the Abstract Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

|                                                                | Tree by the Constant Stream Solver on the example of Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                  |

| 4.6                                                            | Detail 2 on the before and after modifications done on the Abstract Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64                  |

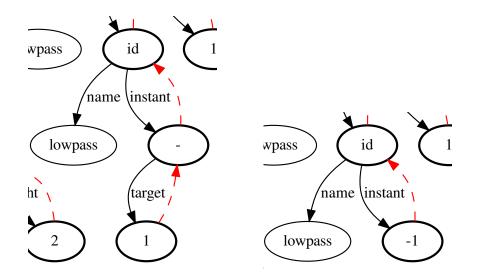

| 4.7                                                            | Detail 3 on the before and after modifications done on the Abstract Syntax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

| 4.0                                                            | Tree by the Constant Stream Solver on the example of Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                  |

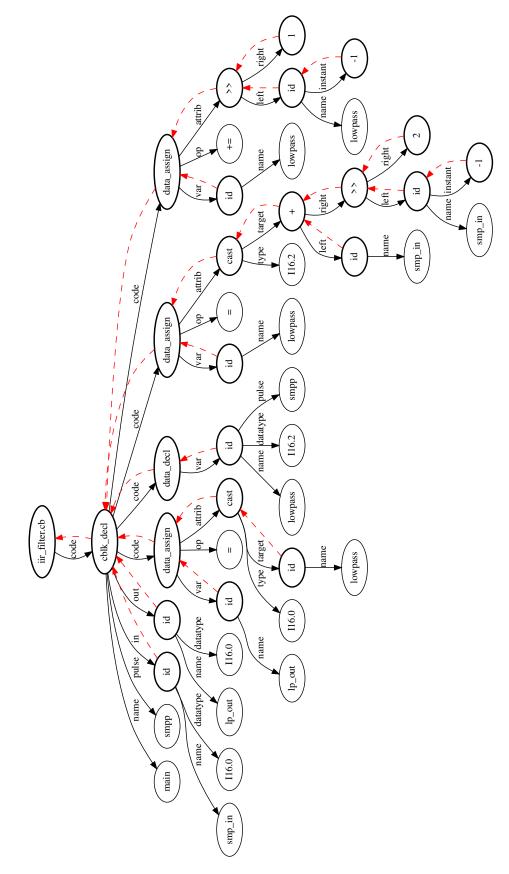

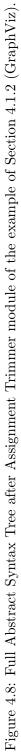

| 4.8                                                            | Full Abstract Syntax Tree after Assignment Trimmer module of the example $\int G_{ij} dx_{ij} dx$ | <u>co</u>           |

| 4.0                                                            | of Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69                  |

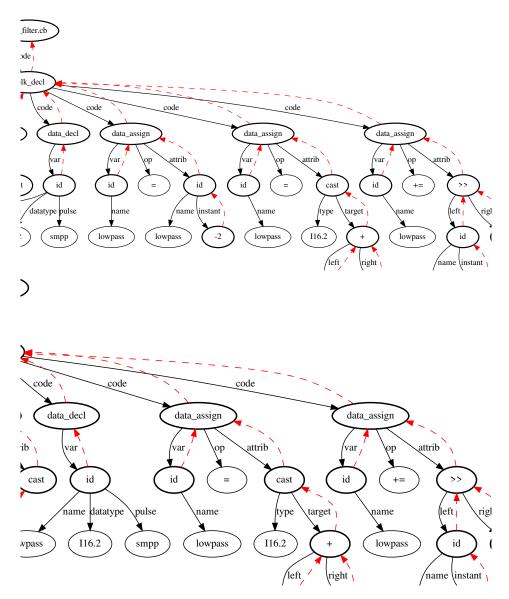

| 4.9                                                            | Detail 1 on the before and after modifications done on the Abstract Syntax Tree<br>by the Assignment Trimmer module on the grample of Section 4.1.2 (CraphVig)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                  |

| 4 10                                                           | by the Assignment Trimmer module on the example of Section 4.1.2 (GraphViz).<br>Full Abstract Syntax Tree after Assignment Mover module of the example of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70                  |

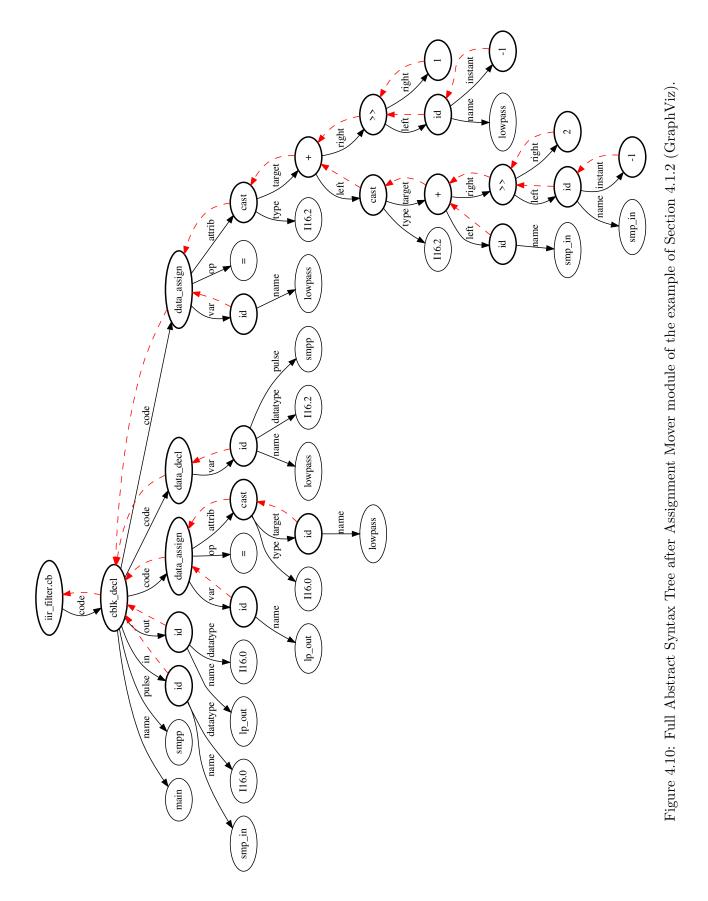

| 4.10                                                           | Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                  |

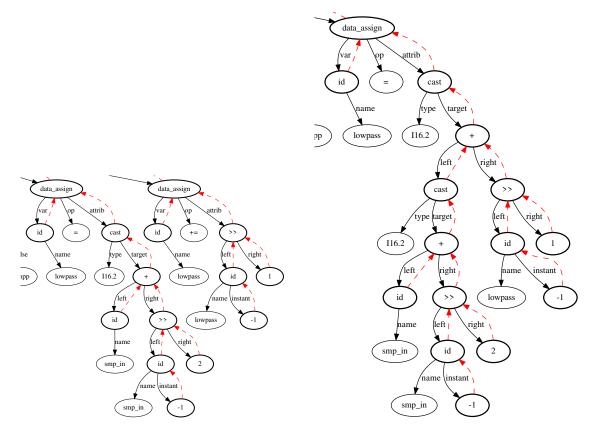

| 4 11                                                           | Detail 1 on the before and after modifications done on the Abstract Syntax Tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10                  |

| 1.11                                                           | by the Assignment Mover module on the example of Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 74                  |

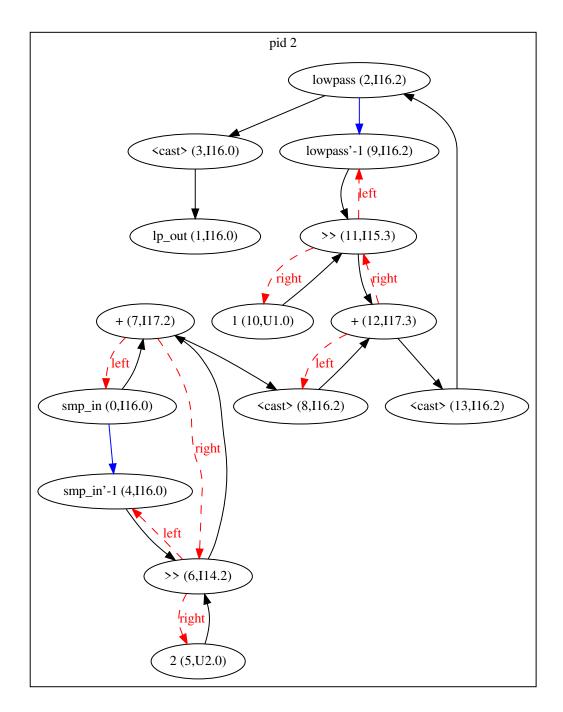

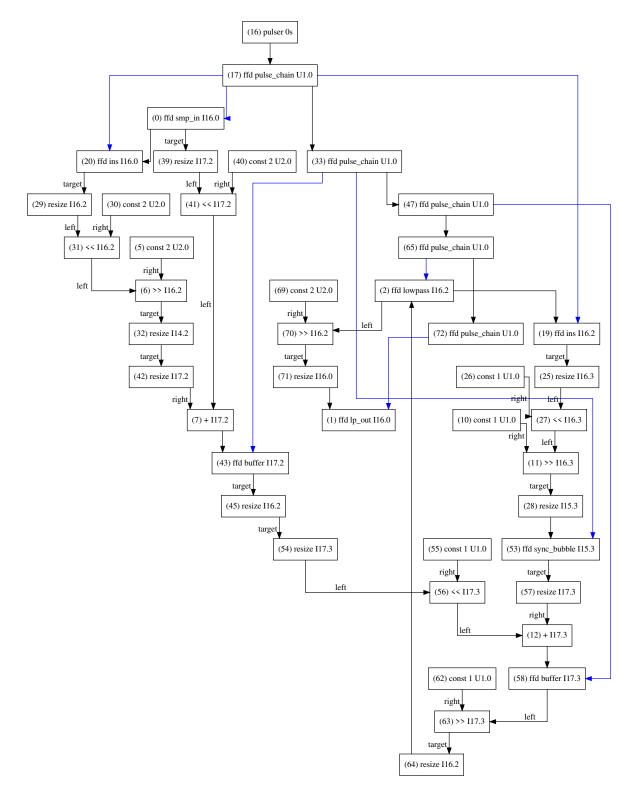

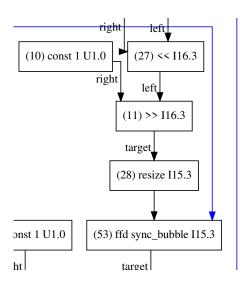

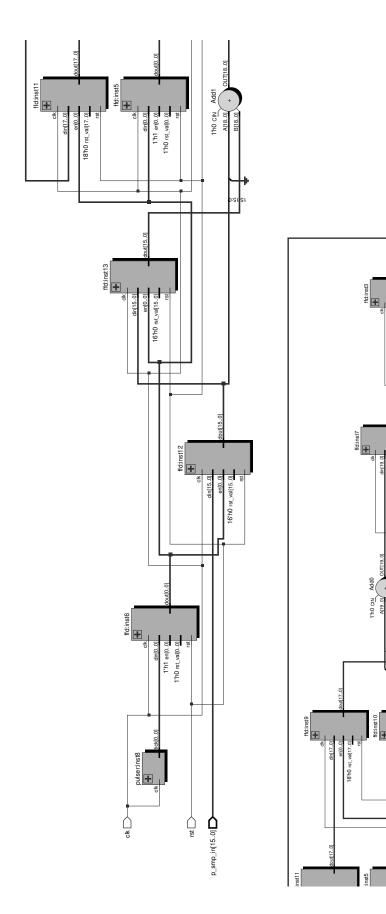

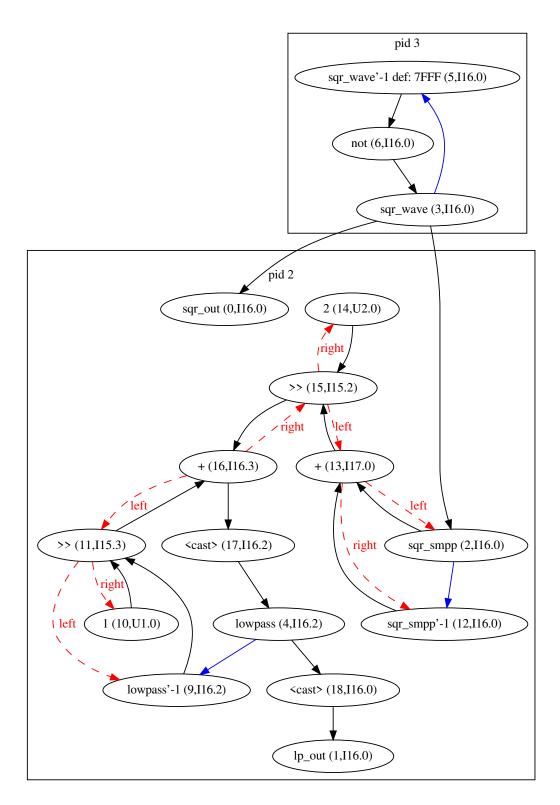

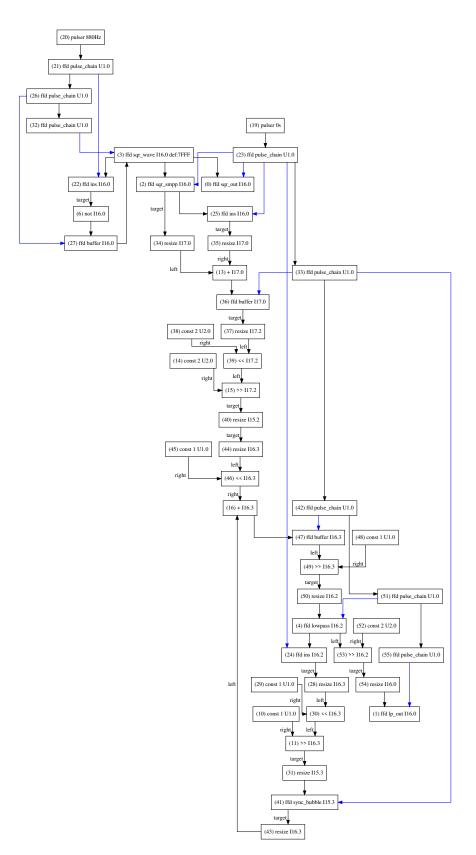

| 4.12                                                           | Full Architecture Graph of the example of Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79                  |

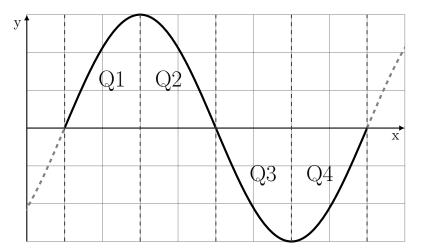

|                                                                | Full Final Representation Graph of the example of Section 4.1.2 (GraphViz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 89                  |