## **Guilherme Moura Reis Correia Gil**

Modelação e simulação de equipamentos de rede para Indústria 4.0

Modelation and simulation of network equipment for Industry 4.0

## **Guilherme Moura Reis Correia Gil**

Modelação e simulação de equipamentos de rede para Indústria 4.0

Modelation and simulation of network equipment for Industry 4.0

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia Eletrónica e Telecomunicações, realizada sob a orientação científica do Doutor Paulo Bacelar Reis Pedreiras, Professor Auxiliar do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro, e do Doutor Luís Emanuel Moutinho da Silva, Professor Adjunto Convidado da Escola Superior de Tecnologia e Gestão de Águeda.

| Dedico esta dissertação apoio que me deram. | à minha família, | namorada e amigos pelo |

|---------------------------------------------|------------------|------------------------|

|                                             |                  |                        |

|                                             |                  |                        |

|                                             |                  |                        |

|                                             |                  |                        |

|                                             |                  |                        |

|                                             |                  |                        |

## o júri / the jury

presidente / president Prof. Doutor Manuel Bernardo Salvador Cunha

Professor Auxiliar, Universidade de Aveiro

vogais / examiners committee Prof. Doutor Luís Miguel Pinho de Almeida

Professor Associado, Faculdade de Engenharia da Universidade do Porto

Prof Doutor Luís Emanuel Moutinho da Silva

Professor Adjunto Convidado, Universidade de Aveiro

# agradecimentos / acknowledgements

Gostaria de agradecer, em primeiro lugar, aos meus orientadores, Professor Doutor Paulo Pedreiras e Professor Doutor Luís Moutinho, pela excelente orientação e dedicação que proporcionaram ao longo deste percurso. Obrigado por estarem disponíveis sempre que precisasse, pela paciência em tolerar os meus erros e pela forma como me trataram. Espero que tenham tido tanto gosto em trabalhar comigo como eu tive com ambos desejando que, num futuro próximo, continuaremos a trabalhar juntos.

obrigado à minha namorada, Andreia Andrade, por ser aquela pessoa que me consegue relaxar até nos momentos mais difíceis. Obrigado por todo o amor que me deste e por todos os momentos que passámos juntos nestes últimos cinco anos. Agora vais ter de ficar comigo para o resto da vida :p.

obrigado aos meus amigos por todo o apoio e ajuda que me deram nestes últimos cinco anos. Em particular gostaria de agradecer ao Ivo Oliveira, Marco Sousa e Miguel Tavares por todos os bons momentos que despendemos a jogar às copas no aquário do DETI enquanto deveria estar a trabalhar na dissertação.

por último, mas não com menor importância, obrigado à minha família por me aturar nestes últimos meses, nos quais estivemos de ficar confinados. Eu sei que às vezes posso ser um bocado chato. Obrigado aos meus pais, Zé Toninho e Geninha, por todo o apoio, carinho e dedicação que me deram ao longo da minha vida e por me fazerem a pessoa que sou hoje, o filho favorito;).

#### **Palavras Chave**

Redes de Comunicação Tempo-Real, Simuladores de Redes, Ethernet Tempo-Real, Indústria 4.0.

#### Resumo

Atualmente o setor industrial tem vindo cada vez mais a optar por tecnologias digitais de forma a automatizar todos os seus processos. Este desenvolvimento surge de noções como Indústria 4.0, que redefine o modo de como estes sistemas são projetados. Estruturalmente, todos os componentes destes sistemas encontram-se conectados numa rede complexa conhecida como Internet Industrial das Coisas. Certos requisitos advêm deste conceito, no que toca às redes de comunicação industriais, entre os quais se destacam a necessidade de garantir comunicações tempo-real bem como suporte a uma gestão dinâmica dos recursos, os quais são de extrema importância. Várias linhas de investigação procuraram desenvolver tecnologias de rede capazes de satisfazer tais exigências. Uma destas soluções é o "Hard Real-Time Ethernet Switch" (HaRTES), um switch Ethernet com suporte a comunicações de tempo-real e gestão dinâmica de Qualidade-de-Serviço (QoS), requisitos impostos pela Indústria 4.0.

O processo de projeto e implementação de redes industriais pode, no entanto, ser bastante moroso e dispendioso. Tais aspetos impõem limitações no teste de redes de largas dimensões, cujo nível de complexidade é mais elevado e requer o uso de mais hardware. Os simuladores de redes permitem atenuar o impacto de tais limitações, disponibilizando ferramentas que facilitam o desenvolvimento de novos protocolos e a avaliação de redes de comunicações.

No âmbito desta dissertação desenvolveu-se um modelo do switch HaRTES no ambiente de simulação OMNeT++. Com um objetivo de demonstrar uma solução que possa ser utilizada em redes de tempo-real industriais, esta dissertação apresenta os aspetos fundamentais do modelo implementado bem como um conjunto de experiências que o comparam com um protótipo laboratorial já existente, no âmbito da sua validação.

#### **Keywords**

Real-Time Communication Networks, Network simulators, Real-Time Ethernet, Industry 4.0.

#### **Abstract**

Currently, the industrial sector has increasingly opted for digital technologies in order to automate all its processes. This development comes from notions like Industry 4.0 that redefines the way these systems are designed. Structurally, all the components of these systems are connected in a complex network known as the Industrial Internet of Things. Certain requirements arise from this concept regarding industrial communication networks. Among them, the need to ensure real-time communications, as well as support for dynamic resource management, are extremely relevant. Several research lines pursued to develop network technologies capable of meeting such requirements. One of these protocols is the Hard Real-Time Ethernet Switch (HaRTES), an Ethernet switch with support for real-time communications and dynamic resource management, requirements imposed by Industry 4.0.

The process of designing and implementing industrial networks can, however, be quite time consuming and costly. These aspects impose limitations on testing large networks, whose level of complexity is higher and requires the usage of more hardware. The utilization of network simulators stems from the necessity to overcome such restrictions and provide tools to facilitate the development of new protocols and evaluation of communications networks.

In the scope of this dissertation a HaRTES switch model was developed in the OMNeT++ simulation environment. In order to demonstrate a solution that can be employed in industrial real-time networks, this dissertation presents the fundamental aspects of the implemented model as well as a set of experiments that compare it with an existing laboratory prototype, with the objective of validating its implementation.

# **Contents**

| Co               | onten  | its                                              | 1            |

|------------------|--------|--------------------------------------------------|--------------|

| Li               | st of  | Figures                                          | iii          |

| Li               | st of  | Tables                                           | $\mathbf{v}$ |

| $\mathbf{G}^{]}$ | lossaı | ry                                               | vii          |

| 1                | Intr   | roduction                                        | 1            |

|                  | 1.1    | Problem Statement                                | 1            |

|                  | 1.2    | Objectives                                       | 2            |

|                  | 1.3    | Document Outline                                 | 2            |

| 2                | The    | eoretical Real-Time and Ethernet concepts        | 5            |

|                  | 2.1    | Real-Time Systems                                |              |

|                  |        | 2.1.1 Classification of real-time systems        | 6            |

|                  |        | 2.1.2 Task Model                                 | 7            |

|                  |        | 2.1.3 Scheduling                                 |              |

|                  |        | 2.1.4 Schedulability Analysis                    | 14           |

|                  |        | 2.1.5 Hierarchical Scheduling                    | 16           |

|                  | 2.2    | Real Time communications                         | 17           |

|                  |        | 2.2.1 Communication paradigms                    | 18           |

|                  | 2.3    | Ethernet                                         | 19           |

|                  |        | 2.3.1 Ethernet Frame                             | 19           |

|                  |        | 2.3.2 Ethernet Switch                            | 20           |

|                  | 2.4    | Real-time protocols over Ethernet                | 23           |

|                  |        | 2.4.1 Real-time protocols on COTS switches       | 23           |

|                  |        | 2.4.2 Real-time protocols on customized hardware | 25           |

| 3                | An     | FTT-Enabled Switch - HaRTES                      | 29           |

|                  | 3.1    | The Flexible Time Triggered paradigm             |              |

|                  |        | 3.1.1 FTT Elementary cycle                       |              |

|                  | 3.2    | Flexible Time Triggered Switch Ethernet          |              |

|                  |        | 3.2.1 FTT-SE master architecture                 |              |

|                  |        | 3.2.2 FTT-SE slave architecture                  |              |

|                  |        | 3.2.3 FTT-SE communication model                 |              |

|                  | 3.3    | Hard Real Time Ethernet Switch                   |              |

|                  |        | 3.3.1 HaRTES internal architecture               |              |

|                  |        | 3.3.2 HaRTES communication description           |              |

|                  |        | 3.3.3 Advances over the HaRTES implementation    | 40           |

| 4                |        | work Simulators                                  | 47           |

|                  | 4.1    | Overview of different network simulators         | 47           |

ii CONTENTS

|   |            | 4.1.1     | ns-3                                                                                    | 49           |

|---|------------|-----------|-----------------------------------------------------------------------------------------|--------------|

|   |            | 4.1.2     | OMNET++                                                                                 | 49           |

|   |            | 4.1.3     | QualNet                                                                                 | 50           |

|   |            | 4.1.4     | NetSim                                                                                  | 51           |

|   |            | 4.1.5     | OPNET                                                                                   | 51           |

|   |            | 4.1.6     | TrueTime                                                                                | 52           |

|   | 4.2        | A comp    | parative analysis of network simulators                                                 | 54           |

|   | 4.3        | The ON    | MNeT++ framework                                                                        | 57           |

|   |            | 4.3.1     | Model Structure                                                                         | 57           |

|   |            | 4.3.2     | NED Language                                                                            | 59           |

|   |            | 4.3.3     | Messages and Packets                                                                    | 60           |

|   |            | 4.3.4     | OMNeT++ Architecture                                                                    | 61           |

|   |            | 4.3.5     | Analysis facilities                                                                     | 64           |

|   |            | 4.3.6     | Third party libraries                                                                   | 65           |

| _ | T          | 1         | II-DTEC!4-l d-l OMN-T                                                                   | P7-1         |

| 5 | 1mp<br>5.1 |           | ng HaRTES switch model on OMNeT++ isolation with IEEE 802.1Q in a Ethernet switch model | <b>71</b> 72 |

|   | 5.2        |           | er-based scheduling framework for Ethernet switches                                     | 75           |

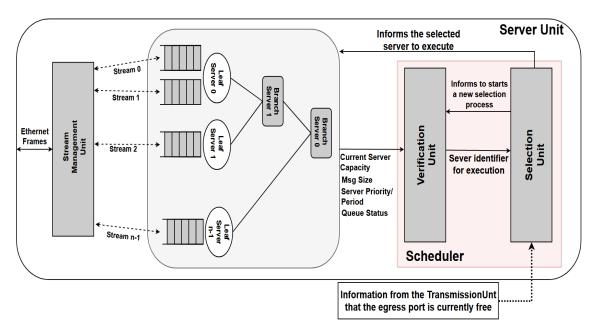

|   | 0.2        | 5.2.1     | Switch Architecture                                                                     |              |

|   |            | 5.2.1     | Implementation of the hierarchical server-based framework                               | 70<br>77     |

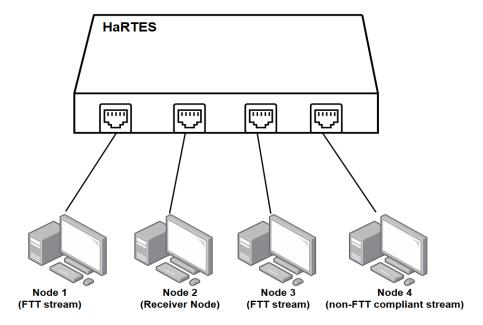

|   | 5.3        |           | S simulation model                                                                      | 88           |

|   | 0.0        | 5.3.1     | HaRTES switch                                                                           |              |

|   |            | 5.3.1     | FTT Compliant nodes                                                                     |              |

|   |            | 0.0.2     | 111 Compilant nodes                                                                     | 51           |

| 6 | Vali       | dation of | of the implemented OMNeT++ simulation models                                            | 97           |

|   | 6.1        | Validat   | ion of the IEEE 802.1Q simulation model                                                 |              |

|   |            | 6.1.1     | Experiment 1 - Homogeneous traffic set                                                  |              |

|   |            | 6.1.2     | Experiment 2 - Heterogeneous message set                                                |              |

|   | 6.2        | Validat   | ion of the server-based scheduling model                                                | 101          |

|   |            | 6.2.1     | Experiment 1 - Assessing the model control capabilities                                 |              |

|   |            | 6.2.2     | Experiment 2 - Realistic network simulation                                             |              |

|   | 6.3        | -         | ring the performance of the frameworks in Ethernet switches                             |              |

|   |            | 6.3.1     | Experiment 1 - Normal operation                                                         |              |

|   |            | 6.3.2     | Experiment 2 - Abnormal node operation                                                  |              |

|   | 6.4        | •         | nental validation of HaRTES simulation model                                            |              |

|   |            | 6.4.1     | Temporal isolation between the traffic classes                                          |              |

|   |            | 6.4.2     | Traffic confinement within the asynchronous subsystem                                   | 117          |

| 7 | Clos       | sure      |                                                                                         | 121          |

|   | 7.1        | Conclus   | sions                                                                                   | 121          |

|   | 7.2        |           | Work                                                                                    |              |

| _ | _          |           |                                                                                         |              |

|   | eferer     | 2000      |                                                                                         | 123          |

# **List of Figures**

| 2.1  | Scheduling algorithms                                                                       | 9  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.2  | Standard Ethernet IEEE 802.3 Data frame                                                     | 19 |

| 2.3  | Internal structure of an Ethernet switch (from R. Marau, L. Almeida and P. Pedreiras        |    |

|      | [13], 2006)                                                                                 | 21 |

| 2.4  | Standard IEEE 802.1Q Ethernet VLAN-tag frame                                                | 21 |

| 2.5  | Typical FTT-SE system architecture                                                          | 24 |

| 2.6  | ETHERNET PowerLink communication cycle (based from [2])                                     | 25 |

| 2.7  | PROFINET-IRT communication cycle (based from [19])                                          | 26 |

| 2.8  | Typical AFDX architecture (based from [2])                                                  | 27 |

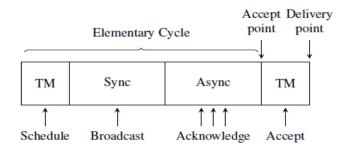

| 3.1  | FTT paradigm Elementary Cycle structure (based from [2])                                    | 30 |

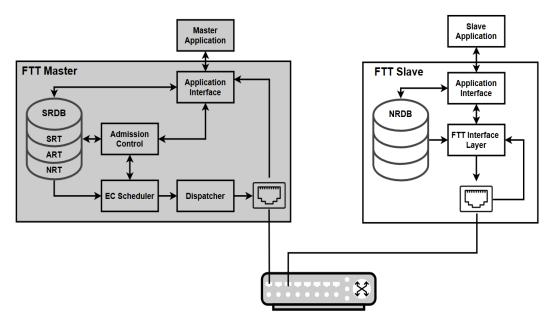

| 3.2  | FTT-SE master/slave architecture (based from [20])                                          | 32 |

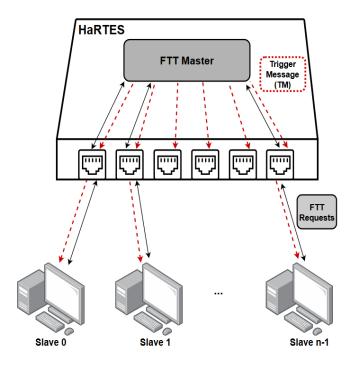

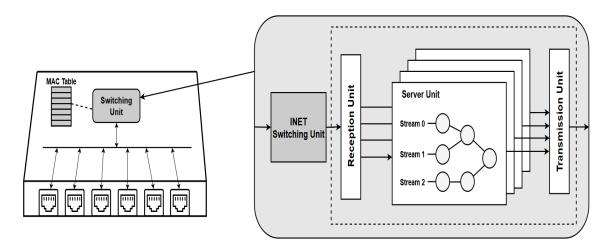

| 3.3  | HaRTES architecture                                                                         | 36 |

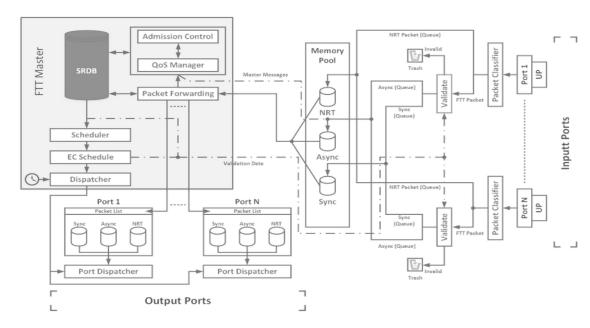

| 3.4  | HaRTES internal architecture (from [22])                                                    | 37 |

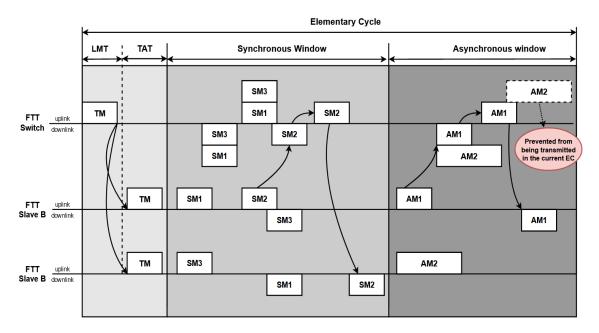

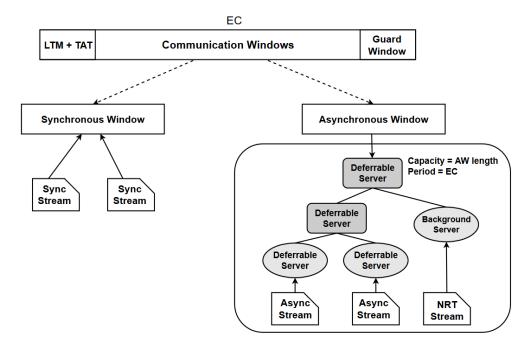

| 3.5  | HaRTES communication model (based from [2])                                                 | 39 |

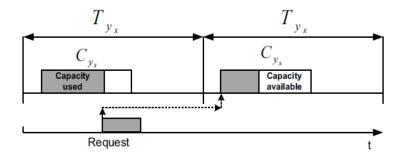

| 3.6  | Distinct four phases of the proposed protocol over the FTT elementary cycle (from Guillermo |    |

|      | Rodriguez-Navas, Julián Proenza [24], 2013)                                                 | 41 |

| 3.7  | Network behavior throughout the different four phases of the protocol (from Guillermo       |    |

|      | Rodriguez-Navas, Julián Proenza [24], 2013)                                                 | 41 |

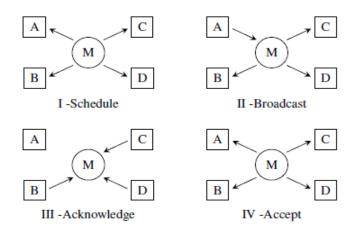

| 3.8  | A general architecture of the proposed server-based hierarchy (from Rui Santos et al [25],  |    |

| 0.0  | 2011)                                                                                       | 43 |

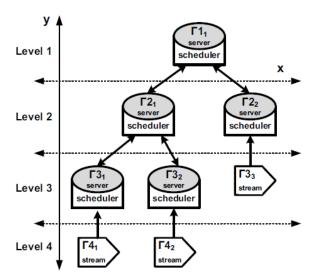

| 3.9  | Example of idle-time insertion (from Rui Santos et al [25], 2011)                           | 44 |

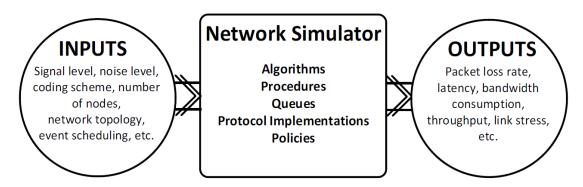

| 4.1  | Abstract structure of network simulators (from J.Suárez et al. [29], 2015)                  | 48 |

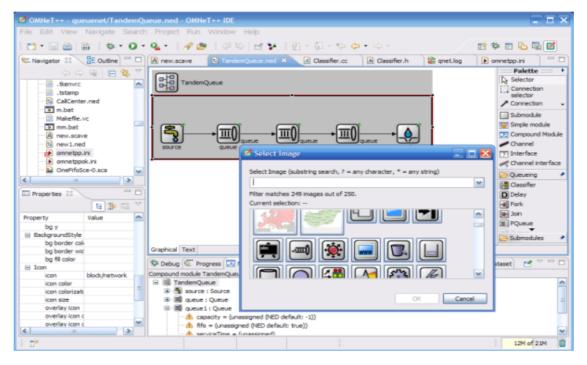

| 4.2  | OMNeT++ IDE (from [35])                                                                     | 50 |

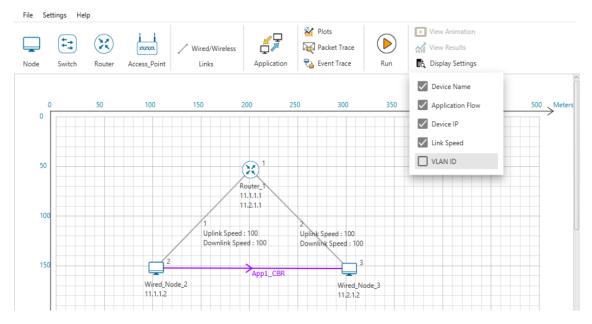

| 4.3  | NetSim GUI ( <i>from</i> [42])                                                              | 51 |

| 4.4  | OPNET architecture (from Saba Siraj et al. [44], 2012)                                      | 52 |

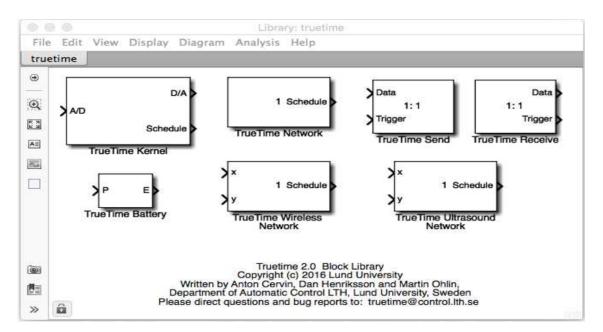

| 4.5  | TrueTime Simulink blocks (from [47])                                                        | 53 |

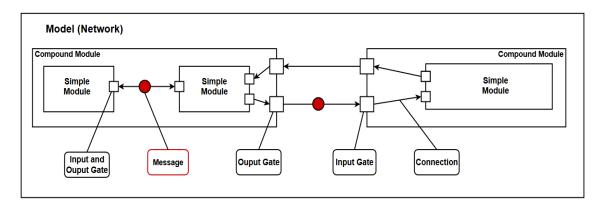

| 4.6  | OMNeT++ module structure                                                                    | 58 |

| 4.7  | OMNeT++ connection types                                                                    | 58 |

| 4.8  | Example of a NED file structure: a) network; b) simple module; c) compound module           | 59 |

| 4.9  | OMNeT++ cMessage and cPacket class properties                                               | 61 |

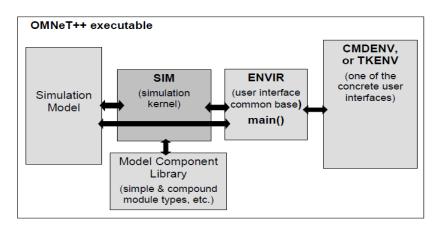

| 4.10 | OMNeT++ architecture (from András Varga and Rudolf Horning [51], 2008)                      | 61 |

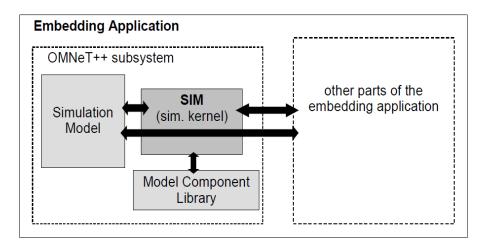

| 4.11 | Embedded OMNeT++ architecture (from András Varga and Rudolf Horning [51], 2008).            | 62 |

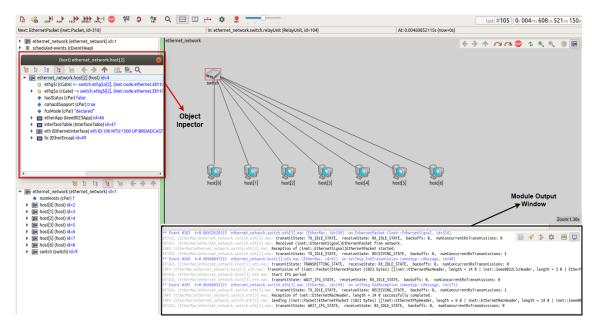

| 4.12 | OMNeT++ Tkenv                                                                               | 63 |

| 4.13 | OMNeT++ main environment                                                                    | 63 |

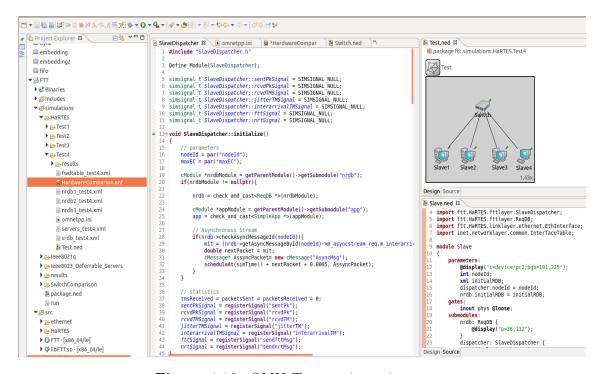

| 4.14 |                                                                                             | 64 |

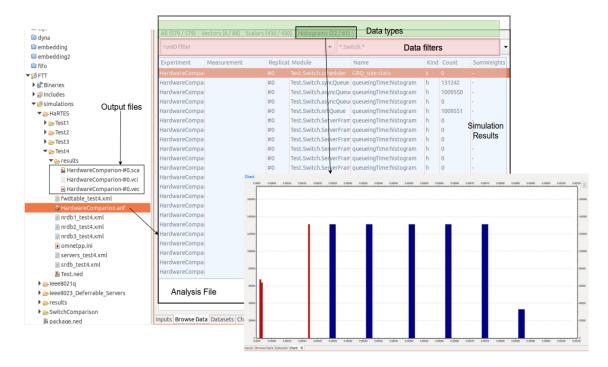

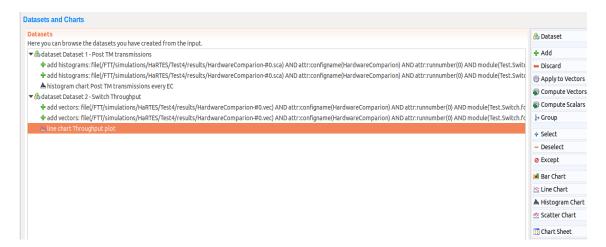

| 4.15 | OMNeT++ dataset example                                                                     | 65 |

| 4.16 | Example of a user-defined chunk for a .msg file (from [36])                                 | 68 |

| 4.17 | Example of chunk manipulation (from [36])                                                   | 68 |

| 4.18 | Example of packet tagging in INET (from [36])                                               | 69 |

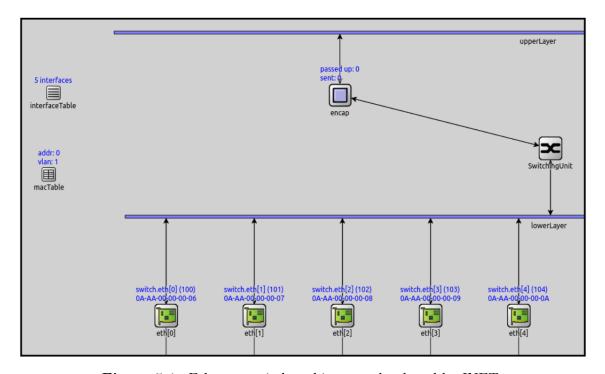

| 5.1  | Ethernet switch architecture developed by INET.                                             | 72 |

iv LIST OF FIGURES

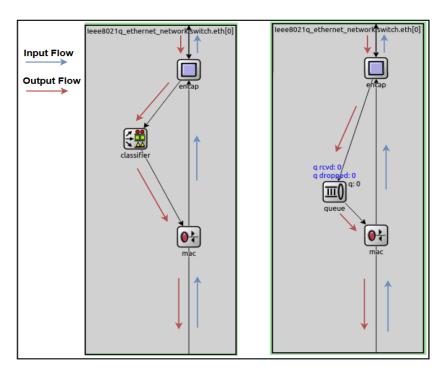

| 5.2  | Ethernet switch ports with the implemented framework in OMNeT++                            | 73  |

|------|--------------------------------------------------------------------------------------------|-----|

| 5.3  | Ethernet switch ports: a) with the implemented framework; b) without the framework in      |     |

|      | OMNeT++                                                                                    | 74  |

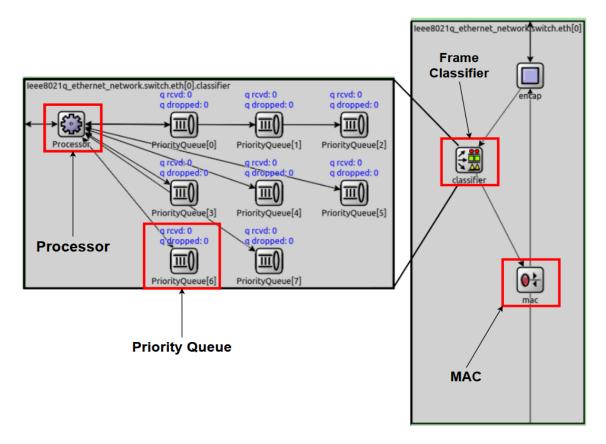

| 5.4  | Processor class implemented in OMNeT++                                                     | 75  |

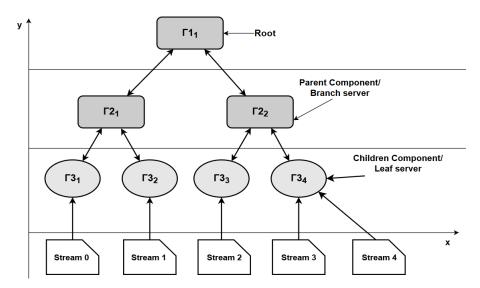

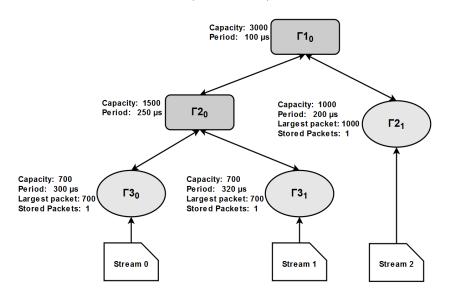

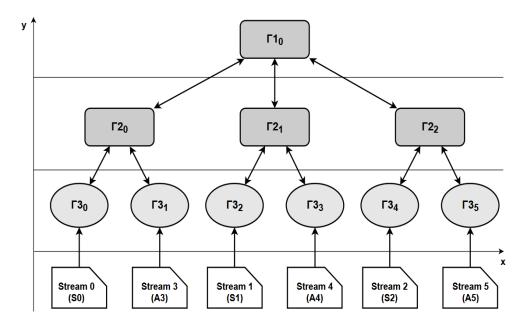

| 5.5  | Multi-level server-based hierarchy representation                                          | 76  |

| 5.6  | Hierarchical server-based framework architecture.                                          | 77  |

| 5.7  | The server-based framework employed in the INET Ethernet switch                            | 77  |

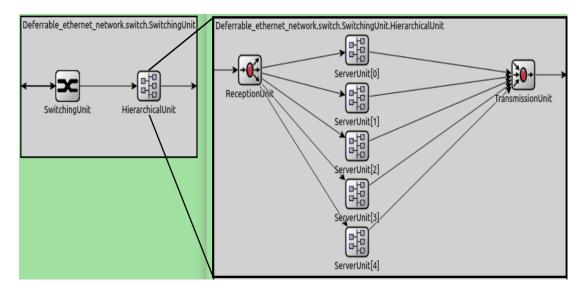

| 5.8  | Sequence Chart of the transmissions within the switch                                      | 78  |

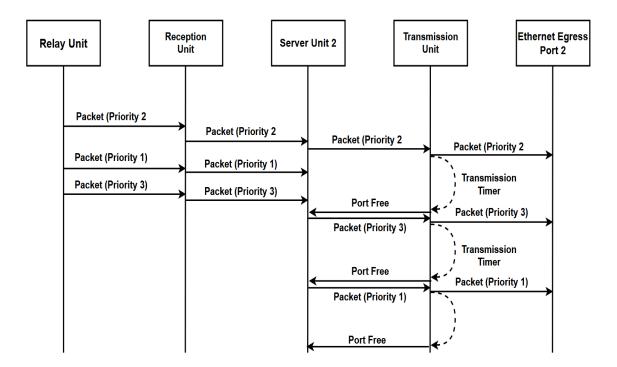

| 5.9  | Server Unit architecture                                                                   | 79  |

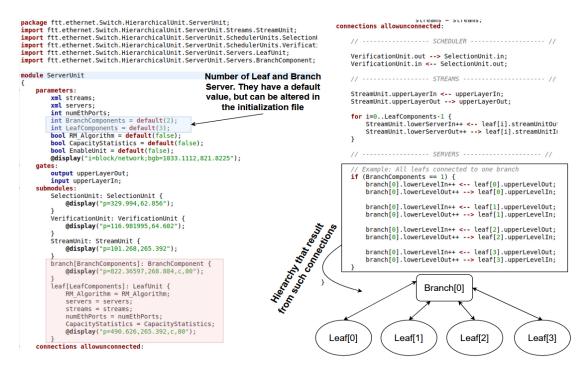

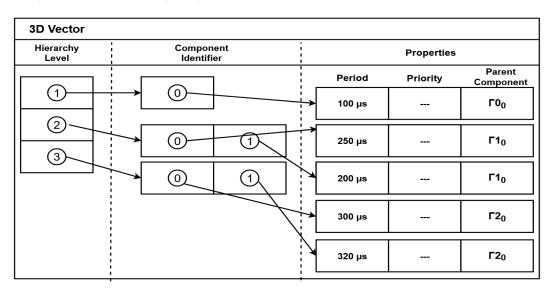

| 5.10 | ServerUnit implementation in OMNeT++ NED file                                              | 80  |

| 5.11 | StreamManagementUnit C++ class                                                             | 81  |

| 5.12 | Example of an XML file with the properties of a leaf server                                | 82  |

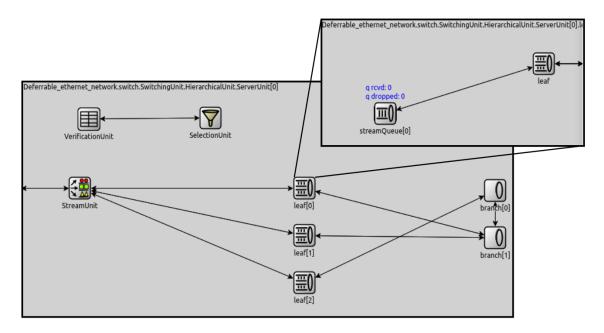

| 5.13 | ServerUnit implementation in OMNeT++                                                       | 82  |

| 5.14 | Section of the leaf components $C++$ class                                                 | 84  |

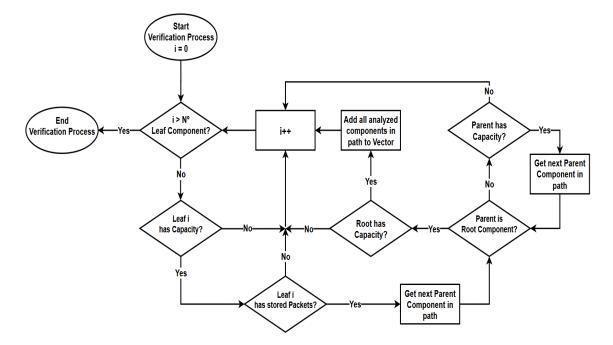

| 5.15 | VerificationUnit processing algorithm                                                      | 86  |

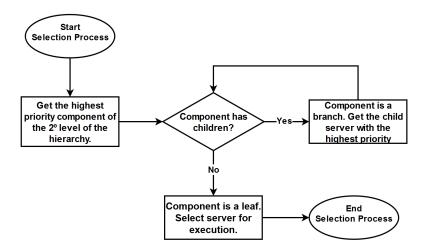

| 5.16 | VerificationUnit selection algorithm                                                       | 87  |

| 5.17 | Example of multi-level server Hierarchy                                                    | 87  |

| 5.18 | Resulting 3D Vector from the first verification process                                    | 88  |

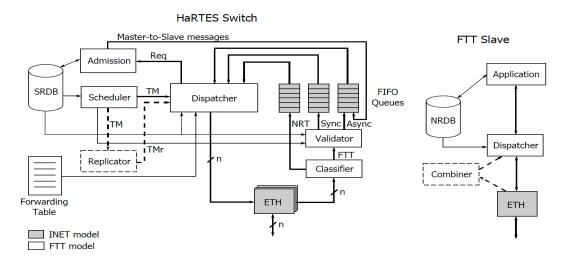

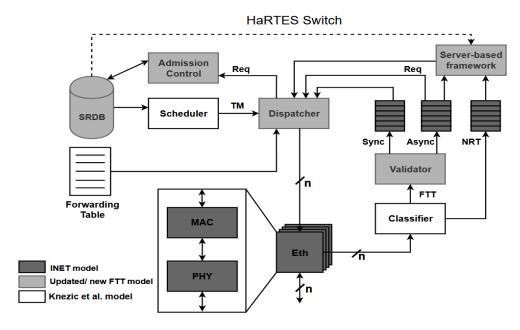

| 5.19 | HaRTES switch and FTT-slave architectures for OMNeT++ (from Knezic et al. [60], 2014).     | 89  |

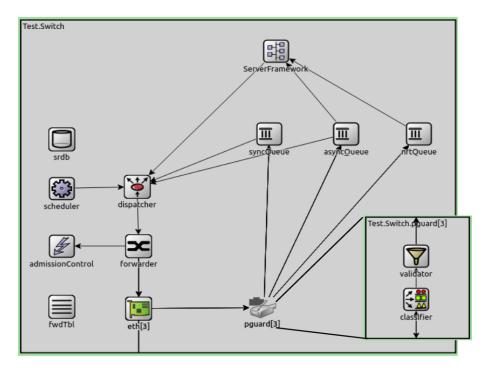

| 5.20 | Implemented HaRTES switch architecture for OMNeT++                                         | 89  |

| 5.21 | HaRTES switch in OMNeT++                                                                   | 90  |

| 5.22 | Example of an XML file with the forwarding table contents                                  | 92  |

| 5.23 | HaRTES elementary cycle structure                                                          | 93  |

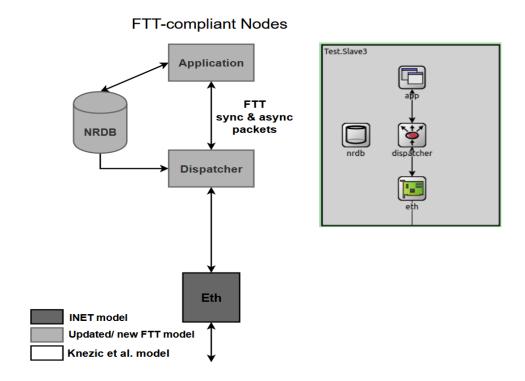

| 5.24 | FTT compliant nodes architecture                                                           | 95  |

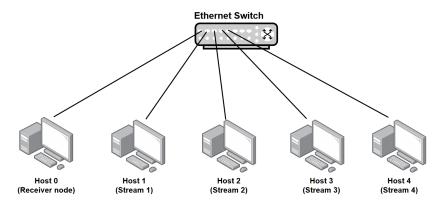

| 6.1  | Experimental setup used to validate the IEEE 802.1Q modeled switch                         | 98  |

| 6.2  | IEEE 802.1Q: Latency measurements for Experiment 1                                         | 99  |

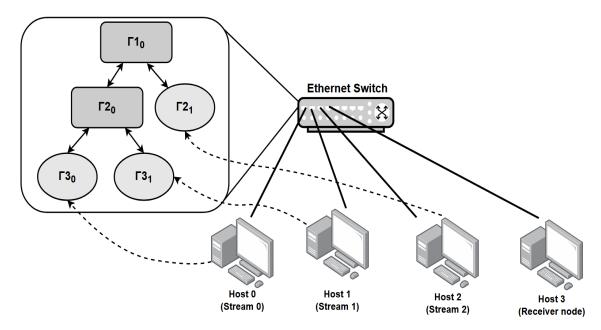

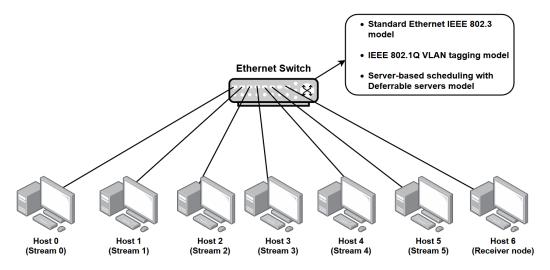

| 6.3  | Server-based scheduling: Experimental setup                                                | 101 |

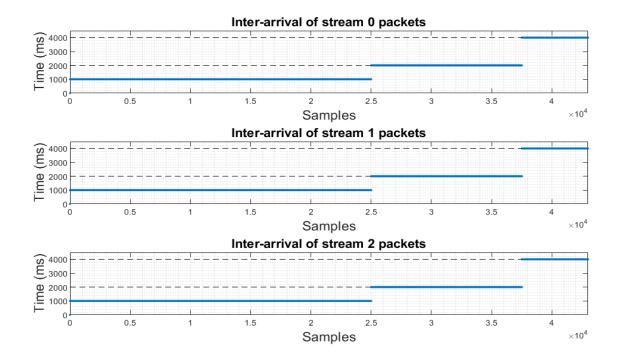

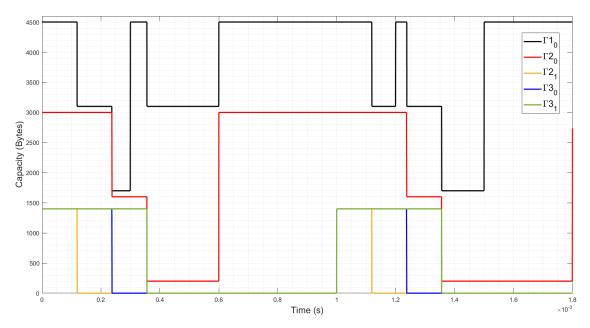

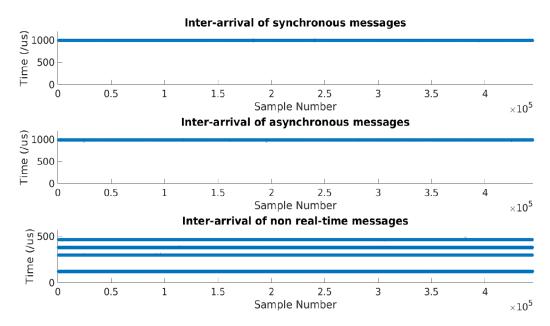

| 6.4  | Server-based scheduling: Inter-arrival timings for Experiment 1                            | 103 |

| 6.5  | Server-based scheduling: Servers' capacity over time for Experiment 1 (Mode 1)             | 104 |

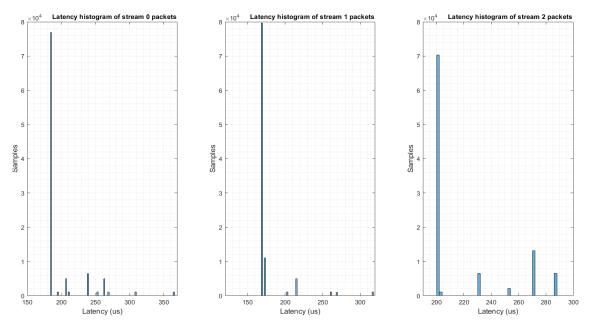

| 6.6  | Server-based scheduling: Latency Histograms in $\mu$ s                                     | 105 |

| 6.7  | Experimental setup employed to compare switch models                                       | 106 |

| 6.8  | Switch Comparison: Server-based structure employed throughout the experiments              | 107 |

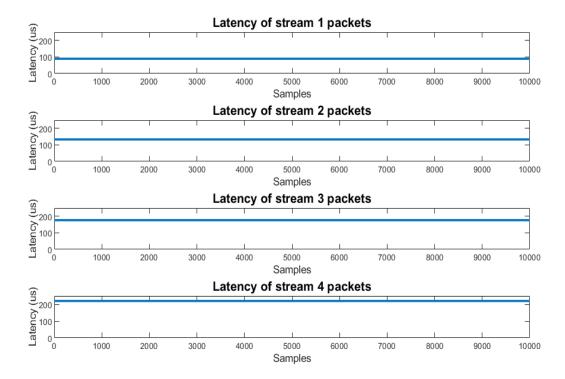

| 6.9  | 1                                                                                          | 112 |

| 6.10 | HaRTES Temporal isolation: Jitter affecting the Trigger messages                           | 113 |

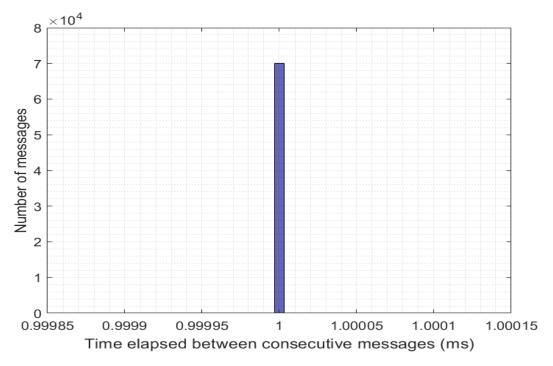

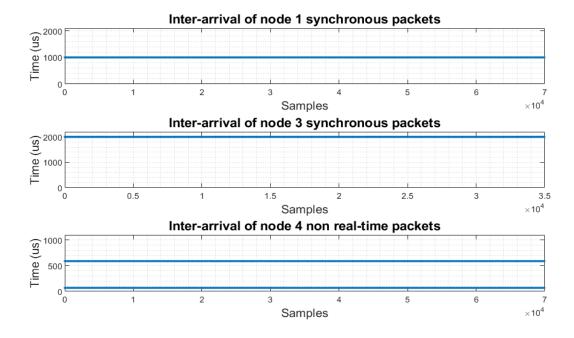

| 6.11 | HaRTES Temporal isolation: Inter-arrival values for Experiment 1                           | 113 |

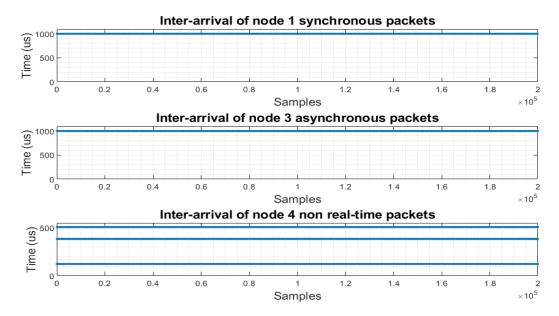

| 6.12 | HaRTES Temporal isolation: Inter-arrival timings (simulator)                               | 115 |

| 6.13 | HaRTES Temporal isolation: Inter-arrival timings (hardware) (from Luis Silva et al. [64]). | 115 |

|      | •                                                                                          | 116 |

| 6.15 | HaRTES Asynchronous Traffic confinement: Histogram of transmissions inside the EC          |     |

|      |                                                                                            | 118 |

| 6.16 | HaRTES Asynchronous Traffic confinement: Histogram of transmissions inside the EC          |     |

|      |                                                                                            | 118 |

| 6.17 | HaRTES Asynchronous Traffic confinement: Asynchronous and non-real-time traffic            |     |

|      | throughput                                                                                 | 119 |

# **List of Tables**

| 4.1  | Table with generic characteristics of different Network Simulators [32], [44], [46], [48], [50]     | 56   |

|------|-----------------------------------------------------------------------------------------------------|------|

| 4.2  | Table with the INET models for wired and wireless communications [36]                               | 67   |

| 5.1  | Properties stored in the <i>StreamManagementUnit</i>                                                | 81   |

| 5.2  | $\label{thm:continuous} VerificationUnit table with all the simulation branch servers' properties $ | 85   |

| 5.3  | VerificationUnit table with all the simulation leaf servers' properties                             | 85   |

| 5.4  | Properties stored in the SRDB/NRDB module                                                           | 91   |

| 6.1  | IEEE 802.1Q: Generated traffic properties for Experiment 1                                          | 98   |

| 6.2  | IEEE 802.1Q: Statistical values for Experiment 1                                                    | 99   |

| 6.3  | IEEE 802.1Q: Latency values for Experiment 2                                                        | 101  |

| 6.4  | Server-based scheduling: Generated traffic properties for all three modes of Experiment 1.          | 102  |

| 6.5  | Server-based scheduling: Server properties for Experiment 1                                         | 102  |

| 6.6  | Server-based scheduling: Requests to the server-based framework                                     | 103  |

| 6.7  | Server-based scheduling: Statistical values for Experiment 1                                        | 103  |

| 6.8  | Server-based scheduling: Generated traffic properties for Experiment 2                              | 105  |

| 6.9  | Server-based scheduling: Latency values for Experiment 2                                            | 105  |

| 6.10 | Switch Comparison: Generated traffic properties in the experimental scenarios                       | 107  |

| 6.11 | Switch Comparison: Servers' properties throughout all four experiments                              | 107  |

| 6.12 | Switch Comparison: Experiment 1 results                                                             | 108  |

| 6.13 | Switch Comparison: Streams' modifications                                                           | 109  |

| 6.14 | Switch Comparison: Experiment 2 results with the highest priority stream (S0) altered               | 109  |

| 6.15 | Switch Comparison: Experiment 2 results with an intermediate highest stream (S1) altered.           | 110  |

| 6.16 | Switch Comparison: Experiment 2 results with a lower priority stream (S2) altered                   | 110  |

| 6.17 | HaRTES Temporal isolation: Generated traffic properties for both experiments                        | 112  |

| 6.18 | HaRTES Temporal isolation: Assigned reservations properties for Experiment 2                        | 114  |

| 6.19 | HaRTES Temporal isolation: Observed values for Experiment 2                                         | 115  |

| 6.20 | HaRTES Asynchronous Traffic confinement: Generated traffic properties for both experiments.         | .117 |

| 6.21 | HaRTES Asynchronous Traffic confinement: Assigned reservations properties for Experi-               |      |

|      | ment 1                                                                                              | 117  |

# **Glossary**

| ART            | Asynchronous Requirements Table                           | LAN                    | Local Area Networks            |

|----------------|-----------------------------------------------------------|------------------------|--------------------------------|

| $\mathbf{AW}$  | Asynchronous Window                                       | MAC                    | Media Access Control           |

| CAN            | Controller Area Network                                   | $\mathbf{mit}$         | Minimum Interarrival Time      |

| COTS           | Commercial-Of-The-Shelf                                   | NED                    | Network Description            |

| CSMA/CD        | Carrier-Sense Multiple-Access with<br>Collision Detection | NRT                    | Non real-time                  |

| DES            | Destributed Embedded Systems                              | OSI                    | Open Systems Interconnection   |

| $\mathbf{DM}$  | Deadline Monotonic                                        | $\mathbf{QoS}$         | Quality-of-Service             |

| $\mathbf{DS}$  | Deferrable Server                                         | $\mathbf{R}\mathbf{M}$ | Rate Monotonic                 |

| DRTS           | Distributed Real-Time Systems                             | $\mathbf{SLA}$         | Service Level Agreement        |

| $\mathbf{EC}$  | Elementary Cycle                                          | SRDB                   | System Requirements Database   |

| $\mathbf{EDF}$ | Earliest Deadline First                                   | SRT                    | Synchronous Requirements Table |

| EDP            | Explicit Deadline Periodic                                | $\mathbf{s}\mathbf{w}$ | Synchronous Window             |

| ET             | Event-Triggered                                           | TM                     | Ų.                             |

| FCFS           | First-Come First-Served                                   |                        | Trigger Message                |

| $\mathbf{FTT}$ | Flexible Time-Triggered                                   | TT                     | Time-Triggered                 |

| FTTRS          | Flexible-Time-Triggered Replicated                        | TS                     | Timeline Scheduling            |

|                | Star                                                      | TSN                    | Time-Sensitive Networking      |

| FTT-SE         | Flexible Time-Triggered Switched<br>Ethernet              | VID                    | Virtual Local Area             |

| II DODG        |                                                           |                        | Network (VLAN) Identifier      |

| HaRTES         | Hard Real-Time Ethernet Switch                            | VLAN                   | Virtual Local Area Network     |

| HSF            | Hierarchical Scheduling Framework                         | WCET                   | Worst-Case Execution Time      |

| IDE            | Integrated Development<br>Environment                     | WCRT                   | Worst-Case Response Time       |

CHAPTER 1

## Introduction

#### Contents

| 1.1 | Problem Statement | 1        |

|-----|-------------------|----------|

| 1.2 | Objectives        | 2        |

| 1.3 | Document Outline  | <b>2</b> |

The concept of Industry 4.0 is used to describe the current industrial revolution which proceeds the three previous ones. In the 18th century, the shift from manual labor to mechanical production, through steam and water power, led to the first industrial revolution. The second industrial revolution occurred during the late 19th century, with the introduction of electricity in the manufacturing process which improved the production by creating assembly lines. Throughout the 1970s, the third revolution stemmed from the introduction of digital electronics and communication technologies in the industrial sector. Industry 4.0 forecasts the digitalization of the industrial process using three major technologies: Internet- of-Things, Cyber-Physical Systems and Cloud Computing. In this transformation, computer systems, sensors and intelligent machines are integrated into a single network, also known as Industrial Internet-of-Things (IIoT). As several connected systems can interact with each other, exchanging information grants more flexibility and autonomy to factories with machines autonomously analyzing data, predicting failures and self-reconfigure when necessary. Besides gains in flexibility, Industry 4.0 has significant improvements in efficiency and cost reduction, productivity, human-machine interaction and product quality.

#### 1.1 Problem Statement

Although the notion of Industrial Internet of Things offers considerable advantages for industrial sector, the need to interconnect the factory different components makes the requirements of industrial communication networks increasingly demanding. As the exchange of real-time information between the several applications is essential for the accuracy and correctness of the system, the implementation of a communication system that guarantees their timeliness requirements, is a crucial process in the development of this kind of networks.

Among the different industrial communication infrastructures employed over the years, Ethernet quickly became the most widely used due to several advantages that the protocol

provided. As the non-deterministic arbitration mechanisms of standard Ethernet did not guarantee the capability of meeting the, often strict, real-time requirements of industrial applications, several researchers strived to add support for real-time traffic over switched Ethernet. Such technologies include Time-Sensitive Networking (TSN) and Hard Real-Time Ethernet Switch (HaRTES) protocols. However, the process of developing and testing industrial networks using physical hardware can be complex, expensive and, for certain case studies, considerably limited. The development of network simulators allows to circumvent these issues. The creation of software models of the prototypes used in the industrial sector makes the process of designing industrial networks significantly easier, cheaper and faster. This work aims to integrate technologies from Industry 4.0 and network simulators with the development of a HaRTES switch simulation model for industrial real-time networks.

### 1.2 Objectives

The main objectives of this dissertation are:

- Study of industrial real-time Ethernet protocols, focusing on technologies that use the FTT paradigm;

- Survey of network simulators used in the scope of industrial applications and selection of one of them;

- Implementation of simulation models for real-time Ethernet switches and their subsequent validation;

- Analysis of the retrieved results.

#### 1.3 Document Outline

This dissertation is organized as follows:

- Chapter 2: starts by introducing some concepts regarding real-time systems and scheduling techniques for both synchronous and asynchronous real-time traffic. Then, it addresses the Ethernet protocol and presents some existing real-time technologies based on Ethernet switching.

- Chapter 3: is dedicated to the FTT-enable switch, HaRTES. It starts by introducing the FTT paradigm and its implementation over switched Ethernet, the FTT-SE protocol. Then discusses the objectives and architecture of the new switch and compares it to its previous technology. Lastly, some improvements performed over the HaRTES are presented.

- Chapter 4: presents some of the most commonly used network simulators and compares them to find the best candidate to implement the proposed switch. The chapter finishes with a detailed description of the selected simulator.

- ullet Chapter 5: describes the created simulation models and their components.

- ullet Chapter 6: is dedicated to the experiments conducted to validate the developed models and the result analysis.

- *Chapter* 7: presents the conclusions of the dissertation and some possible lines for future research.

# Theoretical Real-Time and Ethernet concepts

| Contents |                     |                                            |  |  |

|----------|---------------------|--------------------------------------------|--|--|

| 2.1      | Real-T              | Time Systems                               |  |  |

|          | 2.1.1               | Classification of real-time systems        |  |  |

|          | 2.1.2               | Task Model                                 |  |  |

|          | 2.1.3               | Scheduling                                 |  |  |

|          | 2.1.4               | Schedulability Analysis                    |  |  |

|          | 2.1.5               | Hierarchical Scheduling                    |  |  |

| 2.2      | Time communications |                                            |  |  |

|          | 2.2.1               | Communication paradigms                    |  |  |

| 2.3      | B Ethernet          |                                            |  |  |

|          | 2.3.1               | Ethernet Frame                             |  |  |

|          | 2.3.2               | Ethernet Switch                            |  |  |

| 2.4      | Real-ti             | ime protocols over Ethernet                |  |  |

|          | 2.4.1               | Real-time protocols on COTS switches       |  |  |

|          | 2.4.2               | Real-time protocols on customized hardware |  |  |

This chapter presents some basic concepts regarding real-time systems and the Ethernet protocol, which are fundamental for understanding concepts introduced throughout this dissertation. It initiates with the discussion of real-time scheduling algorithms and communications. The chapter closes with the presentation of Ethernet technologies and real-time communication protocols over the Ethernet switch.

## 2.1 Real-Time Systems

Sectors such as chemical, nuclear and flight control, automotive applications and military systems potentially experience extreme consequences when the timeliness constraints of their systems are not met [1]. Therefore, when designing these systems, i.e., *real-time systems*, besides having to consider the correctness of the computed results, also required to guarantee

that computations, as well as communications, for the case of distributed real-time systems, satisfy specific timing requirements, being *deadline* one of the more common ones.

#### 2.1.1 Classification of real-time systems

In real-time systems, computational activities are described as a set of real-time tasks. Each task is commonly characterized by its individual *deadline*, a constraint that restricts the task response time, and can be classified depending on the consequences of a missed deadline [1]:

- Soft: When a task misses a deadline produces, it might produce useful results for the system, although the delay may cause degradation to its quality and performance.

- **Firm:** The tasks results after a missed deadline have no utility for the system. Despite there may be some performance degradation, these are tolerable depending on their frequency, but there are no catastrophic consequences that result from such events.

- Hard: The tasks results after a missed deadline are useless. Furthermore, catastrophic consequences, such as human losses or significant costs, may emerge.

Depending on the type of task handled, real-time systems can then be classified as [1]:

- Soft Real-Time: Systems that only handle firm and/or soft real-time tasks. These are usually used in applications where the miss of a deadline is less critical such as video/audio encoding and decoding, video streaming and image processing.

- Hard Real-Time: Systems that execute at least one hard real-time task. Also known as **safety-critical systems**, these are used in several activities: missile control, airplane control and nuclear plant control.

Real-time systems are generally associated with a set of tasks. Tasks can normally have three different constraints [1]: **temporal constraints**, **precedence constraints** and **resources constraints**.

- **Temporal constraints**: typically associated with each task's *deadline*. However, it can also be correlated to the *window* (Upper and lower bounds in which a task must finish its execution), *synchronization* (Temporal boundary of the difference between two generated events), or the *distance* of a task (time limit between completion and consequent activation).

- Precedence constraints: associated with the order that the tasks are executed. If a task  $(T_a)$  can only execute after another task  $(T_b)$  finishes,  $T_b$  is specified as the predecessor of  $T_a$ . If a task has no predecessors, it is nominated as beginning task whereas tasks with no successors are called ending tasks.

- Resources constraints: applied to a set of tasks whenever they must access the same resource (*shared resource*) to continue their execution. For such cases it is necessary to ensure that it is not accessed simultaneously by multiple tasks (*mutual exclusion*).

The previously explained constraints will influence the moment when tasks are executed. Real-time systems have an entity responsible for selecting the following task to execute from a current set which is designated *scheduler*. It is possible to perform a *scheduling analysis* to assess, if a given task set is *schedulable* (there is at least one feasible schedule), and then arrange the task order by applying *scheduling algorithms*. Besides the scheduler, a generic real-time system/kernel has the subsequent components [2]:

- Task Manager: responsible for creating, deleting, setting the initial activation and updating each task state.

- **Time Manager:** accountable for activating the tasks, verifying time constraints and measure time intervals.

- Resource Manager: grants mutual exclusion of a shared resource to the tasks (mutexes, semaphores, etc.).

- Task Dispatching: picks the selected task from the scheduling process and puts it in execution.

Even though a real-time system is formed by multiple entities, the scheduler is the one that requires more attention because it is the responsible structure for implementing complex algorithms that arrange the execution order of a task set. The following sections briefly explain several real-time scheduling concepts.

#### 2.1.2 Task Model

A task [1] is a computational process that performs a specific instruction executed by the CPU. It can be classified as *periodic*, *aperiodic* and *sporadic* depending on its activation. Periodic tasks arrive regularly with a fixed time interval between two consecutive activations (*inter arrival-time*). Sporadic tasks are also activated regularly but with a minimum inter arrival-time instead of a fixed one. Finally, for aperiodic tasks, their arrival cannot be predicted nor constrained and can only be characterized by probabilistic means.

A set of periodic tasks can be characterized by the following model:

$$\Gamma = \{ \tau_i(C_i, T_i, \phi_i, D_i, Pr_i), i = 1, 2, ..., n \}$$

(2.1)

where:

- $C_i$  is the worst case computation time required to compute task  $\tau_i$ , also designated as Worst-Case Execution Time (WCET);

- $T_i$  is the period of task  $\tau_i$ ;

- $\phi_i$  is the initial phase of task  $\tau_i$  (the task first activation offset time);

- $D_i$  is the relative deadline of task  $\tau_i$ ;

#### • $Pr_i$ is the priority of task $\tau_i$ ;

The release/activation time  $(r_{i,k}/a_{i,k})$  and absolute deadline  $(d_{i,k})$  of the  $k^{th}$  instance of a task  $\tau_i$  can be computed as:

$$r_{i,k} = \phi_i + (k-1)T_i, \quad i \in \mathbb{N}$$

$$(2.2)$$

$$d_{i,k} = r_{i,k} + T_i = \phi_i + kT_i, \quad i \in \mathbb{N}$$

$$(2.3)$$

The model (2.1) can be applied to sporadic tasks if the period parameter  $(T_i)$  is changed to the minimum inter-arrival activation time  $(Tmit_i)$  and the phase parameter  $(\phi_i)$  is excluded:

$$\Gamma = \{ \tau_i(C_i, Tmit_i, D_i, Pr_i), i = 1, 2, ..., n \}$$

(2.4)

For aperiodic tasks, the release instant and absolute deadline value can be computed as follows:

$$r_{i,k} \ge r_{i,k-1} + Tmit_i, \quad i \in \mathbb{N}$$

(2.5)

$$d_{i,k} = r_{i,k} + D_i, \quad i \in \mathbb{N} \tag{2.6}$$

#### 2.1.3 Scheduling

In real-time systems, the scheduler is responsible for assigning each task execution (scheduling) by applying different algorithms and rules (scheduling algorithms). According to [1], the scheduler requires three sets to create a schedule: a set of n tasks  $\Gamma = \{\tau_1, \tau_2, ..., \tau_n\}$ , a set of m processors  $P = \{P_1, P_2, ..., P_n\}$  and a set of s types of resources  $R = \{R_1, R_2, ..., R_n\}$ . Besides these, precedence relations between tasks can be specified through cyclic graphs. The scheduler ensures the execution of all tasks under the imposed constraints by assigning processors from P and resources from R to tasks from  $\Gamma$ . Real-time scheduling algorithms can be classified as [1]:

#### • Preemptive vs Non Preemptive:

- In preemptive algorithms, a task execution can be interrupted by assigning the processor to another one..

- In non-preemptive algorithms, a task always completes its execution when it is assigned to the processor.

#### • Static vs Dynamic (priorities):

- In Static priority algorithms, the scheduler selects the task order based on their fixed priorities. These are assigned to each task before their release.

- In Dynamic priority algorithms, the task's priorities may vary through the system execution, and the scheduling is based on these changeable parameters.

#### • Offline vs Online:

- In Offline scheduling, the scheduling algorithm is applied to the task set before their activation. The generated scheduler is then stored and executed during run-time.

- In Online scheduling, all the scheduling decisions are made in run-time, whenever a task completes its execution or a new one is added to the task set.

#### • Optimal vs Sub-Optimal/Heuristic:

- A scheduling algorithm is optimal if it minimizes the cost function assigned to the task set. However, if the cost function was not defined, an optimal scheduling algorithm is one able to find a feasible schedule for the task set, provided that one exists, computed with an algorithm of the same class.

- A heuristic algorithm is one that tends to find the optimal schedule using heuristic functions.

A common taxonomy used for real-time scheduling is illustrated in Figure 2.1. The algorithms are generally divided into *online* and *offline* scheduling, with offline being more suitable for complex algorithms with high computational requirements. However, it is less flexible as, unlike online scheduling, it does not support changes that may occur in the system. Regarding online scheduling, it can be further classified depending on the priorities assigned to the tasks: *static* or *dynamic*. Both these categories can be *preemptive* or *non-preemptive*.

Figure 2.1: Scheduling algorithms.

#### 2.1.3.1 Periodic Task Scheduling

The following segments present some of the most used techniques [1]: Timeline Scheduling (TS), Rate Monotonic (RM), Deadline Monotonic (DM) and Earliest Deadline First (EDF).

#### 2.1.3.1.1 Offline Scheduling

#### Timeline Scheduling

Timeline Scheduling (TS) [1], also known as Cyclic Executive, is a scheduling algorithm that splits the time interval assigned to the tasks execution in equal segments of time (time slots). Each task is allocated to a given time slot in a way that all their requirements (frequency and deadline) are respected. In the TS algorithm, a time slot is denominated Minor Cycle, whereas the hyperperiod (minimal time interval from which the scheduler repeats itself) is designated Major Cycle. Prior to the system's execution, a schedule, in which all the tasks are associated with Minor Cycles for a whole Major Cycle, is created and stored in a scheduling table. The dispatcher then uses it and executes each task in their predetermined Minor cycle. Even though this type of scheduling algorithm has a low complexity level, being an offline technique makes it limited in terms of flexibility.

#### 2.1.3.1.2 Online Scheduling

#### Fixed Priorities - Rate Monotonic

Rate Monotonic (RM) [3] is an online preemptive algorithm based on fixed priorities where task's priorities  $(P_i)$  are assigned monotonically based on their periods, with lower periods corresponding to higher priorities:

$$\forall_{\tau_i, \tau_j} \in \Gamma : T_i < T_j \to P_i > P_j \tag{2.7}$$

Since it is an online technique, whenever a new task is activated or a running one completed, the scheduler must select, at run-time, the task with the shortest period in the set for execution. Furthermore, as the RM is a preemptive algorithm, running tasks can be interrupted if a new one with a shorter period is activated. The Rate Monotonic was proven to be the optimal algorithm among all the fixed-priorities techniques by Liu and Layland [3], for  $D_i = T_i$ . They demonstrated that any fixed-priority scheduling algorithm can only schedule a task set if it is schedulable with RM.

#### Fixed Priorities - Deadline Monotonic

The Deadline Monotonic (DM) algorithm was created as an extension of Rate Monotonic by Leung and Whitehead [4]. It is an online technique with fixed priorities in which tasks have relative deadlines shorter or equal to their periods, i.e.,  $C_i \leq D_i \leq T_i$ . Following the DM scheduling, priorities are monotonically assigned according to the relative deadlines  $(D_i)$ , with tasks with lower deadlines being assigned higher priorities. Similar to Rate Monotonic, the Deadline Monotonic is also a preemptive algorithm, meaning that an executing task can be interrupted when a new one with a lower deadline is activated. Furthermore, the DM algorithm was also proven to be an optimal fixed-priority algorithm by Liu and Layland [3], meaning that the fixed-priority scheduling conditions applied to RM are also used in this algorithm.

#### Dynamic Priorities - Earliest Deadline First

The Earliest Deadline First (EDF) [3] is a preemptive technique based on dynamic priorities in which the tasks relative deadlines are equal to their periods:  $\forall_{\tau_i \in \Gamma} : D_i = T_i$ . In EDF, the tasks priorities are assigned according to their absolute deadlines  $(d_i)$ , i.e., tasks with earlier deadlines relatively to the current execution time assigned higher priorities:

$$\forall_{\tau_i, \tau_j} \in \Gamma_{T_a} : d_i < d_j \to P_i > P_j, \quad T_a \in \mathbb{R}$$

(2.8)

where  $\Gamma_{T_a}$  is subset of  $\Gamma$ , composed by ready tasks at the time instant  $T_a$ , and  $(d_i, d_j)$  the absolute deadlines at  $T_a$  for both tasks  $\tau_i$  and  $\tau_j$ . Comparing to the Rate Monotonic scheduling algorithm, the EDF is capable of achieving higher utilization factors while reducing the preemption levels of the overall system and guaranteeing timeliness. Nonetheless, it is a more complex technique, which can be problematic for systems with low processing power due to the algorithm's high run-time overhead.

#### 2.1.3.2 Aperiodic Task Scheduling

Asynchronous tasks [1], commonly external to the system, are event-triggered based and cannot be controlled by the scheduler. Hence, in order to maintain the real-time system requirements, with the integration of both synchronously and asynchronously task sets, some mechanisms are applied to the latter so that their overall interference can become predictable (deterministic) or, at least, bounded.

For that purpose, two types of techniques were created, one based on fixed priorities and the other on dynamic priorities. Some of these algorithms will be presented in the following segments.

#### 2.1.3.2.1 Background Scheduling

In Background Scheduling [1], the aperiodic traffic is only processed when there are no periodic tasks ready to execute. Although this procedure makes this algorithm very simple, there are no guarantees that the time constraints of the aperiodic jobs will be satisfied, particularly in high periodic load systems. Therefore, this method should only be used for aperiodic task sets with limited timeless constraints and low periodic loads.

#### 2.1.3.2.2 Server-based Scheduling

Server-based scheduling [1] is a technique that makes use of a periodic task (server) to act as a proxy of associated sporadic or aperiodic tasks. A server can be described by a given period  $T_s$ , and an execution time  $C_i$  (server capacity or budget). The server is scheduled just like a regular periodic task by the scheduler and, when active, allows requests execution made by aperiodic or sporadic tasks within its budget.

The server-based scheduling mechanisms are divided into static and dynamic priority scheduling. Some of the static-priority most well-known algorithms are [1]:

- Polling Server (PS): The polling server activates every  $T_s$ , replenishes its capacity, and executes any aperiodic requests within its budget. If the server capacity is exhausted or there are no requests during its activation, it suspends and loses all its budget (if it has any). Aperiodic requests that arrive during the suspended state must wait for the replenishment in the next activation state. In a polling server, whenever a task execution time surpasses the server capacity, it is suspended. Thus, the interference caused by both aperiodic and periodic tasks is the same. As requests that arrive after the server activation must wait to be processed, even if there are no other higher priority active tasks, the general response time of this server is not satisfactory.

- **Deferrable Server (DS):** The deferrable server is an algorithm also characterized by a periodic replenishment with period  $T_s$  and execution time  $C_i$ . Similar to a Polling Server, a DS executes aperiodic requests within its budget, which is replenished periodically. However, in this case, instead of depleting its capacity in the absence of requests, the server preserves its budget until each period completion or its exhaustion. This improvement allows better response times compared to the Polling Server. Nevertheless, the possibility for aperiodic tasks to execute at any point within the server period causes a drawback in the schedulability of the periodic traffic.

- Sporadic Server (SS): Similar to the deferrable server, the sporadic server preserves its capacity until it is exhausted by aperiodic requests. The main difference is that, in this server type, the server capacity budget is only replenished when it is used. These procedures reduce the sporadic server impact when scheduling periodic tasks. The main disadvantage is the complexity of its implementation.

- Priority Exchange (PE): Akin to the polling server, at the beginning of each period  $(T_s)$ , the priority exchange server replenishes its capacity and checks for aperiodic requests. These servers are modeled as high priority tasks and can exchange their budget with low priority ones. If the server has the set highest priority, it executes all pending aperiodic requests within its budget. On the other hand, in the presence of higher priority periodic tasks, the server grants its budget for the task execution. This type of mechanism improves the schedulability. However, it increases the complexity and worsens the response time.

Dynamic priority server scheduling is not implemented in the HaRTES architecture. Nevertheless, for the sake of completeness, two types of schedulers will be explained [1]:

• Total Bandwidth Server (TBS): The total bandwidth server is a dynamic priority-based algorithm implemented to overcome the Sporadic Server limitation regarding the requests delays, which result from long server periods. The main concept of the TBS is that, while handling the aperiodic workload, the processor utilization never exceeds a defined bound  $U_s$ . In this algorithm, whenever a new aperiodic task is added to the

system at  $t = r_k$ , it receives the total server bandwidth, if possible. The deadline  $d_k$  assigned to the  $k_{th}$  request that arrived at  $r_k$  is computed as:

$$d_k = \max(r_k, d_{k-1}) + \frac{C_k}{U_s}$$

(2.9)

where  $C_k$  is the request execution time and  $U_s$  the server utilization factor (bandwidth). Upon receiving a deadline, the tasks are inserted into a queue where they are treated as normal periodic tasks to be scheduled by the EDF algorithm. Although the average response time for aperiodic tasks is smaller, when comparing to other dynamic/static priority servers, Spuri and Buttazzo [1] proved that a set of n periodic tasks with a utilization rate of  $U_p$  is only schedulable with the EDF by the TBS with a utilization factor of  $U_s$  when:

$$U_p + U_s \le 1 \tag{2.10}$$

The main advantages of this server are its simplicity and low overhead. On the other hand, it requires a priority knowledge of the server capacity and is vulnerable to overruns.

- Constant Bandwidth Server (CBS): The constant bandwidth server is a dynamic priority-based server. The CBS algorithms guarantee that a server contribution to the total utilization factor is always smaller than the total possessed bandwidth  $(U_s)$ , even in the occurrence of overheads. A constant bandwidth server is characterized by a budget  $c_s$  and a pair of values  $(T_s, Q_s)$ , where  $Q_s$  is the maximum budget and  $T_s$  the server period. The server bandwidth  $(U_s)$  is computed as:  $U_s = \frac{Q_s}{T_s}$ . When a request is added to the system, a mew scheduling deadline is assigned and afterwards stored in an EDF queue. While executing, whenever a task demands more bandwidth than the reserved (executes more than expected), its deadline is postponed, i.e., the tasks priority decreases due to the EDF rules. By doing so, the task interference on the overall workload is reduced. The CBS algorithm is defined as follows:

- At each instant, a deadline  $d_{s,k}$  is associated to the server and, at the beginning,  $d_{s,0} = 0$ .

- All of the servers jobs  $J_{i,j}$  receive dynamic deadlines  $d_{i,j}$ , which are equal to the servers deadline, i.e.,  $d_{i,j} = d_{s,k}$ . Whenever a job is executed, the server budget  $(c_s)$  is decreased by the same amount.

- When the server total budget is depleted  $(c_s = 0)$ , it is recharged with the maximum valued pre-defined  $c_s = Q_s$ , and a new server deadline is generated:  $d_{s,k+1} = d_{s,k} + T_s$ .

- A constant bandwidth server is defined as *active* at a time instant t if there is at least one pending job  $J_{i,j}$  so that  $r_{i,j} \leq t < f_{i,j}$ , otherwise is said to be *idle*. Note that  $r_{i,j}$  is the instant the job  $J_{i,j}$  arrives and  $f_{i,j}$ , the worst-case finish time of the respective job.

- Whenever the server is active and a job  $J_{i,j}$  arrives, it is stored in a queue of pending requests.

- At any time the server is idle and a job  $J_{i,j}$  arrives, the server's deadline  $d_{s,k}$  is computed as follows:

if

$$c_s \ge (d_{s,k} - r_{i,j})U_s$$

, the deadline  $d_{s,k}$  stays equal otherwise a new one is generated  $d_{s,k+1} = r_{i,j} + T_s \wedge c_s = Q_s$

After a job is finished, the next pending request is assigned to the current budget and deadline. If there are no requests, the server becomes idle.

Compared to a TBS, CBS has higher complexity due to the dynamic capacity management with similar response times for aperiodic requests. However, it has better performance whenever the tasks WCET has a high variance. A set of n periodic hard tasks, with a utilization factor  $U_p$  only can be schedulable with the EDF algorithm, using a set of m constant bandwidth servers with a processing factor  $U_s = \sum_{i=1}^m U_{si}$ , if condition (2.10) is verified.

#### 2.1.4 Schedulability Analysis

Schedulability analysis is a computation performed by the scheduler and allows to determine, a priori, if a task set is feasible, i.e., all the time constraints of each task will be met. In [1], the most distinguished approaches are based on the *utilization rate* and *response time*. The former has generally lower computational complexity but is more pessimistic when compared to other approaches. Response time analysis tests are more complex, thus require systems with higher computational power. Nonetheless, they tend to be less pessimistic, providing more precise results.

#### 2.1.4.1 Utilization based tests

Utilization tests are based on the fraction of time a processor spends to execute a task set  $\Gamma = \{\tau_1, \tau_2, ..., \tau_n\}$ . This factor, generally represented as U, is calculated by the sum of each tasks contribution  $(u_{\tau_i})$ :

$$u_{\tau_i} = \frac{C_i}{T_i} \tag{2.11}$$

For a uniprocessor system with n tasks, the utilization factor can be computed as:

$$U = \sum_{i=1}^{n} \left(\frac{C_i}{T_i}\right) \tag{2.12}$$

By calculating this value, and comparing it to a certain threshold, it is possible to confirm if the task set is schedulable. This bound depends on the system characteristics (task set deadlines, periods and applied scheduling algorithm).

In their study, Liu and Layland [3], proved that, for uniprocessor systems, any task set  $\Gamma$  of n periodic and independent tasks can be schedulable with the RM policy if the following inequality is verified:

$$U \le n(2^{\frac{1}{n}} - 1) \tag{2.13}$$

#### 2.1.4.2 Response Time based tests

Response time based tests are associated with the Worst-Case Response Time (WCRT), i.e., the maximum interval between arrival and finish time of a task. For each task, the scheduler verifies if the WCRT is higher than their respective deadline and, if it occurs at least once, the entire set is not schedulable.

For fixed-priority preemptive systems, Joseph and Pandya [5], showed that, for a periodic task  $\tau_i$ , its longest response time  $R_i$  is obtained by the sum of its computation time  $C_i$  and the amount of interference that it can suffer from higher priority tasks in the system  $I_i$ :

$$R_i = C_i + I_i \tag{2.14}$$

The maximum amount of interference occurs when a task  $\tau_i$  and the remaining higher priority tasks (hp(i)) are released at the same time, also know as *critical instant*:

$$I_{i} = \sum_{\forall j \in hp(i)} \left( \left\lceil \frac{R_{i}}{T_{i}} \right\rceil \times C_{j} \right) \tag{2.15}$$

Computing equations (2.14) and (2.15) results:

$$R_i = C_i + \sum_{\forall j \in hp(i)} \left( \left\lceil \frac{R_i}{T_i} \right\rceil \times C_j \right)$$

(2.16)

Equation (2.16) can be solved by the following iteration method:

$$R_i^{n+1} = C_i + \sum_{\forall j \in hp(i)} \left( \left\lceil \frac{R_i^n}{T_i} \right\rceil \times C_j \right)$$

(2.17)

The iteration starts at  $R_i^0$  and stops when  $R_i^{n+1} = R_i^n$  or when  $R_i^n > D_i$ , i.e., when the longest response time exceeds the task deadline. Audsley et.al [6] improved this analysis in order to address the non-preemption effects of resource sharing. In this analysis, equation (2.14) is reformulated by adding a blocking factor caused by lower priority tasks  $B_i$ :

$$R_i = C_i + I_i + B_i \tag{2.18}$$

The blocking factor can be solved as:

$$B_{i} = \begin{cases} 0, & lep(i) = \emptyset \\ max_{j \in lep(i)} \{C_{j}\} & lep(i) \neq \emptyset \end{cases}$$

$$(2.19)$$

where lep represents the set of tasks with lower priority than  $\tau_i$

It is important to highlight that, for this analysis, the *critical instant* is different due to the blocking factor. Now it happens when both  $\tau_i$  and the remaining higher priority tasks are released, immediately afterward a lower priority task that blocks  $\tau_i$  starts its execution.

# 2.1.5 Hierarchical Scheduling

Hierarchical scheduling or *Hierarchical Scheduling Framework (HSF)* [7], [8], are techniques implemented to simplify issues imposed by systems with global scheduling analysis. Apart from their complexity, these systems are more suitable for situations when the information about the systems applications established are a priori (closed systems). Nonetheless, there are multiple sectors where closed systems are not fitting as they are unable to execute applications during run-time that have not been scheduled together with the current set. Thus, different methodologies such as HSF were developed to overcome these problems.

Hierarchical scheduling allows fragmentation of global and complex systems into a set of subsystems whose individual analysis simplifies the scheduling problem. A hierarchical scheduling framework is typically represented as a tree, similar to the ones used in data structures (binary trees). Each component/subsystem is represented by nodes. These are independent structures hence, they all have individual schedulers to schedule their local task set. Each component also includes an interface that simplifies the integration of different nodes in the system by modeling their individual requirements into a single real-time requirement. Furthermore, it is also used to allocate resources between different hierarchy levels (parent  $\rightarrow$  child).

According to Shin and Lee [7], [8], the following properties must be verified in any hierarchical scheduling framework:

- **Independence:** each node schedulability analysis must be performed independently to all other components of the same hierarchical level.

- **Separation:** the interaction between parent and child nodes is made through an interface that abstracts their inner complexity.

- Universality: all the components are independent. Thus any scheduling algorithm can be applied to them.

- Composability: the scheduling analysis of a parent component considers all its children's requirements. As such, these are only schedulable if all their children's time requirements are satisfied.

These properties are feasible using techniques based on server architectures as they have efficient methodologies to control resource distribution. Such scheduling techniques provide transparency when allocating virtual resources (fraction of the capacity of the corresponding hardware resources) to the components of the hierarchy. Consequently, server-based structures can be considered suitable for component-based scheduling interfaces.

A model for the construction of HSF was presented by Shin and Lee [7], [8]. In this model, a component C is defined as a triplet (W, R, A), where W represents the workload (task set), R the resources available and A the scheduling algorithm that defines how the resources are shared by the workload. Using this nomenclature, two functions were established: (i) the

demand bound function and (ii) supply bound function. The former,  $dbf_A(W,t)$ , quantifies the maximum workload W that can be submitted to resource R under the scheduling policy A during a time interval t. The later,  $sbf_R(t)$ , computes the minimum possible resources that R can provide through a certain time interval t. Resource R satisfies the submitted workload W if:

$$dbf_A(W,t) \le sbf_R(t), \quad \forall t \in \mathbb{R}^+$$

(2.20)

Furthermore, the authors also defined a real-time model,  $\Gamma(\Pi, \Theta)$ , which characterizes the periodic allocation of the resource R by workload W. This periodic model represents a resource supply that provides  $\Theta$  resource units periodically, every  $\Pi$  time units. Consequently, the supply bound function,  $sbf_{\Pi}(t)$ , can be defined as:

$$sbf_{\Pi}(t) = \begin{cases} b\Theta + max\{0, t - a - b\Pi\}, & t \ge \Pi - \Theta \\ 0, & t < \Pi - \Theta \end{cases}$$

(2.21)

where:

$$a = 2(\Pi - \Theta) \wedge b = \left\lfloor \frac{t - (\Pi - \Theta)}{\Pi} \right\rfloor$$

(2.22)

The model proposed by Shin and Lee,  $\Gamma(\Pi, \Theta)$ , was generalized for hierarchical frameworks by Arvind et al. [9] and named Explicit Deadline Periodic (EDP). This model is also characterized by a triplet,  $\Omega = (\Pi, \Theta, \Delta)$ , which represents a resource supply that periodically provides, every  $\Pi$  time units,  $\Theta$  resources units during  $\Delta$  time units, where  $\Delta \leq \Pi$ . Thus, the periodic model  $\Gamma(\Pi, \Theta)$  can be defined as  $(\Pi, \Theta, \Pi)$  using the EDP structure. The supply bound function,  $sbf_{\Omega}(t)$ , is now computed as:

$$sbf_{\Omega}(t) = \begin{cases} b\Theta + max\{0, t - a - b\Pi\}, & t \ge \Delta - \Theta \\ 0, & t < \Delta - \Theta \end{cases}$$

(2.23)

where:

$$a = (\Pi + \Delta - 2\Theta) \wedge b = \left\lfloor \frac{t - (\Delta - \Theta)}{\Pi} \right\rfloor$$

(2.24)

# 2.2 Real Time communications

As previously described, the task's execution on real-time systems is highly conditioned by their temporal constraints. A set of real-time systems interconnected by communication systems (networks) is generally known as *Distributed Real-Time Systems (DRTS)*. Contrarily to standard real-time systems, which only impose time constraints on the tasks execution, DRTS also enforce these restrictions on exchanging messages within the network. Therefore, these systems behavior depends on both timeliness execution of the real-time nodes and communication systems capability of transmitting messages while satisfying timeliness

requirements. Communication systems that can provide such services are known as *real-time* communication systems [10].

Equally to real-time systems, which must properly schedule the task set to satisfy the time requirements, communication networks must also apply scheduling techniques when multiple nodes use a shared medium to exchange messages. Its purpose is to control the access of each device to the network so that the overall system time specifications can be maintained. Similar to task scheduling, techniques used in communication networks can also be classified into: (i) soft, hard and non-real-time, when referring to their time constraints, or (ii) periodic, aperiodic and sporadic, according to their activation. Although this allows the use of scheduling methods applied to tasks, such as scheduling analysis, to be used in the network domain, there are several network-specific issues in distributed real-time systems, such as, e.g., the lack of preemption, that require suitable adaptations.

# 2.2.1 Communication paradigms

To initiate communications, i.e., message exchanging between network nodes, real-time communication systems can use two distinct approaches, *time-triggering* and *event-triggering* [10]:

- Time-Triggered (TT): In systems following the time-trigger paradigm, message transmissions within the network only occurs at specific temporal instants. Those moments are defined in a scheduling table that the network nodes must follow. Therefore, all the nodes must be synchronized and have a common time reference so that the triggering of messages happens at the defined instants. The scheduling table can be built prior to the system activation, i.e., offline, or online, while the system is operating.

- Event-Triggered (ET): Regarding systems that use the event-trigger paradigm, the transmission of application messages is triggered upon the occurrence of an asynchronous event, meaning that they can occur at arbitrary time instants, and cannot be controlled by the network. However, using the minimum inter-arrival time between consecutive events, it is possible to determine the upper bounds for the response time of these systems.

When comparing both paradigms, time-trigger communications are more suitable for synchronized systems, where they can provide low latency and jitter when handling messages. Regarding event-trigger strategies, due to the unpredictability of asynchronous traffic dispatching, these approaches are more fitting to handle sporadic messages with low latency. Nonetheless, upon receiving an overload of asynchronous messages, these procedures may suffer from high jitter and latency. Thus, to solve these issues, systems may ignore less important requests, only executing higher priority tasks, or switch to a time-trigger approach.

Several real-time systems use time and event-trigger approaches when handling both synchronous and asynchronous messages. The main advantages of employing both topologies are

2.3. ETHERNET 19

the increase in flexibility on the overall system and costs reduction. However, the two distinct traffics must be temporally isolated so that the asynchronous nature of event-trigger messages can not interfere with the time-trigger traffic. This can be done by assigning bandwidth restricted sections to different traffic classes.

# 2.3 Ethernet

Ethernet is a communication technology for connecting devices, being the most commonly used to construct Local Area Networks (LAN). It was approved and released by the IEEE as IEEE 802.3 [11] in 1983, with CSMA/CD mechanisms. Carrier-Sense Multiple-Access with Collision Detection (CSMA/CD) is a collision-based protocol where multiple nodes can access the medium (Multiple Access - MA). However, each one must first confirm if the medium is idle before sending data (Carrier Sense - CS). Even with these measures, there still is the possibility that two distinct nodes start their transmissions at the same instant, thus resulting in a collision. This is detected as they keep sensing the medium even after sending the data, which stops the transmission (Collision Detection - CD). Both devices must then wait a random time interval and retry. The process is repeated a maximum number of times or until the transmission process is completed.

# 2.3.1 Ethernet Frame

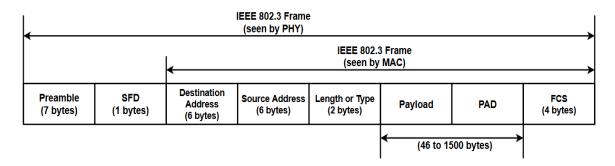

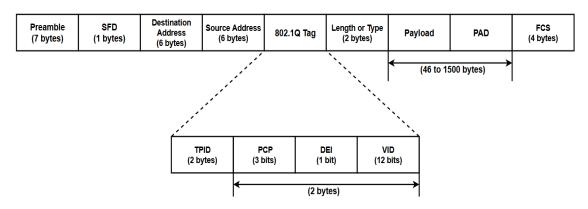

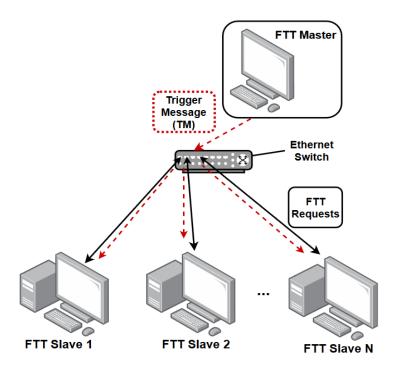

The standard Ethernet IEEE 802.3 data frame is illustrated in Figure 2.2 [11].

Figure 2.2: Standard Ethernet IEEE 802.3 Data frame.

The several fields present on the frame have the following functions:

- *Preamble*: used to establish the synchronization of the receiver devices.

- Start of Frame Delimiter (SFD): sequence of 8 bits with the value "10101011". It indicates the termination of the preamble and the start of the Ethernet frame.

- Destination and Source Media Access Control (MAC) Addresses: used to identify the destination and source network interfaces, respectively.

- Length or Type: value between 0 to  $2^{16} 1$  that indicates the length of the payload or the protocol encapsulated in the data payload (e.g., 0x800 for IPv4 datagrams, 0x86DD for IPv6 datagrams).

- *Payload*: field that contains the data to be sent/received. It can range from 46 to 1500 bytes.

- **PAD**: field used for padding, whenever the minimum imposed size of 64 bytes for the frame is not reached.

- Frame Check Sequence (FCS): value generated by the transmission device, used for error detection by other nodes upon receiving the MAC frame.

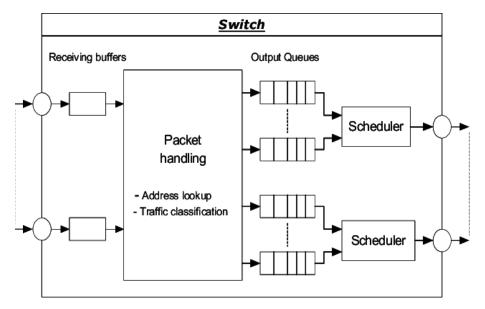

#### 2.3.2 Ethernet Switch

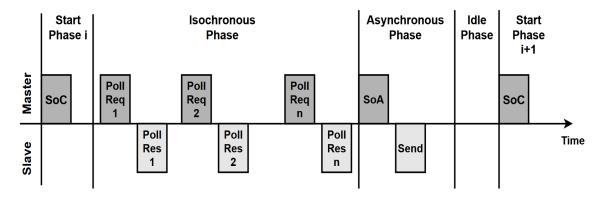

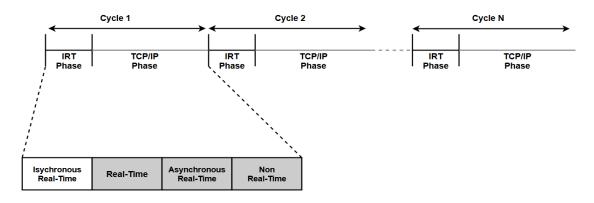

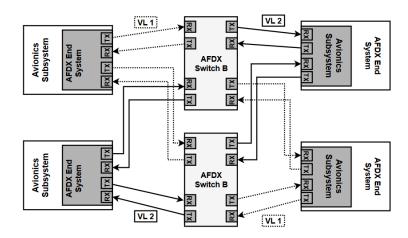

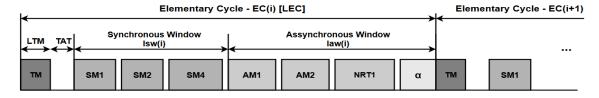

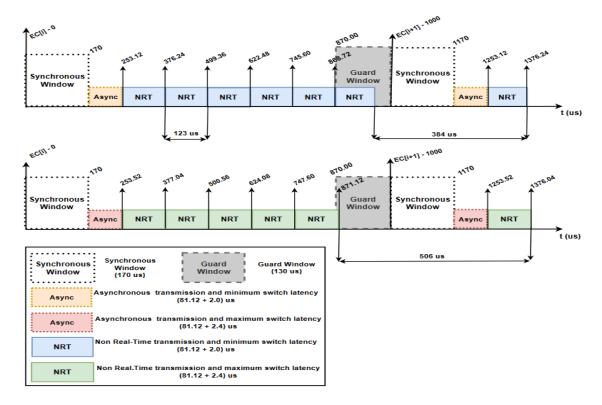

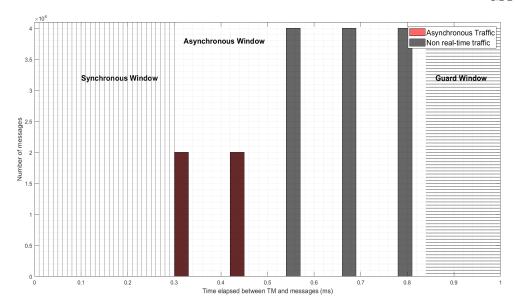

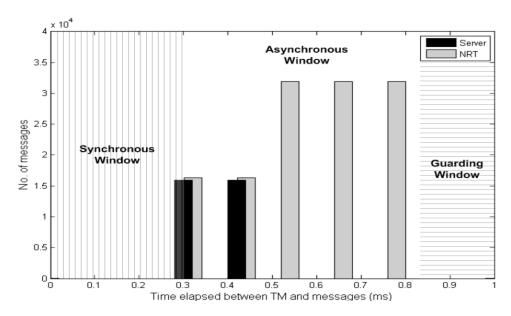

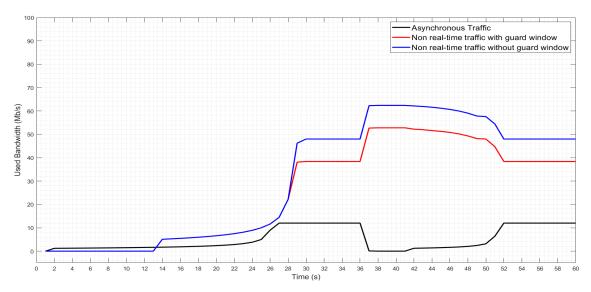

Ethernet switches emerged in 1990 as a mean to overcome the existing issues in Ethernet networks, specifically the lack of non-determinism from the CSMA/CD arbitrary methods, misusage of the accessible bandwidth, and absence of traffic isolation. A switch or bridge is an interconnection device that operates at the data link layer of the Open Systems Interconnection (OSI) reference model (second layer). Contrarily to Ethernet hubs, these devices have mechanisms that reduce the bandwidth wastage which result from broadcasting receiving frames to unnecessary network nodes. Instead, the switch forwards the data only through specific destination ports, thus increasing the overall throughput.