Departamento de Universidade de Aveiro Electrónica, Telecomunicações e Informática, 2014

João Carlos Cordeiro Pires Portar o GNU linker para o EVP DSP Porting of GNU linker for the EVP DSP

João Carlos Cordeiro Pires

## Portar o GNU linker para o EVP DSP Porting of GNU linker for the EVP DSP

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia de Computadores e Telemática, realizada sob a orientação científica do Doutor Paulo Bacelar Reis Pedreiras, Professor do Departamento de Electónica, Telecomunicações e Informática da Universidade de Aveiro e do Doutor Orlando Miguel Pires dos Reis Moreira, Ericsson, Holanda.

### o júri / the jury

| presidente / president       | <b>José Nuno Panelas Nunes Lau</b><br>Professor Auxiliar da Universidade de Aveiro (por delegação da Reitora da<br>Universidade de Aveiro) |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| vogais / examiners committee | <b>Joaquim José de Castro Ferreira</b><br>Professor Adjunto da Universidade de Aveiro                                                      |

|                              | <b>Orlando Miguel Pires dos Reis Moreira</b><br>Principal Dsp Systems Engineer, Ericsson (co-orientador)                                   |

#### Agradecimentos Acknowledgements

I would like to use this space to thanks all the people that help me during the last few years. I probably will forget some of you, but things happen.

First of all I want to thanks to Orlando Moreira and Dmitry Cheresiz for giving me the opportunity to do my master thesis with them at Ericsson. Also I have to thanks to Paulo Pedreiras for being my advisor, even though my work was done far away.

I want to thank to all the people that work at Ericsson for all their help. Specially to Cupertino Miranda, for all his help and all the knowledge that he shared with me.

To my friends, thank you all. Thanks for all the good times that we have spend together, and thanks for put up with me in my worst times.

E como é obvio um grande obrigado para a minha família, que sempre me apoiou e sempre esteve disponível nos bons e maus momentos.

#### Abstract

Nowadays, with the ubiquitous presence of mobile devices, modems play a relevant role. The EVP is a vector processor used by Ericsson on its 2G, 3G and 4G modems. Due to size, weight and power constraints, mobile devices have limited power sources, and because of that the hardware must be power efficient. The processors used in this type of devices have multiple power consumption states. If a processor is in a idle state i.e. without code to execute, it can switch off and consume less power. Moreover, if it is known beforehand that the processing takes less time than available, the processor can be set to a lower frequency (and lower voltage level), executing the same amount of work, but consuming considerable less energy. With this dynamic power consumption the autonomy of the devices is extended, because the processor can be in a reduced power consumption state most of the time.

One way to maximize the time during which the processor stays in a reduced power consumption state is through the execution of optimized code. This can be achieved through manual code optimization, or by letting the compiler apply optimizations on the code. Link Time Optimization (LTO) is a compilation technique that tries to expand the optimizations scope by joining the input files and compile them as a unique file. Using this technique the compiler has more information during the optimization phase and should be able to do better decisions about the optimizations to apply.

The team responsible for the development of Embedded Vector Processor (EVP) wanted to evaluate the benefits of LTO. To be able to implement and evaluate LTO it was necessary to migrate the GNU linker to support EVP and enable LTO compilation on the EVP backend of GNU Compiler Collection (GCC).

This dissertation reports this work, including the necessary concepts to understand the problem addressed, how was added EVP support in the GNU linker, and the necessary step to enable LTO compilation on GCC. Also it will be presented and analysed the performance improvements of using LTO.

The LTO compilation presents mixed results, some of the test cases have a small performance improvements, and other present a small performance degradation. This was kind os expected because of the organization of the test code. It is composed by several files that do not have dependencies between them, in this situation the LTO compilation do not present much benefits.

#### Resumo

Hoje em dia, com a ubiquidade dos dispositivos móveis, os modems desempenham um papel relevante. O EVP é um processador vectorial usado pela Ericsson nos seus modems 2G, 3G e 4G. Devido às condicionantes ao nível de tamanho, peso e energia, os dispositivos moveis tem fontes de energia limitadas, e por isso o hardware tem de ser energéticamente eficiente. Os processadores usados neste tipo de dispositivos, tem múltiplos estados de consumo. Se um processador estiver inactivo i.e. sem ter código a ser executado, o processador pode ser desligado passando a consumir menor energia. Mais ainda se for conhecido de antemão que o processamento demora menos tempo que o disponível, o processador pode reduzir a sua freguência(e a sua tensão), realizando a mesma quantidade de trabalho mas consumindo considerávelmente menos energia. Com o consumo energético dinâmico, a autonomia dos dispositivos é estendida, porque o processador pode estar grande parte do tempo num estado de baixo consumo energético.

Uma maneira de maximizar o tempo que o processador está num estado de baixo consumo energético é através do uso de código optimizado. Este pode ser obtido através de optimização manual, ou deixando o compilador aplicar as otimizações. LTO é uma técnica de compilação que tenta expandir o âmbito das optimizações através da junção dos ficheiros de entrada e compila-los como um só. O uso desta técnica permite que o compilador tenha mais informação durante a fase de optimizações a aplicar.

A equipa responsável pelo desenvolvimento do EVP queria avaliar os benefícios do LTO. Para implementar e avaliar o LTO era preciso adicionar suporte para o EVP ao GNU linker e activar o LTO no GCC especifico para o EVP.

Esta dissertação reporta o trabalho realizado, incluindo os conceitos necessários para perceber o problema, como foi adicionado o suporte para o EVP no GNU linker e os passos necessários para activar a compilação LTO no GCC. Vão ser também apresentadas e analisadas as alterações de desempenho quando o LTO é usado.

A compilao LTO apresenta resultado ambíguos, em alguns dos casos de teste houve pequenos aumentos de desempenho e noutros casos pequenas diminuições de desempenho. Estes resultados eram mais ou menos esperados, devido a organizao do código de teste. Este é composto por diversos ficheiros que não tem dependências entre si, nestas situações a compilação LTO não traz praticamente nenhuns benefícios.

## Contents

| С                         | Contents i        |               |                                                                                           |              |  |

|---------------------------|-------------------|---------------|-------------------------------------------------------------------------------------------|--------------|--|

| $\mathbf{L}_{\mathbf{i}}$ | List of Figures v |               |                                                                                           |              |  |

| $\mathbf{L}^{\mathrm{i}}$ | ist of            | <b>Tables</b> | 5                                                                                         | vii          |  |

| A                         | Acronyms ix       |               |                                                                                           |              |  |

| 1                         | 1 Introduction    |               |                                                                                           |              |  |

| <b>2</b>                  |                   |               | al Introduction.                                                                          | 3            |  |

|                           | 2.1               |               | source code to executable. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |              |  |

|                           |                   | 2.1.1         | Compilation phase                                                                         |              |  |

|                           |                   |               | Lexical Analysis                                                                          |              |  |

|                           |                   |               | Syntax Analysis                                                                           |              |  |

|                           |                   |               | Semantic Analysis                                                                         |              |  |

|                           |                   |               | Code Optimization                                                                         | . 6<br>. 7   |  |

|                           |                   | 010           | Code Generation                                                                           | -            |  |

|                           |                   | 2.1.2         | Assembler                                                                                 |              |  |

|                           |                   |               | Assembly language                                                                         |              |  |

|                           |                   | 010           |                                                                                           |              |  |

|                           |                   | 2.1.3         | Linker                                                                                    |              |  |

|                           |                   |               |                                                                                           |              |  |

|                           |                   |               | Linker Scripts                                                                            |              |  |

|                           |                   | 2.1.4         | Overlays                                                                                  |              |  |

|                           |                   | 2.1.4         | Link Time Optimization                                                                    |              |  |

|                           |                   |               | First Compilation                                                                         |              |  |

|                           |                   |               | Second Compilation                                                                        |              |  |

|                           |                   |               | Linker plugin                                                                             | . 13<br>. 13 |  |

|                           |                   |               |                                                                                           |              |  |

|                           |                   |               | Inlining                                                                                  |              |  |

|                           | 2.2               | Object        |                                                                                           | 14. 14       |  |

|                           | Z.Z               | Object        | t files                                                                                   | . 19         |  |

|          |      | 2.2.1 ELF Files                                                                                        | 15              |

|----------|------|--------------------------------------------------------------------------------------------------------|-----------------|

|          | 2.3  | Binutils                                                                                               | 16              |

|          |      | 2.3.1 Binary File Descriptor                                                                           | 17              |

|          |      | 2.3.2 ld                                                                                               | 17              |

|          |      | 2.3.3 gas                                                                                              | 17              |

|          |      | $2.3.4$ gold $\ldots$ | 17              |

|          |      | $2.3.5$ Other tools $\ldots$                                                                           | 17              |

|          | 2.4  | Debug information                                                                                      | 17              |

|          |      | 2.4.1 DWARF                                                                                            | 18              |

|          | 2.5  | EVP                                                                                                    | 18              |

|          | 2.0  | 2.5.1 Architecture                                                                                     | 18              |

|          |      | 2.5.2 Exposed pipeline                                                                                 | 19              |

|          |      | 2.5.3 Very Large Instruction Word (VLIW)                                                               | 20              |

|          |      | 2.5.5     Very Large instruction word (VERW)                                                           | 20<br>21        |

|          |      | 2.9.4 Intrinsics                                                                                       | 41              |

| 3        | Pro  | olem Description and Approach                                                                          | 23              |

| -        | 3.1  | Problem description                                                                                    | 23              |

|          | 0.1  | 3.1.1 Replace the linker                                                                               | $\frac{-3}{23}$ |

|          |      | 3.1.2 LTO compilation                                                                                  | $\frac{-3}{23}$ |

|          | 3.2  | Approach                                                                                               | 24              |

|          | 0.2  | 3.2.1 Linker                                                                                           | 24              |

|          |      | 3.2.2 LTO enabling                                                                                     | 24              |

|          |      | 3.2.3 Performance Measures                                                                             | 24              |

|          |      |                                                                                                        | - 1             |

| <b>4</b> | Imp  | ementation                                                                                             | 25              |

|          | 4.1  | Creation of a libbfd backend                                                                           | 25              |

|          |      | 4.1.1 Architecture description                                                                         | 25              |

|          |      | 4.1.2 Relocations                                                                                      | 26              |

|          |      | 4.1.3 How a relocation is calculated                                                                   | 28              |

|          |      | 4.1.4 File Operations                                                                                  | 30              |

|          |      | 4.1.5 Debug Sections                                                                                   | 32              |

|          |      | .debug_info_groups                                                                                     | 32              |

|          | 4.2  | Changes in ld                                                                                          | 34              |

|          |      | 4.2.1 New command option                                                                               | 34              |

|          |      | 4.2.2 Version Verification                                                                             | 35              |

|          | 4.3  | Small changes in Binutils package                                                                      | 35              |

|          | 4.4  | LTO enablement in gcc                                                                                  | 35              |

|          | 1.1  |                                                                                                        | 00              |

| <b>5</b> | Disc | ussion of results.                                                                                     | 37              |

|          | 5.1  | Linker Validation                                                                                      | 37              |

|          | 5.2  | How the data was collected                                                                             | 37              |

|          |      | 5.2.1 BLISS test                                                                                       | 37              |

|          | 5.3  | Linker performance changes                                                                             | 38              |

|          | -    | · · · · · · · · · · · · · · · · · · ·                                                                  | -               |

|    | 5.4 LTO performance            | 38              |

|----|--------------------------------|-----------------|

| 6  | Conclusions<br>6.1 Future Work | <b>43</b><br>43 |

| Bi | ibliography                    | 45              |

# List of Figures

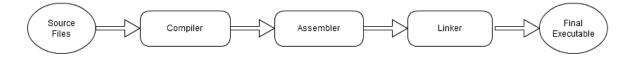

| 2.1 | Passes from source code to executable          | 5  |

|-----|------------------------------------------------|----|

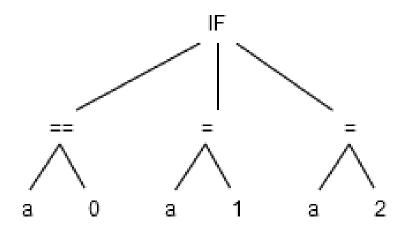

| 2.2 | Abstract Syntax Tree (AST) example.            | 6  |

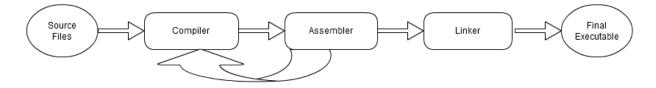

| 2.3 | Passes from source code to executable in LTO 1 | 2  |

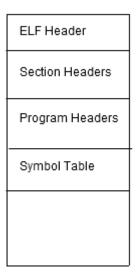

| 2.4 | ELF file Structure                             | 6  |

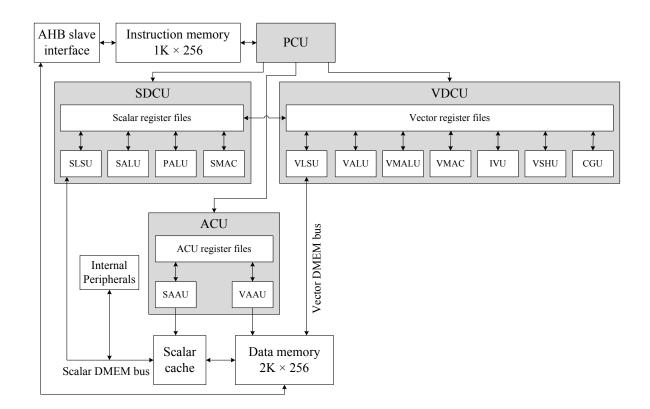

| 2.5 | EVP core block diagram. $[1]$                  | 9  |

| 4.1 | Architecture of the libbfd backend.            | 31 |

## List of Tables

| 5.1 | Size for WCDMA executables    | 38 |

|-----|-------------------------------|----|

| 5.2 | Size for WCDMA executables    | 39 |

| 5.3 | Cycles for WCDMA executables. | 39 |

## Acronyms

| GNU  | GNU's Not Unix                   |  |  |  |

|------|----------------------------------|--|--|--|

| ISA  | Instruction Set Architecture     |  |  |  |

| ELF  | Executable and Linkable Format   |  |  |  |

| LSB  | Least Significant Bit            |  |  |  |

| MSB  | Most Significant Bit             |  |  |  |

| LTO  | Link Time Optimization           |  |  |  |

| IPO  | InterProcedural Optimization     |  |  |  |

| BFD  | Binary File Descriptor           |  |  |  |

| COFF | Common Object File Format        |  |  |  |

| EVP  | Embedded Vector Processor        |  |  |  |

| VLIW | Very Large Instruction Word      |  |  |  |

| PCU  | Program Control Unit             |  |  |  |

| SDCU | The Scalar Data Computation Unit |  |  |  |

| SALU | Scalar Arithmetic Logic Unit     |  |  |  |

| PALU | Predicate Arithmetic Logic Unit  |  |  |  |

| SMAC | Scalar Multiply/Accumulate       |  |  |  |

| SLSU | Scalar Load/Store Unit           |  |  |  |

| VDCU | Vector Data Computation Unit     |  |  |  |

| VALU | Vector Arithmetic Logic Unit     |  |  |  |

| VMALU                                    | Vector Mask Arithmetic Logic Unit |  |  |

|------------------------------------------|-----------------------------------|--|--|

| VMAC                                     | Vector Multiply/Accumulate Unit   |  |  |

| IVU                                      | Intra Vector Unit                 |  |  |

| VSHU                                     | Vector Shuffle Unit               |  |  |

| VLSU                                     | Vector Load/Store Unit            |  |  |

| ACU                                      | Address Calculation Unit          |  |  |

| DSP                                      | Digital Signal Processor          |  |  |

| AST                                      | Abstract Syntax Tree              |  |  |

| CFG                                      | Context Free Grammar              |  |  |

| DIE                                      | Debugging Information Entry       |  |  |

| GCC                                      | GNU Compiler Collection           |  |  |

| WCDMA Wideband Code Division M<br>Access |                                   |  |  |

| SoCs                                     | Systems on Chip                   |  |  |

| ILP                                      | Instruction-Level parallelism     |  |  |

| SDK                                      | Software Development Kit          |  |  |

| ALU                                      | Arithmetic Logic Unit             |  |  |

| SLU                                      | Store Load Unit                   |  |  |

# Chapter 1 Introduction

In the modern world with the massification of mobile/embedded devices, their limitations in memory space, processing power and limited power source became more problematic. The creators of these type of devices are always trying to improve the autonomy without sacrificing its functionalities. The trend at the moment (at least in the smartphones) is to increase the number of functionalities in every iteration and continue to increase autonomy. There are three main areas that could bring autonomy improvements.

- battery capacity: if the battery can hold more power, the device autonomy will be higher.

- **improve hardware power consumption:** if the hardware is more power efficient, the power consumption will be smaller and therefore the autonomy is increased.

- **software performance:** if a task takes less time to complete, the hardware can return to a power save state sooner.

The first two improvements are only applicable for new devices, because they are only available in new hardware revisions.

But for existing models it is not so easy to take advantage from battery improvements and practically impossible to use new hardware. However, software improvements can always be applied to devices by means of firmware updates.

Let us focus on the software performance option. In this option the idea is to reduce the execution time of the tasks. This can be achieved in various ways:

- use specialized hardware: it is common in embedded devices to find Systems on Chip (SoCs) that contain a general purpose processor and a few specialized coprocessors. A vector processor is an example of one such specialized coprocessor. It allows, for instance, adding two vector registers in one single instruction. A vector register is a wider register that contain multiple elements. For instance, in the Embedded Vector Processor (EVP) the vector register is 256 bits wide and can store 16 elements of 16 bits. On a regular processor it would take various instructions.

- manually replace inefficient algorithms: it is common to have algorithms that implement the same functionality but have different execution times. Replacing one for the other will bring a performance improvement maintaining the same functionalities. However this replacement is done by a programmer and can be expensive the search for a better algorithm.

- use automatic optimization tools: apply transformations on the program reducing the execution time. These techniques always result in a longer compilation time. In this situation the optimizations are done by automatic tools, from the programmer perspective there are no cost associated with it, but it is necessary to buy, or develop the optimization tools.

The third option is the more interesting one, mainly because it doesn't require additional work. It is only necessary to inform the compiler about the optimization that should be applied and let it do the work. It can be though as a "free" performance improvement from the application developer point of view.

The type and number of optimizations present in a compiler is dependent of its version and usually recent versions have more and better optimizations. For instance, on version 4.5.0, GNU Compiler Collection (GCC) introduced the ability to do Link Time Optimization (LTO). LTO allows the compilation of multiple source files as if it was a single one. The fact that the compiler operates on a single file instead of multiple files has huge benefits when applying optimizations, because it expands the scope where the optimizations are applied. This will be discussed in more depth on subsection 2.1.4.

The EVP is developed by Ericsson, and is used within the development of thin modems, operating on 2G, 3G and 4G telecommunication networks. These modems will be used in embedded devices and therefore must comply with the design constrains of embedded devices, e.g. limited power. The Software Development Kit (SDK) team, responsible for the development of the compiler, linker, assembler and simulator, is searching for ways to improve the performance of the compiled code. To pursue this path the team migrated the old compiler to the GCC compiler. The migration brought some new optimization techniques, one of these techniques being LTO. When the compilation is done with LTO and the linker has some special support, this compilation brings more improvements that when only the compiler is used.

The current linker is a custom tool created more that 10 years ago. The tool was also created with another processor in mind and some characteristics of the processor are reflected in the linker design choices. For instance, the way the linker deals with memory pages, even though EVP does not have paged memory. More important the linker does not have support for LTO compilation. This support in the linker is important to obtain the best optimization possible. So two approaches appear: add LTO support to the current linker or port a linker with LTO support to EVP.

The decision was to port the linker present in the binutils package. The binutils is a software package develop by GNU's Not Unix (GNU) project, and it contains tools to handle binary files. It contains a linker, an assembler, and tools to inspect binary files.

It is expected that when the work is complete to have a linker that is able to replace the current one, test the LTO compilation and have some data regarding the performance changes that LTO brings.

Through the duration of this work, the GNU linker 1d was ported to support EVP, the LTO support was enabled on GCC and check the performance improvements of LTO compilation.

The document is organized in 6 chapters, the first one explains the reasons behind the work, the second gives the reader the necessary detail to understand the follow chapters, the third one explains in a more detailed way the problem addressed in this dissertation, the fourth chapter explains how the work was done, the fifth presents the analysis of the LTO performance improvements and in the last one the conclusions and future work are presented.

# Chapter 2 Theoretical Introduction.

In the early days of computers, programming a computer involved physically modifying the memory bits. To remove the need to manually change the bits, the programs began to be introduced in the machine via a keyboard. But programs were still written in machine code i.e. in its binary format. The programmer continued to change the memory but now it was not necessary to physical change it. The programmer would write the program first in a piece of paper and then type it into the machine. Both write the program and type it was a tedious and error prone task. But specially the typing part, because the computers did not have a display so it was impossible to catch typing errors until the program was executed. The example on Listing 2.1 is the MIPS machine representation of the code present on Listing 2.2, to make the representation shorter the vales are represented in hexadecimal instead of binary. In this example two values are loaded and then summed.

1 0x20010001 2 0x20020002

3 0x00221820

Listing 2.1: Example of a program in machine code.

To raise the abstraction level the assemblers were created. The assembler abstracts the computer. For instance, it is no longer necessary to know the binary representation of the instructions because the assembler translates the program written in assembly language into machine code. The assembly language is a low-level programming language that has a strong tie to hardware and it uses mnemonics, to identify the instructions. An example of a program in assembly language can be seen in Listing 2.2, this assembly code is equivalent to the C code present in Listing 2.3

```

1 addi $at, $zero, 1

2 addi $v0, $zero, 2

3 add $v1, $at, $v0

```

Listing 2.2: Example of a program in assembly code.

Further down the line, the abstraction level was raised once again. This time from assembly language to high level programming languages. These programming languages introduce a new layer of abstraction from the computer. One of the features introduced by high level languages is the concept of variable. A variable is an abstraction used to represent something in memory. It has a name and a type, both giving it semantic value. But perhaps more important allows the program to be independent of the memory layout. For instance it is easier to deal with a variable named **age** and let the compiler deal with its memory position. In Listing 2.3 is an example of a program written in C language.

```

1 int a = 1;

2 int b = 2;

3 int c = a + b;

```

Listing 2.3: Example of a program in C language.

### 2.1 From source code to executable.

For most programmers compiling a program to an executable is simple and straightforward. It is only necessary to click in a button or execute a single command in a command line. In reality, there are a few steps between a source file and an executable. These steps are hidden from most people for the sake of simplicity.

The steps necessary to create an executable from some source code are depicted in Figure 2.1. I will explain them one by one in the following sections.

#### 2.1.1 Compilation phase

As can be seen in Figure 2.1 the compilation is the first step to create an executable. In this step a compiler is used to translate code between two languages, the original files, usually written in a high level language, and the final files in assembly.

The structure of compiler evolved with time. In the beginning the compiler was a single program written in a monolithic way. With the increasing complexity of programming languages the compiler structure started to split to make development easier and faster, since each of the parts could be developed by different teams. Moreover this separation allowed modular testing. The most common division at this moment is:

- the front-end: is responsible for language analysis and translation of the source code into an intermediate representation.

- the middle-end: works on the intermediate representation and makes generic code optimizations.

- **the back-end:** translate the intermediate representation to machine code and applies optimizations that are specific to that machine.

Each of these different parts of the compiler are also divided in different phases. Each of these phases is independent of the others and each of them transforms the input and feeds it to the next phase.[2] These are the different phases:

- lexical analysis

- syntax analysis

- semantic analysis

- code optimization

- code generation

#### Lexical Analysis

Lexer is the name given to the program/function used in this phase. The purpose of the lexer is create tokens from a sequence of characters. A token is a sequence of characters that has meaning as a whole. The lexer will receive as input the content, of a source file, parse the input file, and outputs a list of pairs, token and token class.

If we think about almost all programming languages we can identify a few token classes that exist in the language. For instance, in the C language we typically have classes such as:

Figure 2.1: Passes from source code to executable

- keywords: words that are reserved for use by language constructs, e.g for, if

- operators: symbols that represent an operation. e.g +, =

- identifiers: usually a string of letter and number that starts with a letter. e.g. foo.

- numbers: a string compose only of digits. e.g 42.

- whitespace: a sequence of spaces, tabs and newlines.

The lexer will go trough all the characters in the input file and tries to find the correspondent class. When this correspondence is met a pair of class and the sub-string is created and added to a list of tokens. Because of the simple nature of this step there are not many errors that can be caught here. They are basically malformed tokens i.e sub-strings that don't fit in any of the token classes.

An example of an input source and the corresponding lexer can be seen at Listings 2.4 and 2.5 respectively. On Listing 2.4 a token is something that is delimited by spaces. An example of a token is the keyword if. On Listing 2.5 we have a list of pairs. A pair is composed by a token and its class identifier. The list is built with all tokens present in Listing 2.4 and their correspondent classes.

1 if a == 0 2 a = 1 ; 3 else 4 a = 2 ;

Listing 2.4: Input of lexical step

```

1 <"if", keyword>, <"a", identifier>, <"==", operator>, <"0", number>, <"a"

, identifier>, <"=", operator>, <"1", number>, <"else", keyword>, <"a

", identifier>, <"=", operator>, <"2", number>

```

Listing 2.5: Output of lexical step

#### Syntax Analysis

This phase receives as an input a list composed by pairs token and token class, and outputs an Abstract Syntax Tree (AST). Parser is the name given to a function that creates an AST using a list of tokens, and grammar rules.

An AST is a data structure used to represent the structure of a program. An AST does not contain certain elements present in the source code because they are intrinsic to this structure. For instance, the parenthesis used in mathematical expressions to show the priority of the operands. In a AST the tree structure represents the order by which the expressions will be evaluated. Another important thing is the capability to add information to a node in an AST that will not change the execution result. This is important to store debug information.

A Context Free Grammar (CFG) is a grammar form used to represent a programming language. The reasons behind the use of CFG are: it is a simple representation, allowing an easy and efficient parsing.

Figure 2.2: AST example.

During the construction of the AST all input tokens must be used. Because all tokens must match a rule in the CFG it is possible to catch all the situations where the input differs from the grammar rules. There are however some languages were the parser grammar is more abstract and the parser allows syntactical valid expressions that are not valid in the language. This is done to make the grammar simpler and these errors should be caught during semantic analysis.

On Figure 2.2 is an example of an AST that can be created from the code on Listing 2.4.

#### Semantic Analysis

The semantic analysis receives an AST and outputs an AST with more information.

During this phase the AST is enhanced with more information about the program. With this new information invalid constructs that escaped the syntax analysis are caught. For example the type checking and verify if all the variables exist and are initialized before use are done in this phase.

#### Code Optimization

The code optimization phase is usually the largest part of a compiler. It is composed by smaller parts and each of these parts does a specific type of optimization. Also it is the only phase that has not a well defined scope. This is a consequence of the fact that each optimization pass being independent from each other. Moreover which passes and the number of times that each pass will be executed is usually user-defined.

There are many optimizations that can be performed in this phase. To mention only a few:

- dead code elimination: in this pass, code that will never be executed is removed; this pass is discussed in more depth in section 2.1.4.

- **constant propagation:** there are situations where a variable is used to store a constant value. This is done because a variable has a name that gives it semantic value. Since it is a constant value the compiler could replace the variable for its value on all occurrences. Another thing done in this pass is the calculation of runtime constant expressions. An example of this can be seen in Listing 2.6.

- **loop transformations:** these are optimizations that operate on loops. Some examples, of optimizations that fit in this category.

- loop invariant code: in some situations some code inside a loop does not change its result between iterations. This code could be removed from inside the loop and the final result of the execution will be the same. See Listing 2.11 for an example.

- loop unrolling. In some situations exists the possibility that the code to manage the loop (variable incrementation, check for loop end) could be bigger than the code inside the loop. One way to reduce the loop overhead is to duplicate the code inside the loop and by this reduce the number of iterations needed in the original loop. See Listing 2.10 for an example.

#### **Code Generation**

This is the last step in a compiler. The compiler will use a description of the target to transform the AST in assembly code. During the creation of the assembly code the compiler has to schedule the instructions in the correct order. It also has to define what variables will be stored in memory and what will be stored in registers.

It is also in this step that the debug information is derived from the extra information added to the AST.

```

1

double CirclePerimeter(Double

1

double CirclePerimeter(Double

radius)

radius)

2

2

{

{

3

3

double pi = 3.1415; // Unused

double pi = 3.1415; //

constante value

value, can be removed.

4

double perimeter = 2 * pi *

4

double perimeter = 6.283 *

radius;

radius; // The two constant

5

return perimeter;

values are multiplied

6

}

during the compilation.

5

return perimeter;

Listing 2.6: Before constant propagation. 6

}

```

1

$\mathbf{2}$

3

4

5 {

6

7 8 Listing 2.7: After constant propagation.

int a, b, c;

for(i = 0; i < 10; i++)

c = 0;

c +=i;

}

b = 10;

```

1

int a, b, c;

2

c = 0;

3

b = 10;

4

for(i = 0; i < 10; i++)

5

{

6

С

+=i;

7

= b; // This line do always

the same independent of the

loop.

8

}

```

Listing 2.8: Before loop invariant extraction.

Listing 2.9: After loop invariant extraction.

a = b; // So it can be removed

from inside the loop.

```

1

int c;

1

int c;

2

2

3

for(i = 0; i < 10; i++)

3

i < 10; i+=2) // The

for (i = 0;

4

ſ

number of

iterations is

5

= c +

reduced to half.

С

i:

{

6

}

4

5

с

с

+

i:

=

Listing 2.10: Before loop unroll.

6

с

=

с

+ i + 1; // Duplicate

the instructions inside

the

loop, to keep the same

behavior.

7

}

Listing 2.11: After loop unroll.

```

#### 2.1.2 Assembler

Just like the compiler, the assembler is also a translator, in this case not between two different languages but between two representations of the same language. Receives as the input the assembly code in a textual representation and outputs the same assembly code, this time in a binary representation.

#### Assembly language

The assembly language is a low level programming language that usually has a one to one relationship to each instruction in the Instruction Set Architecture (ISA) of the processor.

The basic block of the assembly language is the mnemonic that represents an operation and its parameters. The mnemonic tries to be related with the name of the operation. The number of parameters also depends on the type of operation. An example is shown on Listing 2.12. The mov instruction is used to move data from one place to another. So it must have two operands, the origin and destination. The add instruction adds two values and stores the result in a register. So it must have three operands, the two values to sum and the destination.

Some of the benefits of using assembly language instead of machine code are:

- use of symbolic names: in machine code all locations are described by a number, usually a memory address, but it could also be an offset that should be applied to the address of the current instruction. The use of symbolic names allows for more readable code and leaves the address resolution to the assembler. An example can be seen on Listings 2.13 and 2.14. On Listing 2.14 the instruction present on address 0x42 is associated with the loop label. When is necessary to reference this instruction the label can be used instead of its address. This allows the instructions to move freely across the code without the need to correct the addresses.

- less machine dependant code: if two processors implement the exact same ISA but the encoding is different, using two assemblers, each specific to each processor, allows the same code to be translated and executed in both processors. The use of symbolic name also helps sharing code between two processor architectures, because it allows memory abstraction.

- usage of higher level constructs: one example is the use of virtual instructions. These instructions are expanded by the assembler into two or more instructions. An example of this can be seen on Listings 2.15 and 2.16. For instance, in the MIPS architecture the instruction la(Load Address) that loads a 32 bits value into a register is translated into a lui(Load Upper Immediate) and a ori(Or Immediate), since the MIPS ISA does not have any instruction that have a 32 bits immediate field.

1 mov r1, r2

2 addi \$2, \$1, 1

#### Listing 2.12: MIPS Mnemonics

| $\frac{1}{2}$ | 0x42 add r1, 3, 2<br>0x44 jump 0x42          | $\frac{1}{2}$ | 0x42 loop: add r1, 3, 2<br>0x44 jump loop       |

|---------------|----------------------------------------------|---------------|-------------------------------------------------|

|               | Listing 2.13: Use raw addresses              |               | Listing 2.14: Label use                         |

| 1             | la r1, 0x42                                  | $\frac{1}{2}$ | lui r1, 0x0<br>ori r1, 0x42                     |

|               | Listing 2.15: Example of virtual instruction | _             | Listing 2.16: Expansion of virtual instruction. |

#### The assembler

The work done by the assembler is to convert a textual representation into binary encoding. It reads an instruction, converts it and repeats untils the end of the file. There is however a complication; the addition of symbolic names creates the need to know the value that each symbol represents. This can be done in a one pass or two pass schemes. [3]

In a one-pass assembler the symbol table is created at the time that the output is generated. This makes the assembler more complex because of the need to deal with symbols that are not yet defined. When the assembler finds a symbol there are three possible situations: the symbol exists in the symbol table and it is already defined, it exists in the symbol table but it is not defined or the symbol does not exist in the symbol table. The first situation is the easiest one, since the assembler only has to replace the symbol by its value and encode the instruction. The second and third cases are similar, the only difference is that the third one has to create a new entry in the symbol table. In these cases the instruction will be encoded with the field where the symbol will be stored set to zero and the assembler must keep track of the position where the undefined symbol appeared. After the end of the file was found the assembler needs to substitute all undefined symbols with the correct values.

In a two-pass assembler the input file is parsed two times, in the first pass the symbol table is created and all the symbols values are calculated. In the second pass, when a symbol is found, its value is retrieved from the symbol table and the instruction in encoded using that value.

#### 2.1.3 Linker

As previously said, for each source file an object file will be generated. Usually the program is composed by more than one file, and at some point it is necessary to join them in order to make the final executable. This is the job of a linker.

When the assembler creates an object file, it sets the beginning of the file at the address zero. When a linker is linking more that one file it will have to adjust the addresses of the object files so that there are no address conflicts.

A linker will receive object files as input, and for each of these files will join the sections according the instructions on the linker script.[4] For more information about linker scripts see section 2.1.3. When the sections are joined their start addresses change to reflect their new positions, and that raises a problem on instructions that are position dependent. A position dependent instruction is an instruction that references explicitly a memory location. When these types of instructions appear is necessary to set the memory location to the correct address. This operation is called a relocation. It is responsibility of the assembler to decide when a relocation is needed, and the linker is responsible to resolve them.

#### Relocations

A relocation is the way the assembler informs the linker about instructions that are position dependent and the linker will need to do some work on them.[4]

A relocation is an indication to an instruction that needs to be changed. A simple example of a relocation is when an instruction references an address inside the same section. When the section start address changes, all instructions inside this section will be shifted by the start address. In this situation the linker goes through all the relocations and adds the initial position of the section to the value in the instructions.

However a program is usually composed by more that one section and tends to have references between sections. In this situation it is necessary more information to resolve the relocation

One example of the information needed to resolve all types of relocation can be seen at Listing 2.17. This example shows the format that Executable and Linkable Format (ELF) files use to store relocations.[5] The ELF format has two ways to represent relocations, the difference between them is in the  $r_addend$  field. The  $r_offset$  gives the location where the relocation must be applied. The  $r_info$  stores two pieces of information. In the 8 Least Significant Bits (LSBs) are stored the type of relocation, the type is specific to each processor, and in the other 24 bits are stored the index in the symbol table of the symbol used to calculate the relocation. The  $r_addend$  is one of the values used to calculate the relocation value. This value can be stored in two places, in the structure, the case of Elf32\_Rela or on the object file in the position where the relocation will be applied.

```

1

typedef struct {

\mathbf{2}

Elf32_Addr r_offset;

3

Elf32_Word r_info;

4

} Elf32_Rel;

5

6

typedef struct {

7

Elf32_Addr r_offset;

Elf32_Word r_info;

8

9

Elf32_Sword r_addend;

10

} Elf32_Rela;

```

#### Listing 2.17: Type of ELF relocations

The way that relocations are calculated has to do with their type and since the type is specific to each processor, the process can be really different between processors. The reasons behind this difference has to do with instruction encoding, and memory addressing modes.

To calculate the value of a relocation two values are needed, the  $r_addend$  and the value of the symbol given by the field  $r_info$ . The address is calculated by summing these two values. The calculation part is pretty much the same for all relocations, the big difference is how the value is stored in the instruction. An example of this difference is shown on Listings 2.18 and 2.19.

```

1 symbolValue = 0x00002014

2 addend = 0x0

3 relocation = 0x00002014 //symbolValue + addend

4 jmp 0x00002014

```

Listing 2.18: EVP relocation example

```

1 symbolValue = 0x00002014

2 addend = 0x0

3 relocation = 0x00002014 //symbolValue + addend

4 relocation = 0x805 //relocation >> 2

5 //relocation also drop the 4 MSB.

6 j 0x805

```

#### Listing 2.19: MIPS relocation example

On Listing 2.18 is shown a relocation where the complete address is stored in the instruction. Now on Listing 2.19 the size of the stored value is 26 bits, the four Most Significant Bit (MSB) are dropped and the value is shifted right two times.

#### Linker Scripts

During the linking process the linker needs to know how to aggregate the different sections, and where each of these aggregations will be loaded into memory. The linker scripts are used to inform the linker on how to organize the executable.

The simple linker script present on Listing 2.20 tells the linker to put all input sections that have a name that ends with .text in an output section with the name .text.[6] The start address of this section will be 0x1000. The other sections(.data, .bss) will have the same behaviour except for the load address, which in the .data section, the load address will be 0x8000 and the .bss section will be loaded at the end of .data section.

```

1 SECTIONS

2 {

3    .text 0x1000 : { *(.text) }

4    .data 0x8000 : { *(.data) }

5    .bss : { *(.bss) }

6 }

```

Listing 2.20: A simple linker script.

The linker scripts are much more powerful. We only saw a simple example that shows how to aggregate sections and define where they should be loaded. A few more things that are possible to do with linker scripts are:

- create new symbols.

- create memory bocks that have a start address, a size and access flags(i.e. read, write, executable).

- create unusual memory layouts, e.g more that one memory space, overlays.

#### **Overlays**

The use of overlays is a method that allows the execution of programs bigger than the physical memory available. This feature was relevant in the beginning of the computer age were the available memory was small, and there was the need to run programs that were bigger than the memory available. Today even if it is not a necessary feature in the computers, continues to be a relevant feature in the embedded world, were the available memory continues to be scarce.[4]

As it can be deduced from its name, overlays refer to some sections of a program that have the same memory address, i.e. that their memory addresses overlap. The linker will create sections that have the same memory address and then in runtime the program load/swap the overlays according to the needed functionalities.

Figure 2.3: Passes from source code to executable in LTO

One way to create a simple overlay is shown on Listing 2.21. If we compare the linker script on Listing 2.20 with the one on Listing 2.21 it is easy to see that the last one has two more section, .ov1 and .ov2. Each of these sections is a overlay. These two section have the same load address, and the code will be prepared to run in that memory location. Also since the sections have the same start address they can not be loaded into memory at the same time.

The example shown in Listing 2.21 is a simple example of overlays from the point of view of the linker. All overlay management must be done by the program which needs to know how the functions are spread across the different overlays, how to load, and when to load them. However there are also implementations that change the burden of managing the overlays from the programmer to the linker.

```

SECTIONS

1

\mathbf{2}

{

3

.text 0x1000 : { *(.text)

}

4

.ov1

0x3000

:

{

*(.ov1)

}

5

.ov2

0x3000 :

{ *(.ov2)

}

\mathbf{6}

.data 0x8000 : { *(.data)

}

7

.bss

: { *(.bss)

}

8

}

```

Listing 2.21: A simple overlay linker script.

#### 2.1.4 Link Time Optimization

As it was said before, during the compilation phase each source file is compiled independent of the others. This can be seen as a beneficial thing since the process could be executed in parallel, but also has the problem that no information can be shared between the different compilation processes. Also for various reasons the code tend to be divided in functions and these functions spread across different files, this means that the information about the dependencies of a function may not be present in the optimization phase.

InterProcedural Optimization (IPO) is the name given to optimization techniques that expand the scope of optimizations across functions.[2] When applying IPO the more information about the whole program the compiler has, the better.

LTO is one of the methodologies used to increase the information present in the compiler before applying the IPO.

The compilation flow when LTO is active is shown in Figure 2.3. As it can be seen the files created by the assembler are feed as input to the compiler and the compilation process is repeated. Another difference is in the files generated by the assembler. These files have additional information that is sufficient for the compiler to recreate its internal structures and continue with the compilation process.[7]

#### **First Compilation**

The first compilation is almost identical between a normal compilation and a LTO compilation. The big difference is that when LTO is active the compiler will output the necessary information to latter continue with the compilation process. This information is emitted in special sections on the assembly file and they contain the intermediate representation, a symbol table and all the definitions for the compilation unit, i.e. the input source code. The object files outputted by a LTO compiler will be called "fat" object files. However the "fat" object files have the side effects of doubling the compilation time and increse their sizes.[7]

#### Second Compilation

In the second invocation, the compiler will receive a group of "fat" object files instead of source files. The compiler will read the intermediate representation from each of the files and it reconstructs the compilation unit for each file. After all files are read the compiler will merge all the compilation units into one.

The compiler will then run the optimization phase again. The compilation unit at this moment can be big and that means bigger compilation times. To improve the compilation times the GCC has two ways of running the optimization phase. [7]

- single compilation unit: the compiler works on a single compilation unit. Since it has more information the global optimization can be better, but the compilation time will also increase.

- multiple compilation units: the compiler will create smaller compilation units and apply the optimizations in each of these smaller units. The partition should try to minimize dependencies between the compilation units. Since the compiler has multiple compilation units the optimization process can be run in parallel.

At the end of the optimization phase the compiler will generate assembly files that will be assembled, and linked like in a normal compilation.

#### Linker plugin

This feature allow the exchange of information between the linker and the compiler.

The "fat" object files contain both the assembly code and the information needed to resume the compilation process. These files can be used to build libraries that contain executable code and the information needed in the second pass of a LTO compilation. Let's call these libraries "fat" libraries.

Since a "fat" library contains the information needed on the second compilation, why not use these information when compiling programs that use the library.

This information can be used if the linker has support for it, through the use of the linker plugins. The idea is, after the first compilation the linker will be invoked and it will resolve the external dependencies. The linker will then invoke the second compilation with the object files generated in the first compilation and all information gathered in the linking process. Using this compilation process, the amount of data that is given to the second compilation is bigger and because of that there are more room to optimizations.

#### **IPO Benefits**

IPO is a set of techniques that uses the relationship between caller and callee in order to better optimized them.[2] The main optimization techniques used are:

- constant propation: it was already discussed in section 2.1.1.

- procedure cloning: is used to duplicate functions that one of the parameters is constant. It can be seen at an extreme case of constant propagation. For instance, assume the follow function f(int i), if this function is always called with i equals five, the function can be cloned and create the

function  $f_5()$ . This one does not have parameters, and in all cases where the *i* was used it was replaced by the value five.

- dead code elimination

- function inlining

#### Inlining

The inlining technique is based on the possibility to replace a function call by the function content. This is beneficial because saves the cost of a function call, this is more notorious if the function that was inlined is small, because in this case most of the execution time is spend on the call. However the inlining functionality has the side effect of code size increase. When a function is inlined, the calls to that function are being replaced by its content, that means that the code is duplicated through all the executable. Usually the compiler takes the code increase as a metric to decided if the function should be inlined.

Since the function call will be replaced by the function code, it must be known on the compilation unit where the function is called. For instance if the code on Listing 2.22 is on the same compilation unit the function call of circlePerimeter on line 2 can be replaced by the content of print function, obtaining the code shown on Listing 2.23.

As it was said before for the inlining to work the caller and callee must be on the same compilation unit, which is not always true. The use of LTO has the benefit of join all the compilation units into a single one. Now in this bigger compilation unit the optimization process could do a more aggressive inlining.

Another interesting thing is that the inline optimization can produce dead code. The circlePerimeter function on Listing 2.23 is never executed and it can be safely removed.

| 1 |                                                      | 1                                                   |

|---|------------------------------------------------------|-----------------------------------------------------|

| 2 | double perimeter =                                   | 2 double perimeter = $6.283 *$                      |

|   | <pre>circlePerimeter(radius);</pre>                  | radius;                                             |

| 3 |                                                      | 3                                                   |

| 4 |                                                      | 4                                                   |

| 5 | <pre>double circlePerimeter(double     radius)</pre> | 5 double circlePerimeter(double radius)             |

| 6 | {                                                    | 6 {                                                 |

| 7 | <pre>double perimeter = 6.283 * radius;</pre>        | <pre>7 double perimeter = 6.283 *     radius;</pre> |

| 8 | return perimeter;                                    | <pre>8 return perimeter;</pre>                      |

| 9 | }                                                    | 9 }<br>-                                            |

Listing 2.22: Before inline function.

```

Listing 2.23: After inlined function.

```

#### **Dead Code Elimination**

The dead code elimination is a technique that finds and removes code that will never be executed. This optimization usually has more impact in the code size than in the execution speed.

An example of dead code elimination can be seen at Listing 2.24. In this example if both functions main and deadFunction are in different compilation units, then it is impossible to know the message that will be printed.

However when using LTO the function deadFunction on line 6 will be the target of constant propagation and becomes obvious that the code present on the else block will always be executed, in this situation the line 3. Since the executed code is always the same, the rest of the code can be removed. After removing the unneeded code from the main, it became like the one shown on Listing 2.25.

```

1

int main()

1

int main()

\mathbf{2}

\mathbf{2}

{

{

3

printf("Always executed");

if (deadFunction())

3

}

4

4

{

5

printf("Never executed");

5

}

6

\mathbf{6}

int deadFunction()

7

else

7

{

8

{

8

return 0;

}

9

9

printf("Always executed");

10

}

Listing

2.25:

After

dead

code

11

}

elimination.

12

13

int deadFunction()

14

{

15

return 0;

16

}

```

Listing 2.24: Before dead code elimination.

# 2.2 Object files

An object file is a file that contains code and data generated by the assembler in a binary form.[4] Besides code and data, a list of relocations, a list of symbols and debug information can also be present in an object file. The information present depends upon the purpose of the object file. For instance a final version of a program has no need for debug information.

An object file has a combination of these three functionalities:

- **linkable:** is a file that will be used as input for a linker. Besides code and data this type also has a symbol table and a relocation table.

- **executable:** its purpose is to be loaded into memory and executed. Not that much information is needed in this type of file besides code and data, but the code and data must be arranged in a way that allow execution, i.e. all relocation resolved, code and data starting address must comply with memory constraints.

- **loadable:** it is able to be loaded into memory as a library. Have almost the same configuration as a executable, the big difference is that a loadable file could have some relocation information that will be resolved when is loaded into memory.

## 2.2.1 ELF Files

There are a lot of different types object files. It goes from simple ones that only have data to the more complex ones. The ELF format belongs to the last category. It is a fairly complex format because supports linkable, executable and loadable files. This format was created by AT&T to replace the Common Object File Format (COFF) format as the default object file format in Unix System V.[5]

The ELF format has two different interpretation, one made by the assembler and linker and the other by the loader. On the first interpretation the basic unit is the section. The assembler creates sections based on information given by the compiler, the linker goes through all sections, joins them and creates program headers. A program header is composed by multiple sections and defines the memory layout.

Figure 2.4: ELF file Structure

The other view is the interpretation of the loader, that will look at the program headers and loads them at the correct memory addresses.

A possible structure of an ELF file is show on Figure 2.4. Note that only the ELF header has a fixed position.

- **ELF header:** It is always at the beginning of the file, and contains information about the file. e.g. file type, size, endiness, entry point, the location and size for the other structures.

- section headers: Is an array of section header structures. Each section header describes a section. It contains the name, size, type, flags, location and memory load address of a section.

- **program headers:** An array of program headers. Each program header describes a memory segment. It contains the type, location, flags, and memory load address of a segment.

- symbol table: Contains all the symbols and respective values.

- string table: Contains the strings that are used on the names of sections and symbols. A string is a sequence of null terminated characters.

- **relocations:** A list with the relocations to apply. The format used to store the relocations is shown at Listing 2.17.

# 2.3 Binutils

Binutils is a open source project. Its purpose is to provide free tools to create and manage binary files. The main focus is the development of a linker and an assembler, even tough a few more small tools are present. Other important functionality is the capability to manipulate multiple types of object files, support various processor architectures and support for diverse operating systems.

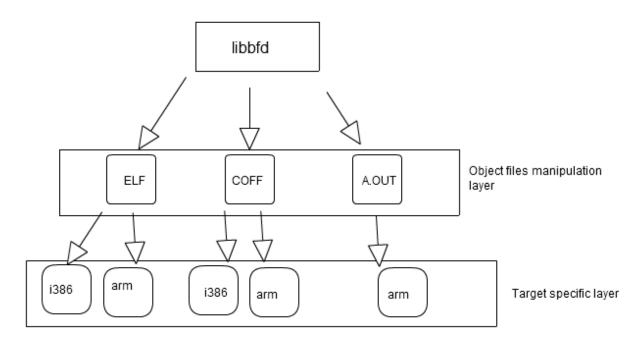

In order to achieve the multiple object files support and multiple processor architectures, all file manipulations are abstracted thought the use of libbfd.

#### 2.3.1 Binary File Descriptor

With the intention to handle multiple object files and support multiple processor architectures, Binary File Descriptor (BFD) was proposed and implemented in the libbfd library. The purpose of libbfd is to handle the myriad of different combinations of object files and processor architectures in a simple and equal way. One of the benefits of this approach is that it makes the addition of a new target simpler, because only the code of libbfd needs to be changed.

libbfd has two different parts, lets call them front-end and back-end. The front-end is the interaction point for the clients. It is composed by functions to manipulate BFD structures. The back-end is specific to each processor architecture and object file type, and it is responsible for the translation between object files and its BFD representation and vice versa.

A simple interaction could be, a client opens a file, the back-end will translate it to a BFD structure, the client manipulate the BFD and in the end writes the result to a file. Once again the back-end will be used to do the translation but this time from BFD to object file. Note that the origin and destination files may have different types.

#### 2.3.2 ld

1d is one of the two linkers available in binutils package. Its purpose is to have a linker that allows the linkage of different object file types on multiple computer architectures.

ld achieves the multiple object files support with the use of libbfd. Using libbfd allows to handle in a uniform way all the different object file types. The linker could receive as input multiple object files in different formats that will be linked together.

#### 2.3.3 gas

gas is the assembler in binutils package. It is an assembler that supports various object file types trough the use of libbfd. Is has support for multiple processor architectures and respective assembly languages.

#### 2.3.4 gold

gold is a linker that only handles ELF files and a few processor architectures. It was created to have better performance that ld, specially when linking C++ code. It is one of the few tools in Binutils package that do not make use of libbfd.

#### 2.3.5 Other tools

Binutils has a few more tools. None of them as big and complex as ld, gas or gold.

- **objdump:** is used to inspect object files. It allows to see the list of section, symbols, relocations and a few more relevant information. Makes use of **libbfd** to read files.

- readelf: has the same functionalities as objdump but only for ELF files. It was created as a way to debug ELF backend of libbfd.

# 2.4 Debug information

Debug information is extra information present in an executable. This information is not necessary for the correct execution of the program, but it is used by a debugger to help debug the program. The use of debug information allows for source-level debugging. As the name implies the source-level debugging allows the debugger to show the original source code, and the debug operations are applied into the original source code instead of assembly code, i.e. allows to step to the next line of code, inspect the value of variables, break the execution when a function or line of code is reached.

# 2.4.1 DWARF

The DWARF format was created to be used by the C compiler and debugger present in the Unix System V Release 4 during the 1980s.[8] The format continue to evolve with time. The more notable changes from the first version are, reduce the generated data, support for new languages, new processors and extend the support for current supported languages.

The information is stored in a tree format, where each node is a Debugging Information Entry (DIE). A DIE is composed by a Tag field that represents the DIE type, and data fields that are specific to the DIE type. The names given to the tags field are prefixed by DW\_TAG and the name of fields are prefixed by DW\_AT. In Listing 2.26 it is shown an example of a DIE. In this case it is shown an example of an integer type with 4 bytes.[8]

```

1 DW_TAG_base_type

2 DW_AT_name = int

3 DW_AT_byte_size = 4

4 DW_AT_encoding = signed

```

Listing 2.26: A DIE that represent and integer type.

# 2.5 EVP

The EVP is a embedded vector Digital Signal Processor (DSP) developed by Ericsson and used in their 2G, 3G and 4G modems.

The following characteristics are used to reduce the complexity of the hardware and make it more power efficient.

- **Exposed pipeline:** this means that the processor does not have hardware to stall, insert bubbles or flush the pipeline. When these capabilities don't exist the compiler becomes responsible for the correct execution of the pipeline. So the compiler must guaranteed that the generated code does not create resource conflicts and the delay slots are properly filled.

- Very Large Instruction Word (VLIW): it is a method that creates bundles of instructions that don't have dependencies between them and therefore can be executed in parallel.

## 2.5.1 Architecture

A block diagram of the architecture of EVP can be seen in Figure 2.5 The more relevant block are:

- Program Control Unit (PCU): handles the instruction decoding, branching and hardware loops.

- The Scalar Data Computation Unit (SDCU): executes the scalar instructions. This block contains two register files, the scalar one with 32 registers that are 16 bits wide and the predicate one with 8 register that are one bit wide. The scalar registers are named from r0 to r31 and each of them can be used as a 16 bits operand. It is also possible to join two register together in order to archive 32 bits operand. In this situation the two register must be contiguous and the lower one must be an even number e.g r2r3. This block also contains a Scalar Arithmetic Logic Unit (SALU), a Predicate Arithmetic Logic Unit (PALU), a Scalar Multiply/Accumulate (SMAC) and a Scalar Load/Store Unit (SLSU).

Figure 2.5: EVP core block diagram.[1]

- Vector Data Computation Unit (VDCU): takes care of vector instructions. In this block are present five register files. The vector register file (vr) has 16 registers 256 bits wide. The register can store 32 elements of 8 bits, 16 elements of 16 bits and 8 elements of 32 bits. Two or three registers can be joined in order to make a 512 bits or 640 bits register which can hold 16 elements of 32 bits or 16 elements of 40 bits. The mask register file (vm) contains 8 elements of 32 bits and is used to make the storage of the calculated values optional. i.e. depending if a bit is one or zero the corresponding vector element will be saved or not. The ir and im register files are used to store the result of inter-vector operations, on vr and vm register respectively. The vsp are used in the operations on Vector Shuffle Unit (VSHU). Other unit present in this block are, Vector Arithmetic Logic Unit (VALU), a Vector Mask Arithmetic Logic Unit (VMALU), a Vector Multiply/Accumulate Unit (VMAC), a Intra Vector Unit (IVU), a VSHU and a VDCU.

- Address Calculation Unit (ACU): performs address calculation using the pointer and offset register that will be used by Vector Load/Store Unit (VLSU) and SLSU.

### 2.5.2 Exposed pipeline

The pipeline technique is used in processors to enhance performance.[9] The idea behind pipeline is that instructions processing can be divided in small steps and these steps can be executed in parallel. This allows that multiple instructions are in execution, each of them will be in a different step and this way increase the throughput. One of the assumptions when writing a program is that when an instruction starts to execute the previous one has already finish its execution. However this is false in a pipelined processor. This is problematic when two instructions that have a data dependency between them are executed, because it could lead to unexpected results. In order to guarantee that the execution result is the same between a pipelined processor and a non pipelined it is necessary to take care of the data dependencies between instructions. For this is necessary to maintain a list of instructions in execution and their dependencies. If at some point one of the instructions does not have a dependency satisfied because another instruction did not finish its execution, that instruction and all that are behind must be stalled until the dependency is satisfied and the execution can continue.

Another situation where the pipeline content must be changed is in the case of branches. When a branch is started to execute the next instruction is not yet known. Now there are two options.

- The next instructions slots are fill with nops (the number depends on how many cycles the branch takes to execute) and after the branch is resolved starts to execute the correct instruction. This is call delay slots.

- Chose one of the two possible instructions. After the branch is resolved if the choice was correct, continue with the processing. Otherwise clean the pipeline and start processing the correct instruction.

A processor is said to have a exposed pipeline when the pipeline control is done by the compiler, i.e. the compiler will schedule the instructions to avoid data dependencies and it must fill the correct number of delay slots. The content of delay slots may be nops or instructions that have to be executed and have no effect in the branch result.

#### 2.5.3 VLIW

Modern processors are composed by multiple functional units. Each of these units implements a set of related operations, e.g. the Arithmetic Logic Unit (ALU) implements the arithmetic and logic operations, and a Store Load Unit (SLU) implements the operations of load and store information on external memory. They also have multiple units that implement the same functionality and can be executed in parallel. With the existence of multiple units, there is the possibility of executing multiple instruction in parallel.