### **Luís Carlos Cótimos Nunes**

Mecanismos de Geração da Distorção Não-Linear em Amplificadores Doherty

Nonlinear Distortion Generation Mechanisms in Doherty Amplifiers

### **Luís Carlos Cótimos Nunes**

### Mecanismos de Geração da Distorção Não-Linear em Amplificadores Doherty

# Nonlinear Distortion Generation Mechanisms in Doherty Amplifiers

Tese apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Doutor em Engenharia Electrotécnica, realizada sob a orientação científica do Doutor Pedro Miguel da Silva Cabral, Professor Auxiliar do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro e sob a coorientação científica do Doutor José Carlos Esteves Duarte Pedro, Professor Catedrático do Departamento de Electrónica, Telecomunicações e Informática da Universidade de Aveiro.

Apoio financeiro da Fundação para a Ciência e a Tecnologia (FCT) no âmbito de uma bolsa de investigação, ref. SFRH/BD/89941/2012, e do projecto EXPL/EEI-TEL/0851/2013. Apoio financeiro da Fundação Luso-Americana para o Desenvolvimento (FLAD) através de uma bolsa à participação de oradores portugueses nos EUA, ref. 2015/CON11/CAN9.

| Dedico este trabalho à minha namorada, aos meus pais e à minha irmã pelo incansável apoio. |

|--------------------------------------------------------------------------------------------|

|                                                                                            |

|                                                                                            |

|                                                                                            |

|                                                                                            |

### O júri / The jury

Presidente / President Doutor Luis Filipe Pinheiro de Castro Professor Catedrático da Universidade de Aveiro

Vogais / Examiners committee Doutor Francesc Purroy Martin

Senior Expert, Huawei Technologies, Sweden AB

Doutor João Manuel Torres Caldinhas Simões Vaz

Professor Auxiliar do Instituto Superior Técnico da Universidade de Lisboa

Doutor José Alberto Peixoto Machado da Silva

Professor Associado da Faculdade de Engenharia da Universidade do Porto

Doutor João Nuno Pimentel da Silva Matos Professor Associado da Universidade de Aveiro

Doutor Pedro Miguel da Silva Cabral

Professor Auxiliar da Universidade de Aveiro (orientador)

# Agradecimentos / Acknowledgments

Em primeiro lugar gostaria de agradecer aos meus pais, por uma vida de esforço e dedicação. À minha irmã pela sua preocupação e amizade. Aos três pelo incansável apoio, encorajamento e exemplo que sempre me proporcionaram em todas as situações da minha vida, tanto profissionais como pessoais. Sem eles nada disto teria sido possível.

Aos meus orientadores Prof. Pedro Miguel Cabral e Prof. José Carlos Pedro por todos os conhecimentos que me transmitiram, pelo apoio, motivação e orientação que sempre me deram. Agradeço também o excelente ambiente de trabalho que me foi proporcionado e o exemplo que me transmitiram, levandome a procurar sempre a excelência.

A todo o grupo de Circuitos e Sistemas de Rádio do Instituto de Telecomunicações de Aveiro, por todas as sugestões, discussões e pelo óptimo ambiente de trabalho durante todo o meu percurso.

À Huawei technologies por me ter proporcionado a oportunidade de trabalhar para um projecto muito desafiante e que muito contribui para melhorar o meu trabalho. Nomeadamente gostaria de agradecer ao Dr. Francesc Purroy, Dr. Oleg Pozdeev and Mr. Zeng Zhixiong por todas as sugestões e discussões que tivemos durante o meu trabalho.

Agradeço também à Universidade de Aveiro, ao Departamento de Electrónica, Telecomunicações e Informática e ao Instituto de Telecomunicações por me terem facultado todos os meios e ambiente de trabalho necessários. Assim como a todos os colaboradores destas instituições que contribuíram para o meu trabalho.

À Fundação para a Ciência e Tecnologia pelo apoio financeiro concedido sob a forma de uma bolsa de Doutoramento.

À Fundação Luso-Americana para o Desenvolvimento (FLAD) por me ter subsidiado uma das viagens aos Estados Unidos para participação num congresso.

Gostaria também de agradecer a amizade de todas as pessoas que me apoiaram e me deram forças para continuar, mostrando-se sempre presentes.

Por fim, não poderia deixar de agradecer à minha namorada pelo seu incondicional apoio, encorajamento e compreensão nos momentos mais difíceis. Sem a sua força tudo teria sido muito mais complicado.

A todos o meu muito Obrigado!

#### palavras-Chave

AM/AM, AM/PM, Amplificadores de Potência, Amplificadores Doherty, Distorção Não-Linear, Eficiência Elevada, Linearidade, Modulação da Carga, Modelação de Dispositivos

#### resumo

Presentemente, os sistemas de comunicações sem fios exigem uma maior mobilidade e elevadas taxas de transferência. Para além disso, a necessidade de eficiência espectral obriga ao uso de esquemas de modulação de envolvente variável. Consequentemente, o desenvolvimento de amplificadores de elevada eficiência, com uma elevada largura de banda e, ao mesmo tempo, lineares, tornou-se num dos maiores desafios para os engenheiros de projeto de amplificadores de potência. Por forma a cumprir estes requisitos muito rigorosos, o amplificador em configuração Doherty parece ser a técnica mais promissora. Contudo, devido à sua complexa operação, os seus mecanismos de geração de distorção não linear não são ainda completamente conhecidos. Atualmente, apenas interpretações heurísticas estão a ser usadas para justificar os fenómenos observados. Nesse sentido, o principal objetivo deste trabalho é desenvolver um modelo capaz de descrever os mecanismos de geração da distorção não linear em amplificadores Doherty, permitindo assim, a optimização do seu projeto, tendo em conta as especificações de linearidade e eficiência. Para além disso, esta abordagem permitirá uma ponte entre dois mundos diferentes: projecto de amplificadores de potência e pré-distorção digital, uma vez que o conhecimento recolhido da operação do Doherty ajudará na escolha de modelos de pré-distorção mais adequados.

#### keywords

AM/AM, AM/PM, Device Modelling, Doherty Amplifiers, High Efficiency, Linearity, Load Modulation, Nonlinear Distortion, Power Amplifier

#### abstract

Nowadays, wireless communications systems demand for greater mobility and higher data rates. Moreover, the need for spectral efficiency requires the use of non-constant envelope modulation schemes. Hence, power amplifier designers have to build highly efficient, broadband and linear amplifiers. In order to fulfil these strict requirements, the practical Doherty amplifier seems to be the most promising technique. However, due to its complex operation, its nonlinear distortion generation mechanisms are not yet fully understood. Currently, only heuristic interpretations are being used to justify the observed phenomena. Therefore, the main objective of this work is to provide a model capable of describing the Doherty power amplifier nonlinear distortion generation mechanisms, allowing the optimization of its design according to linearity and efficiency criteria. Besides that, this approach will allow a bridge between two different worlds: power amplifier design and digital pre-distortion since the knowledge gathered from the Doherty operation will serve to select the most suitable pre-distortion models.

### **Table of Contents**

| TABLE OF (  | CONTENTS                                                    |            |

|-------------|-------------------------------------------------------------|------------|

| LIST OF FIG | URES                                                        | V          |

| LIST OF TAI | BLES                                                        | IX         |

| LIST OF AC  | RONYMS                                                      | XI         |

| 1. INTRO    | DDUCTION                                                    | 1          |

|             | ekground and Motivation                                     |            |

| 1.2. Sta    | te-of-the-Art                                               |            |

| 1.2.1       | Doherty Power Amplifier Architecture                        | 5          |

| 1.2.2       | Distortion Analysis of the Doherty Amplifier                | 7          |

| 1.2.3       | Efficiency Enhancement Techniques in the Doherty Amplifier  | 9          |

| 1.3. Obj    | ectives and Thesis' Organization                            | 12         |

| 1.4. Mai    | n Contributions                                             | 14         |

|             | INEAR MODELLING OF POWER TRANSISTORS USEFUL FOR NONLINEAR   |            |

| DISTORTION  | N ANALYSIS                                                  | 17         |

| 2.1. Ger    | neral Nonlinear Model Extraction                            | 18         |

| 2.1.1       | Extraction Procedure                                        | 18         |

| 2.1.2       | Practical Example of High Power Device Modelling            | 36         |

| 2.2. Nor    | nlinear Model Extraction Methodology suitable for GaN HEMTs | 42         |

| 2.2.1       | GaN HEMT Trapping Effects                                   | <i>4</i> 3 |

| 2.2.2       | Drain-lag Phenomenon and its Effects on the I/V curves      | 44         |

| 2.2.3       | Nonlinear Model Formulation                                 | 47         |

| 224         | Extraction Procedure                                        | 48         |

| 2.2.5   | Model Validation                                                                        | 56  |

|---------|-----------------------------------------------------------------------------------------|-----|

| 2.3.    | Summary                                                                                 | 59  |

| 3. No   | ONLINEAR DISTORTION GENERATION MECHANISMS OF THE CARRIER AND                            |     |

| PEAKING | OPERATING AS SINGLE-ENDED AMPLIFIERS                                                    | 61  |

|         | Semi-Analytical Nonlinear Distortion analysis                                           |     |

| 3.2.    | AM/AM and AM/PM on a Si LDMOS FET based PA                                              |     |

| 3.2.1   | Equivalent Circuit Model of the LDMOS-PA                                                | 65  |

| 3.2.2   | i <sub>DS</sub> (V <sub>GS</sub> ,V <sub>DS</sub> ) Induced AM/AM and AM/PM Distortions | 67  |

| 3.2.3   | C <sub>gs</sub> (v <sub>Gs</sub> ) and C <sub>gd</sub> Induced AM/PM Distortion         | 70  |

| 3.2.4   | C <sub>ds</sub> (v <sub>DS</sub> ) Induced AM/PM Distortion                             | 72  |

| 3.3.    | AM/AM and AM/PM on a GaN HEMT BASED PA                                                  | 75  |

| 3.3.1   | Equivalent Circuit Model of the GaN HEMT-PA                                             | 75  |

| 3.3.2   | i <sub>DS</sub> (v <sub>GS</sub> ,v <sub>DS</sub> ) Induced AM/AM and AM/PM Distortions | 76  |

| 3.3.3   | $C_{gs}(v_{GS})$ and $C_{gd}$ and $C_{ds}(v_{DS})$ Induced AM/PM Distortion             | 77  |

| 3.4. I  | Experimental Validation                                                                 | 78  |

| 3.5.    | Summary                                                                                 | 80  |

|         | ONLINEAR DISTORTION GENERATION MECHANISMS OF THE OVERALL DOHER                          |     |

| 4.1.    | Theoretical Analysis of a 2-way Doherty PA and its Limitations                          | 83  |

|         | Nonlinear Distortion of a Doherty PA                                                    | 85  |

| 4.2.1   | AM/PM Distortion in GaN HEMT Doherty Power Amplifiers                                   | 86  |

| 4.2.2   | AM/PM Distortion in Si LDMOS Doherty Power Amplifiers                                   | 90  |

| 4.3.    | General Approach for Distortion Analysis                                                | 92  |

| 4.3.1   | Behavioural Model Based on Passive Load-Pull Data                                       | 94  |

| 4.3.2   | Application to a Practical Doherty Power Amplifier                                      | 96  |

| 4.4. I  | Efficiency Analysis of the Doherty Amplifier                                            | 98  |

| 4.4.1   | Efficiency Dependence on the Doherty PA Load-Pull Ratio                                 | 99  |

| 4.4.2   | Impact of Trapping Effects on GaN HEMT Based Doherty PA Load-Pull Ratios                | 106 |

| 4.5.    | Summary                                                                                 | 109 |

| 5.   | CONCLUSION AND FUTURE WORK | 111 |

|------|----------------------------|-----|

| 5.1. | . Future Work              | 112 |

| Refe | ERENCES                    | 115 |

## List of Figures

| Fig. 1.1 –  | Block diagram of a conceptual wireless communication base station transmitter link                                                                                                                                                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2 –  | Illustration of the PAPR problem.                                                                                                                                                                                                                                          |

| Fig. 1.3 –  | Conceptual $I_{DS}/V_{DS}$ characteristics of efficiency enhancement techniques by a) load modulation and b) supply voltage modulation                                                                                                                                     |

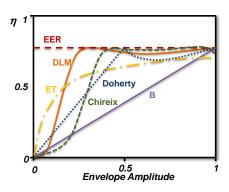

| Fig. 1.4 –  | Efficiency of the efficiency enhancement techniques (when class B operation mode is considered for the main amplifier) as a function of envelope amplitude                                                                                                                 |

| Fig. 1.5 –  | Classical block diagram of the Doherty architecture.                                                                                                                                                                                                                       |

| Fig. 1.6 –  | a) Load Lines of the carrier amplifier in the Doherty architecture; b) Voltages and c) Currents of the carrier and peaking amplifiers as function of the input voltage                                                                                                     |

| Fig. 1.7 –  | Normalized coefficients of the FET's nonlinear transconductance up to 3rd-order                                                                                                                                                                                            |

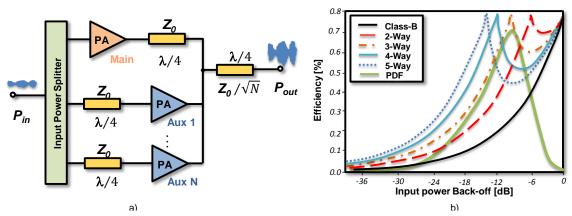

| Fig. 1.8 –  | N-Way Doherty Amplifier: a) N-Way block diagram; b) N-Way efficiency characteristic and the PDF of a W-CDMA signal with 10 dB of PAPR.                                                                                                                                     |

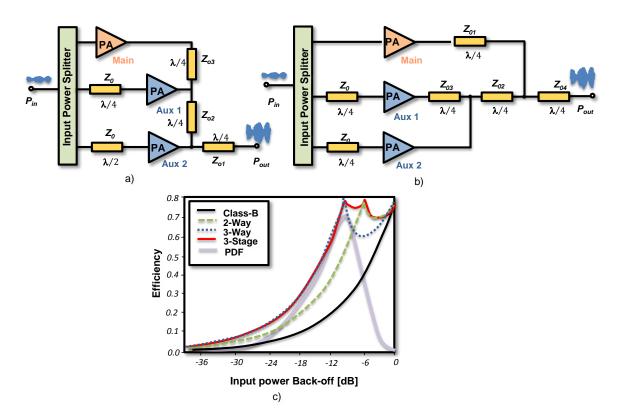

| Fig. 1.9 –  | Three-Stage Doherty Amplifier: a) and b) different types of a Three-Stage arrangements; c) Three-Stage efficiency characteristic and the PDF of a W-CDMA signal with 10 dB of PAPR11                                                                                       |

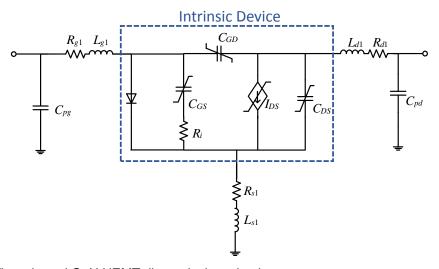

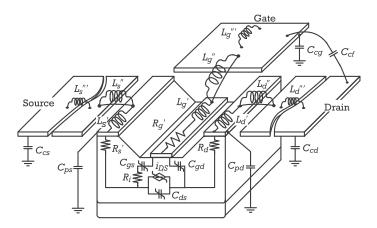

| Fig. 2.1 –  | The adopted GaN HEMT die equivalent circuit                                                                                                                                                                                                                                |

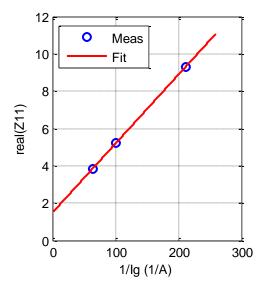

| -           | Curve-fitting of the real part of Z <sub>11</sub> versus the inverse of the gate current                                                                                                                                                                                   |

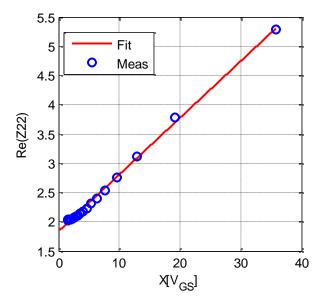

|             | Real part of $Z_{22}$ in triode zone to extract $R_c$ and $(R_d$ and $R_s)$                                                                                                                                                                                                |

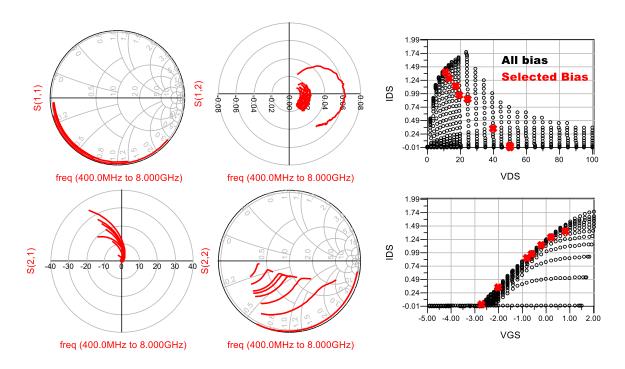

| J           | Estimated intrinsic S-parameters after de-embedding the extracted extrinsic components obtained using the analytical method.                                                                                                                                               |

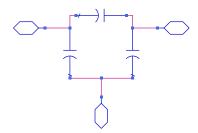

|             | FET channel equivalent circuit for $V_{DS} = 0$ and $V_{GS} << V_T$ .                                                                                                                                                                                                      |

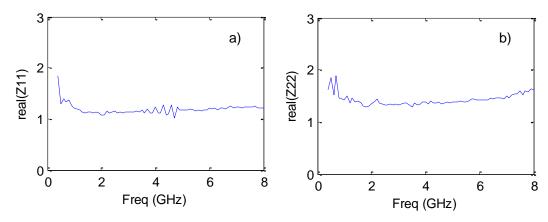

|             | Real part of a) Z <sub>11</sub> and b) Z <sub>22</sub>                                                                                                                                                                                                                     |

| Fig. 2.7 –  | FET channel equivalent circuit for $V_{DS} = 0$ and $V_{GS} >> V_T$ .                                                                                                                                                                                                      |

| -           | Curve-fitting to the S-parameters to extract all extrinsic components.                                                                                                                                                                                                     |

|             | Estimated intrinsic S-parameters after de-embedding the extracted extrinsic components obtained via optimization.                                                                                                                                                          |

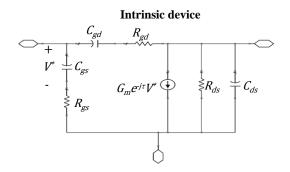

| _           | - Adopted model for the small-signal intrinsic device.                                                                                                                                                                                                                     |

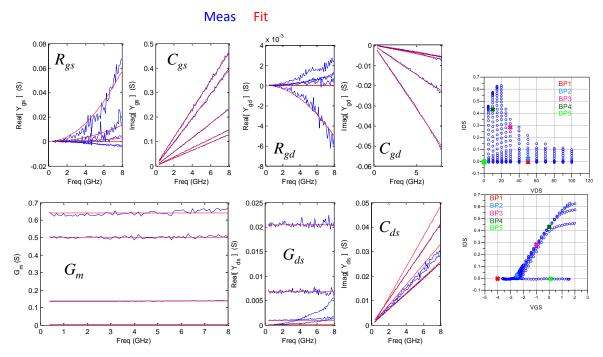

| -           | - Obtained curve fitting results for some bias points                                                                                                                                                                                                                      |

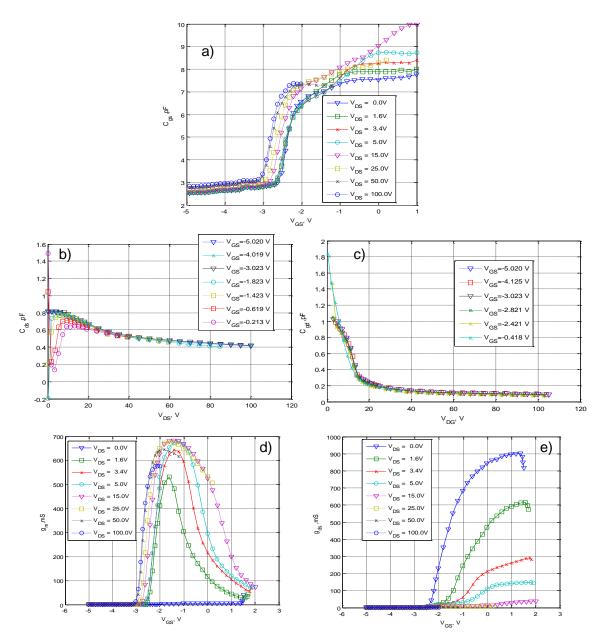

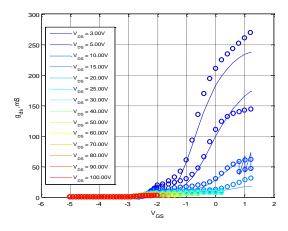

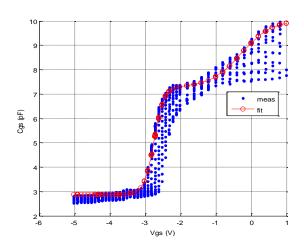

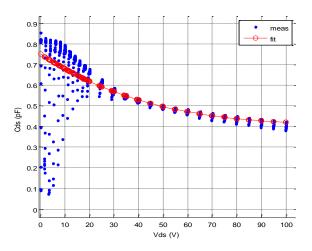

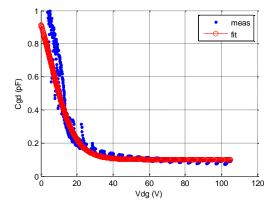

|             | - Extracted a) $C_{gs}$ ; b) $C_{ds}$ ; c) $C_{gd}$ ; d); $G_m$ e) $G_{ds}$ profiles.                                                                                                                                                                                      |

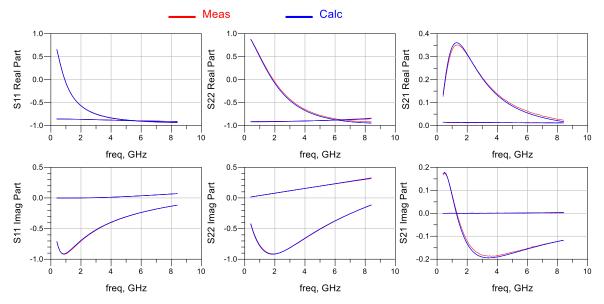

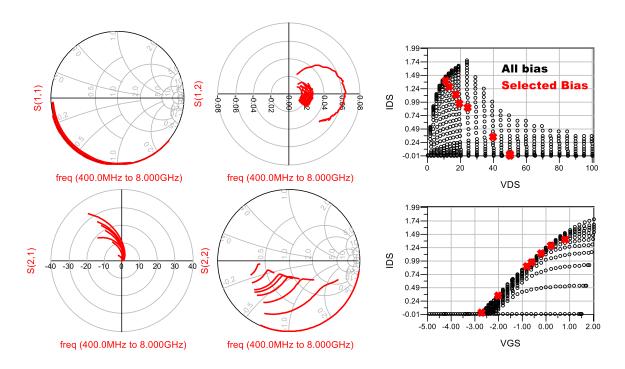

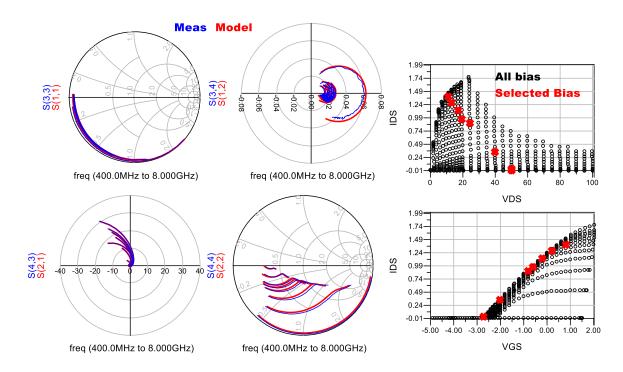

|             | - Comparison between the S-parameters obtained from measurements with the ones obtained from simulations of the small-signal bias dependent model                                                                                                                          |

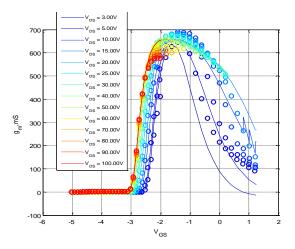

| _           | - Achieved fit of the large-signal model with the measured $G_m$                                                                                                                                                                                                           |

| _           | - Achieved fit of the large-signal model with the measured $G_{ds}$                                                                                                                                                                                                        |

| _           | - Achieved fit of the large-signal model with the measured $C_{ m gs.}$                                                                                                                                                                                                    |

| -           | - Achieved fit of the large-signal model with the measured $C_{ds}$                                                                                                                                                                                                        |

| -           | - Achieved fit of the large-signal model with the measured $C_{gd}$                                                                                                                                                                                                        |

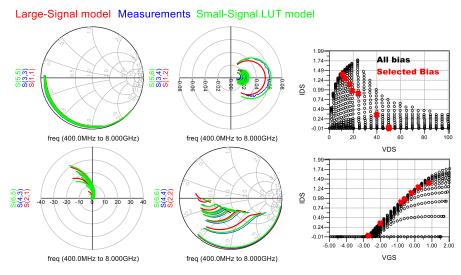

|             | - S-parameters of the large-signal model in comparison with the measured ones and with the ones obtained with small-signal bias dependent model.                                                                                                                           |

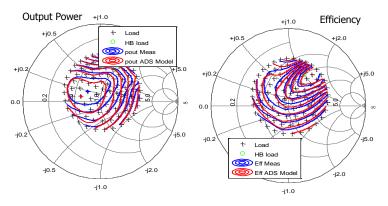

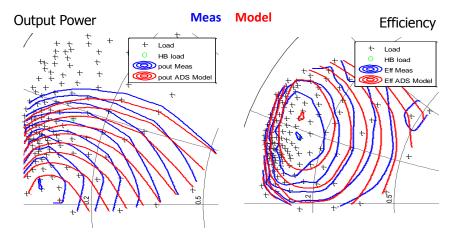

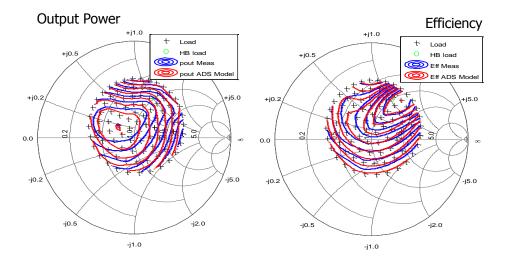

|             | - Simulated efficiency and output power load-pull contours in comparison with measurements for the 3mm device.                                                                                                                                                             |

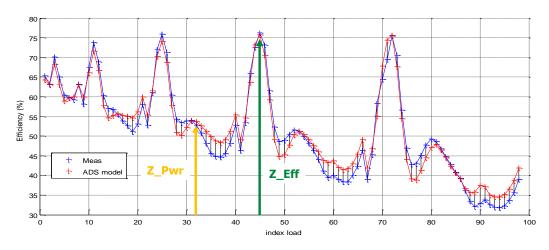

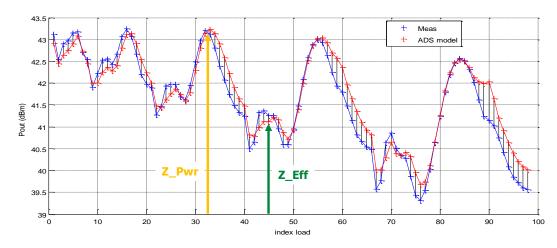

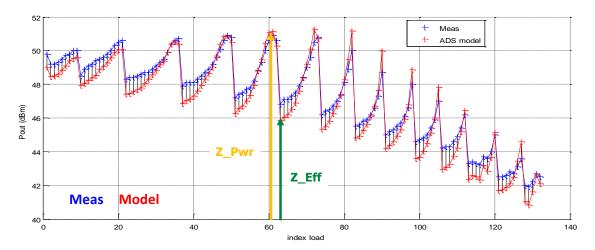

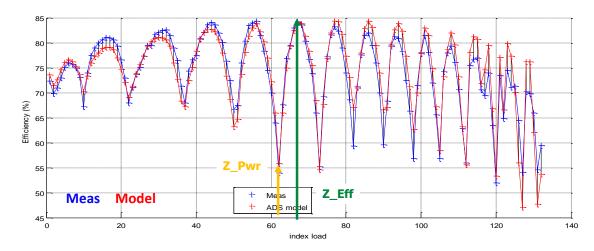

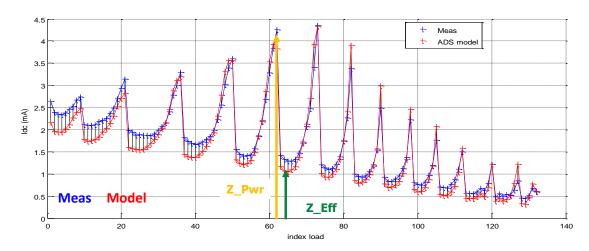

| •           | - Simulated efficiency in comparison with the measurements for different load impedances                                                                                                                                                                                   |

|             | - Simulated output power in comparison with the measurements for different load impedances.                                                                                                                                                                                |

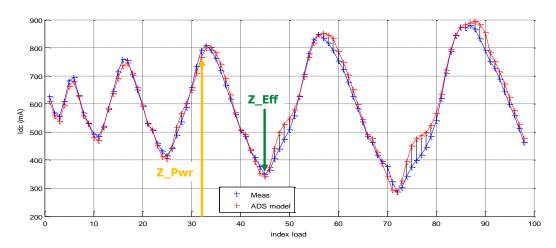

|             | - Simulated dc drain current in comparison with the measurements for different load impedances                                                                                                                                                                             |

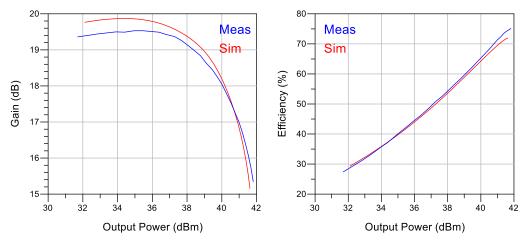

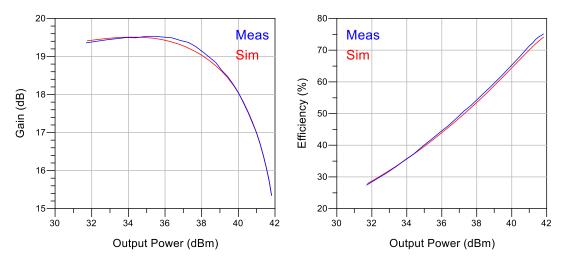

| -           | - Simulated Gain and efficiency versus output power in comparison with the measurements                                                                                                                                                                                    |

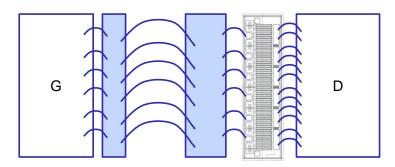

| •           | - Illustration of a FET device, from [3].                                                                                                                                                                                                                                  |

| -           | - Illustrative high power device structure.                                                                                                                                                                                                                                |

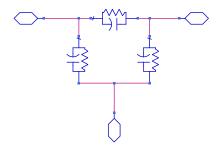

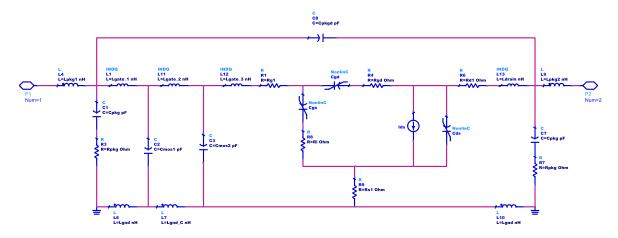

|             | - Package 6-Cell device equivalent circuit                                                                                                                                                                                                                                 |

| Fig. 2.28 - | - Simulated S-parameters (for $V_{DS}$ =50 V and $I_{dq}$ =100mA) of the model – when the package was extracted with a compromise between the S-parameters of the entire device and the small-signal from the swept input power data – in comparison with the measurements |

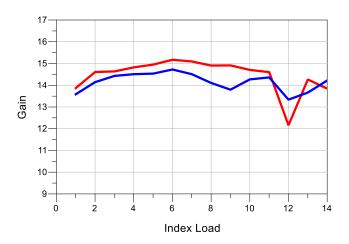

| Fig. | . 2.29 – | Small-Signal gain of the final model for different loads.                                                                                                                                                                       |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

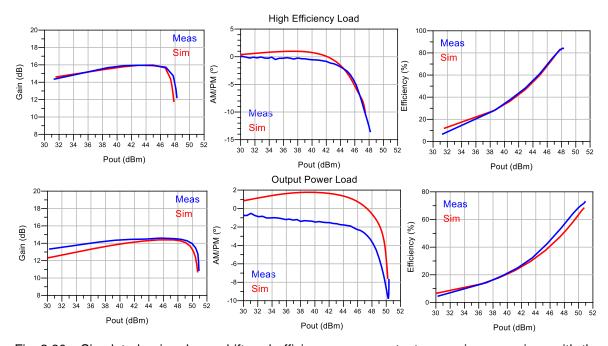

| Fig. | . 2.30 – | Simulated gain, phase shift and efficiency versus output power in comparison with the measurements of the 6-Cellx2.7mm GaN HEMT device.                                                                                         |

| Fig. | . 2.31 – | Efficiency and output power load-pull contours predictions in comparison with the measured ones of the 6-Cellx2.7mm GaN HEMT device.                                                                                            |

| Fig. | . 2.32 – | Simulated output power in comparison with the measurements for different load impedances for the 6-Cellx2.7mm GaN HEMT device.                                                                                                  |

| Fig. | . 2.33 – | Simulated efficiency in comparison with the measurements for different load impedances for the 6-Cellx2.7mm GaN HEMT device.                                                                                                    |

| Fig. | . 2.34 – | Simulated dc drain current in comparison with the measurements for different load impedances for the 6-Cellx2.7mm GaN HEMT device.                                                                                              |

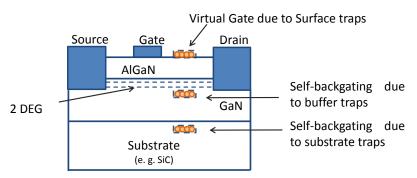

| Fig. | . 2.35 – | Illustration of the virtual gates in GaN HEMT devices due to the trapping effects                                                                                                                                               |

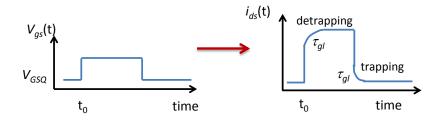

| Fig. | 2.36 –   | Illustration of the $V_{GS}$ step up and step down and the respective $I_{DS}$ response                                                                                                                                         |

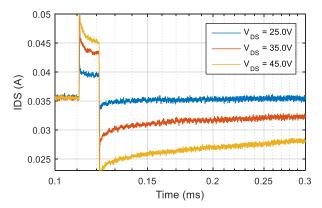

| Fig. | . 2.37 – | Illustration of the V <sub>DS</sub> step up and step down and the respective I <sub>DS</sub> response                                                                                                                           |

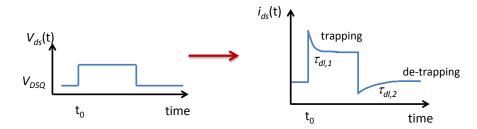

| Fig. | . 2.38 – | Zoom of the $i_{DS}$ pulses when $V_{GS}$ was pulsed for different values (from -5V to 0V) and $V_{DS}$ was kept constant and equal to 25V.                                                                                     |

| Fig. | . 2.39 – | Zoom of the $I_{DS}$ pulses when the $V_{DS}$ is pulsed for different values and the $V_{GS}$ is kept constant and equal to -2.6V.                                                                                              |

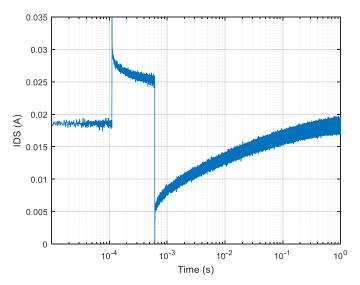

| Fig. | . 2.40 – | Measured i <sub>DS</sub> responses for a) v <sub>DS</sub> step up and b) step down stimuli                                                                                                                                      |

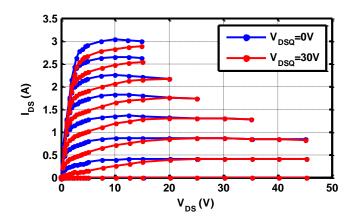

| Fig. | . 2.41 – | Comparison between two sets of measured pulsed I/V curves obtained with different quiescent $v_{DS}$ voltages, $V_{DSQ}$ =0V and $V_{DSQ}$ =30V                                                                                 |

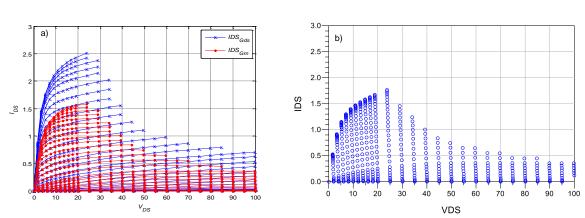

| Fig. | . 2.42 – | -I/V curves a) obtain by integration of the $G_m(V_{GS}, V_{DS})$ and $G_{ds}(VGS, V_{DS})$ and b) dc I/V curves.                                                                                                               |

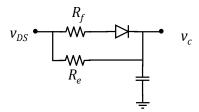

| Fig. | . 2.43 – | Trap charge and discharge equivalent circuit.                                                                                                                                                                                   |

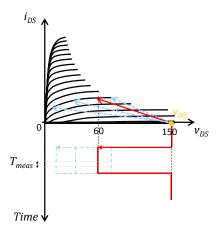

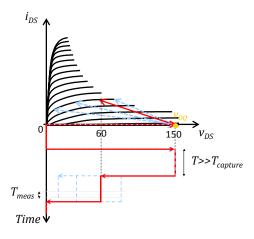

| Fig. | . 2.44 – | Illustration of the proposed measurement technique to obtain a quasi-static FET model                                                                                                                                           |

| Fig. | . 2.45 – | Illustration of the proposed double-pulsed measurement technique to obtain a quasi-static model without damaging the device by excessive power dissipation                                                                      |

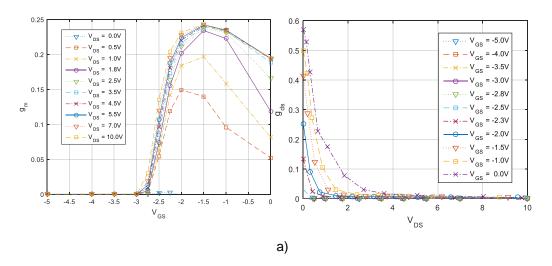

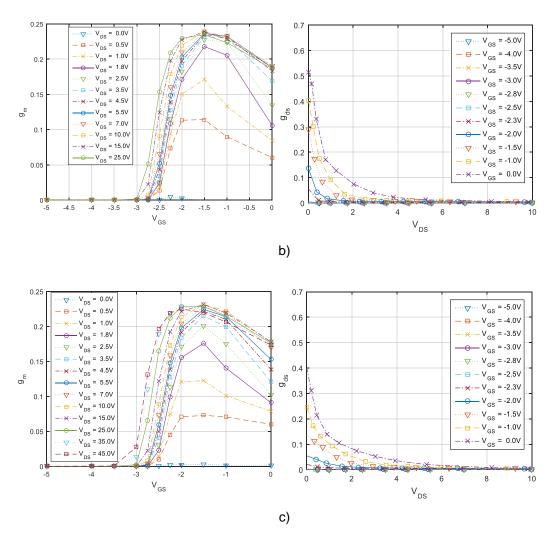

| Fig. | . 2.46 – | Obtained $G_m$ and $G_{ds}$ from the bias-dependent small-signal extraction for several $V_{DQs}$ voltages: a) $V_{DQ}=10V$ ; b) $V_{DQ}=25$ ; c) $V_{DQ}=45$                                                                   |

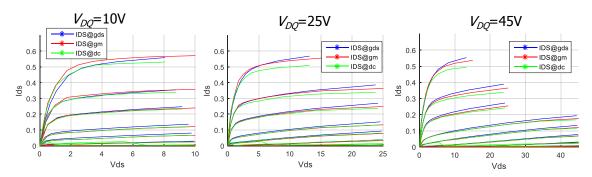

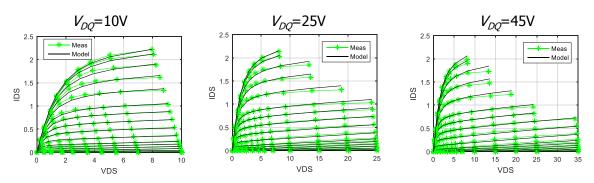

| Fig. | . 2.47 – | Obtained I/V curves by integration of the $G_m$ and $G_{ds}$ in comparison with the measured pulsed dc I/V curves                                                                                                               |

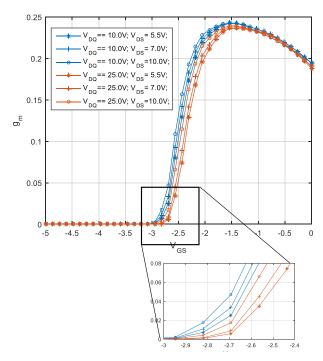

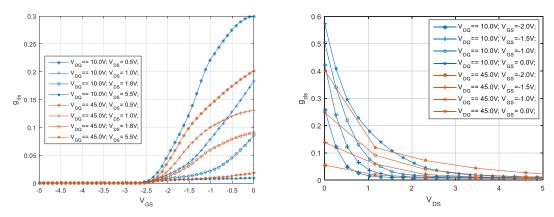

| Fig. | . 2.48 – | Observation of the threshold voltage variation in the extracted bias-dependent Gm for different pre-set voltage ( $V_{DSQ}$ =10V and $V_{DSQ}$ =45V)                                                                            |

| Fig. | . 2.49 – | Knee walkout observation in the extracted bias-dependent $G_{ds}$ for different pre-set voltages ( $V_{DSQ}$ =10V and $V_{DSQ}$ =45V).                                                                                          |

| Fig. | . 2.50 – | Modelled and measured I/V curves for different $v_{DS}$ preset pulses of the 1mm GaN HEMT die                                                                                                                                   |

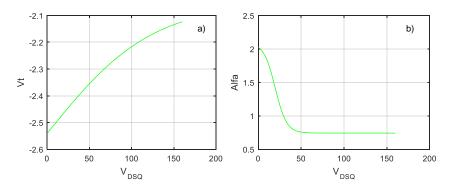

| Fig. | . 2.51 – | Extracted threshold voltage and $\alpha$ variations with the $v_{DS}$ preset pulse, or the intended $V_{T}[v_{C}(t)]$ and $\alpha[v_{C}(t)]$ , respectively.                                                                    |

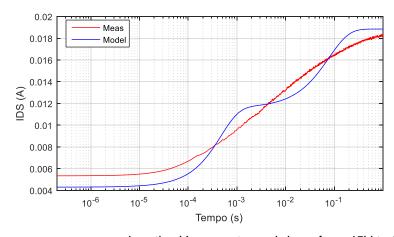

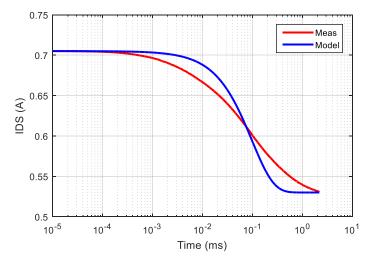

| Fig. | . 2.52 – | $i_{DS}$ recovery response when the $V_{DS}$ was stepped-down from 45V to 25V with a low and constant $V_{GS}$ voltage equal to -2.6V to avoid thermal effects. In comparison, it is also plotted the respective model fitting. |

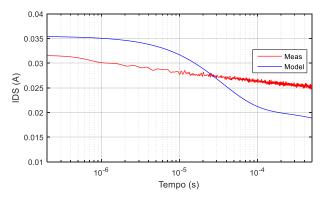

| Fig. | . 2.53 – | $i_{DS}$ trapping response when the $v_{DS}$ was stepped up from 25V to 45V with a low and constant $v_{GS}$ voltage equal to -2.6V to avoid thermal effects. In comparison, it is also plotted the respective model fitting.   |

| Fig. | . 2.54 – | Modelled and Measured electro-thermal dynamics                                                                                                                                                                                  |

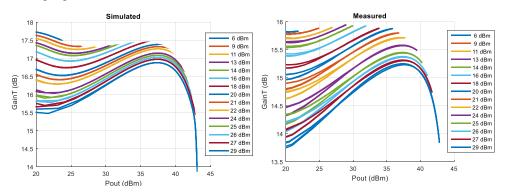

| Fig. | . 2.55 – | Simulated gain and efficiency versus output power, after the inclusion of the trapping effects, in comparison with the measurements                                                                                             |

| Fig. | . 2.56 – | Simulated efficiency and output power load-pull contours after the inclusion of the trapping effects, in comparison with the measurements.                                                                                      |

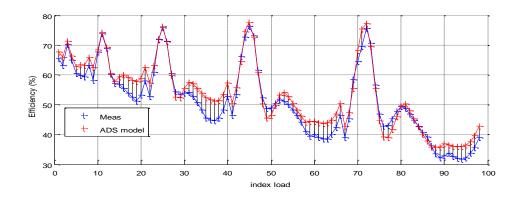

| Fig. | . 2.57 – | Simulated efficiency after the inclusion of the trapping effects, in comparison with the measurements.                                                                                                                          |

| Fig. | . 2.58 – | Simulated output power after the inclusion of the trapping effects, in comparison with the measurements.                                                                                                                        |

| Fig. | . 2.59 – | Simulated dc drain current after the inclusion of the trapping effects, in comparison with the measurements.                                                                                                                    |

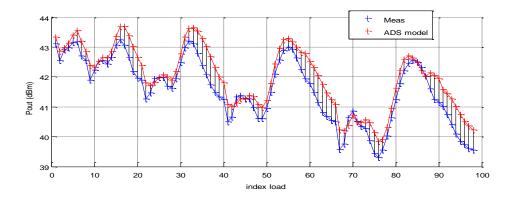

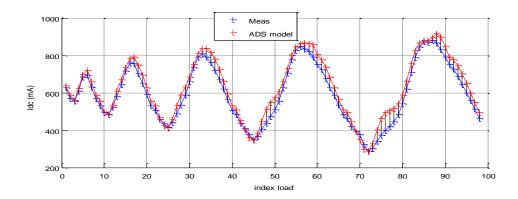

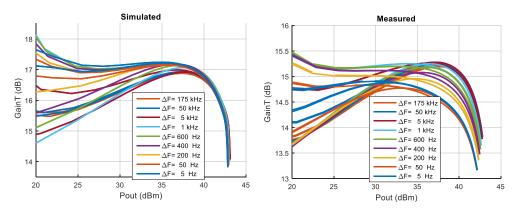

| Fig. 2.60 - | - Measured and simulated dynamic gain profiles with two-tones of various peak-envelope-powers                                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.61 - | - Measured and simulated dynamic gain profiles with two-tones of constant peak-envelope-power and of various frequency separations.                                                                                                                                                                                    |

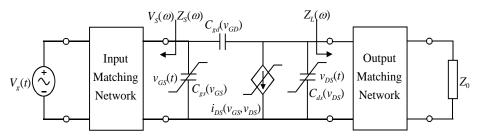

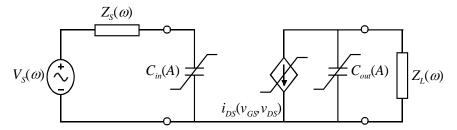

| Fig. 3.1 –  | Graphical representation of the adopted single-stage PA model.                                                                                                                                                                                                                                                         |

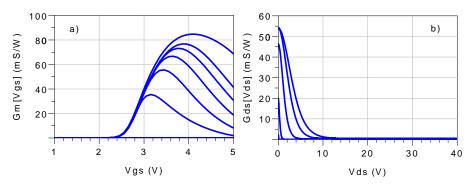

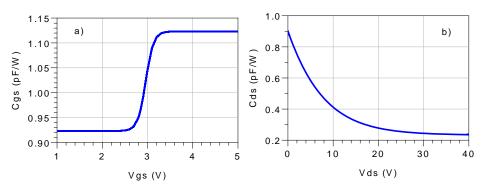

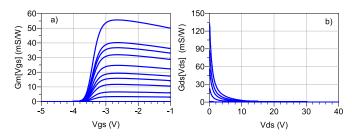

| Fig. 3.2 –  | Si LDMOS normalized a) transconductance $G_m(v_{GS})$ and b) output conductance $G_{ds}(v_{DS})$ profiles derived from the adopted $i_{DS}(v_{GS}, v_{DS})$ model.                                                                                                                                                     |

| Fig. 3.3 –  | Si LDMOS normalized a) gate-source capacitance $C_{gs}(v_{GS})$ and b) drain-source capacitance $C_{ds}(v_{DS})$ modelled profiles obtained from measured data                                                                                                                                                         |

| Fig. 3.4 –  | Simplified unilateral equivalent circuit model of the single-stage power amplifier                                                                                                                                                                                                                                     |

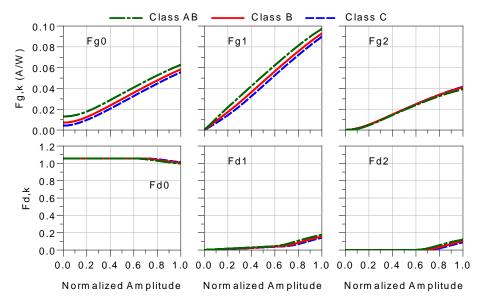

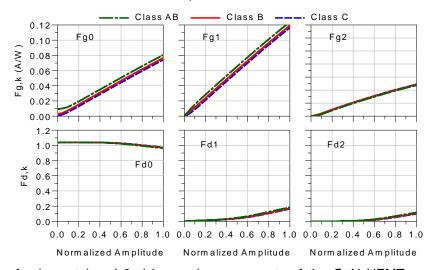

| Fig. 3.5 –  | DC, fundamental and $2^{nd}$ harmonic components of the normalized Si LDMOS time-varying $f_g(v_{GS})$ (top figure) and $f_g(v_{DS})$ (bottom figure)                                                                                                                                                                  |

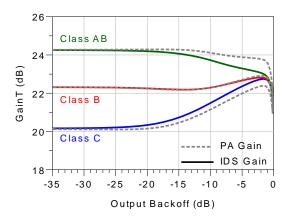

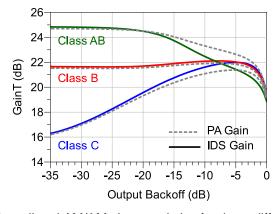

| Fig. 3.6 –  | Simulated and predicted AM/AM characteristics for three different operation classes of a Si LDMOS based PA. The slight differences between the complete PA AM/AM (PA Gain) and the one induced by the drain-source current nonlinearity ( $I_{DS}$ Gain) were attributed to the input capacitance variations           |

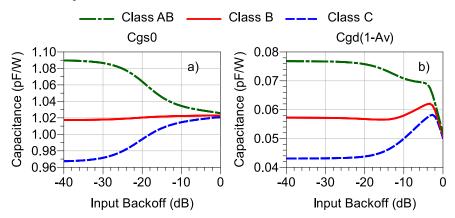

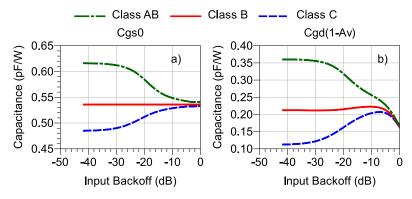

| Fig. 3.7 –  | Shapes of $C_{gso}(A)$ component of the LDMOS nonlinear normalized $C_{gs}$ and normalized input Miller reflected capacitance $C_{gd}$ .                                                                                                                                                                               |

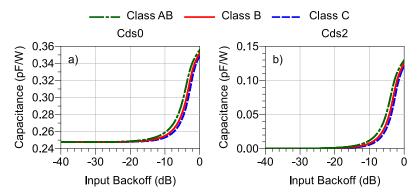

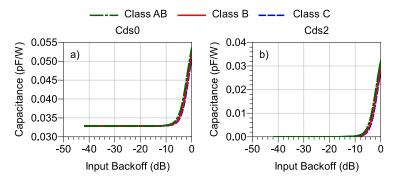

| •           | Shapes of $C_{ds0}(A)$ and $C_{ds2}(A)$ components of the normalized LDMOS nonlinear $C_{ds.}$                                                                                                                                                                                                                         |

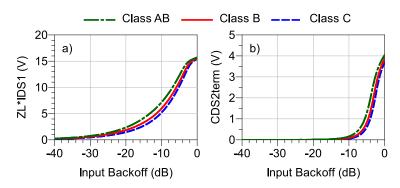

| Fig. 3.9 –  | a) Resistive and b) reactive terms of the numerator of (3.20) for the normalized LDMOS nonlinear $C_{ds}$                                                                                                                                                                                                              |

| Fig. 3.10 - | - Amplitude and phase of the denominator of (3.20) for the normalized LDMOS nonlinear $C_{ds}$                                                                                                                                                                                                                         |

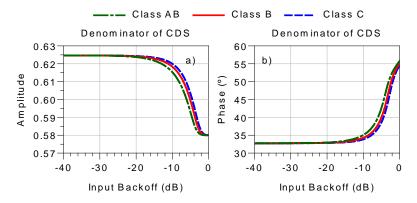

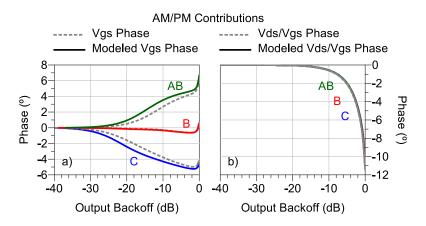

| Fig. 3.11 - | - a) Model predicted (Modelled Vgs Phase) and HB simulated ( $V_{gs}$ Phase) $C_{gs}$ and $C_{gd}$ contributions and b) model predicted (Modelled $V_{ds}/V_{gs}$ Phase) and HB simulated ( $V_{ds}/V_{gs}$ Phase) $C_{ds}$ contribution to the overall Si LDMOS AM/PM                                                 |

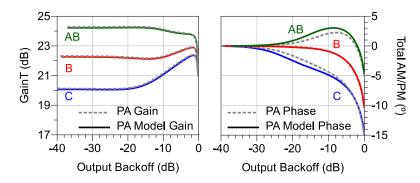

| Fig. 3.12 - | - Overall a) AM/AM and b) AM/PM of the Si LDMOS based PA. Model predictions and HB simulations are shown as continuous or dashed lines, respectively.                                                                                                                                                                  |

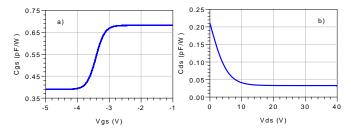

| Fig. 3.13 - | - GaN HEMT a) normalized transconductance $G_m(v_{GS})$ and b) normalized output conductance $G_{dS}(v_{DS})$ profiles derived from the adopted $i_{DS}(v_{GS},v_{DS})$ model                                                                                                                                          |

| Fig. 3.14 - | - GaN HEMT normalized a) gate-source capacitance $C_{gs}(v_{GS})$ and b) drain-source capacitance $C_{ds}(v_{DS})$ modelled profiles obtained from measured data                                                                                                                                                       |

| Fig. 3.15 - | - dc, fundamental and 2nd harmonic components of the GaN HEMT normalized time-varying $f_{\mathcal{G}}(v_{GS})$ and $f_{\mathcal{G}}(v_{DS})$                                                                                                                                                                          |

| Fig. 3.16 - | - Simulated and predicted AM/AM characteristics for three different operation classes of a GaN HEMT based PA. The differences between the complete PA AM/AM (PA Gain) and the one induced by the drain-source current nonlinearity ( <i>I</i> <sub>DS</sub> Gain) are due to the input capacitance variations.         |

| Fig. 3.17 - | - Shapes of $C_{ds0}(A)$ and $C_{ds2}(A)$ components of the normalized GaN HEMT nonlinear $C_{ds}$                                                                                                                                                                                                                     |

| -           | - Shapes of $C_{gs0}(A)$ component of the GaN HEMT nonlinear normalized $C_{gs}$ and of the normalized input Miller reflected capacitance $C_{gd}$ .                                                                                                                                                                   |

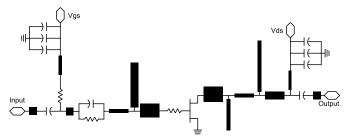

| Fig. 3.19 – | - Layout of the implemented and tested 15 W, 900 MHz, GaN HEMT power amplifier prototype.                                                                                                                                                                                                                              |

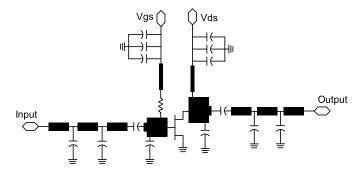

| Fig. 3.20 - | - Layout of the implemented and tested 200 W, 1800 MHz, Si LDMOS power amplifier prototype                                                                                                                                                                                                                             |

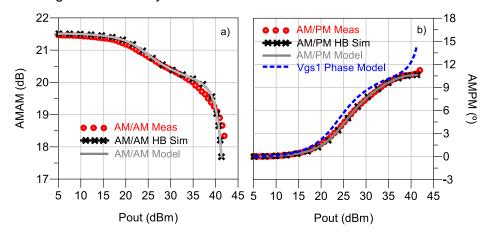

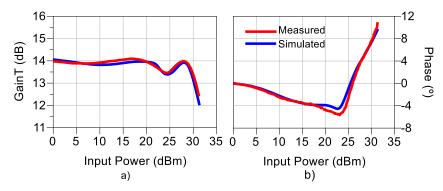

| Fig. 3.21 - | - a) AM/AM and b) AM/PM characteristic from lab measurements, HB simulation of a circuit-level model and predictions from the proposed semi-analytical model for the GaN HEMT based PA. For comparison purposes, fundamental gate-source voltage phase predicted by the proposed semi-analytical model is also plotted |

| Fig. 3.22 - | - a) AM/AM and b) AM/PM characteristic from lab measurements, HB simulation of a circuit-level model and predictions by the proposed semi-analytical model for the Si LDMOS based PA.                                                                                                                                  |

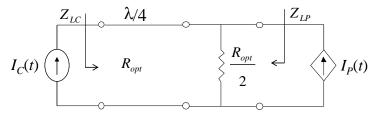

| Fig. 4.1 –  | Equivalent schematic of an ideal 2-way Doherty PA.                                                                                                                                                                                                                                                                     |

| -           | Simplification of the equivalent circuit schematic presented in Fig. 4.1                                                                                                                                                                                                                                               |

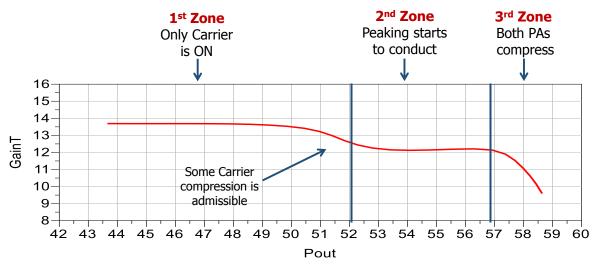

|             | Typical AM/AM of a Doherty PA with three different operation zones well defined                                                                                                                                                                                                                                        |

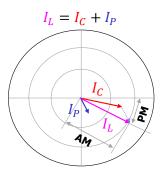

| -           | Illustration of the Doherty carrier and peaking PAs combined in magnitude and phase                                                                                                                                                                                                                                    |

|             | ,                                                                                                                                                                                                                                                                                                                      |

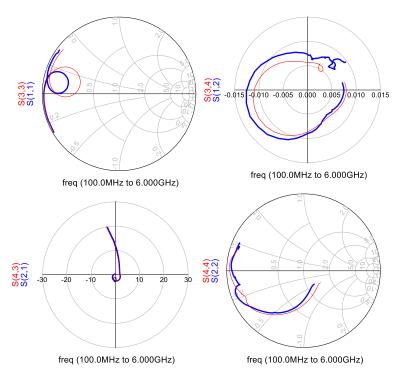

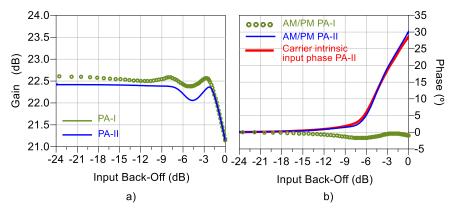

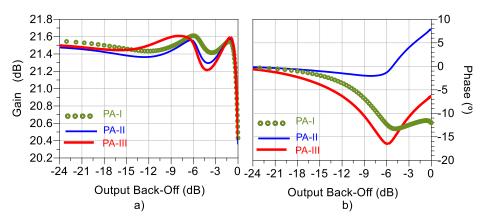

| Fig. 4.5 –  | a) Simulated transducer power gain and b) AM/PM characteristics of both DPAs. For comparison purposes, fundamental gate-source intrinsic voltage phase of the carrier PA-II is also plotted.                                                                                                                                                                                                                        |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

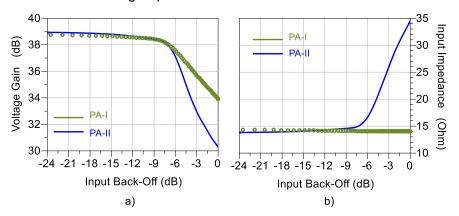

| Fig. 4.6 –  | a) Simulated voltage gain characteristic of the carrier PA and b) correspondent input impedance variation, of both DPAs.                                                                                                                                                                                                                                                                                            |

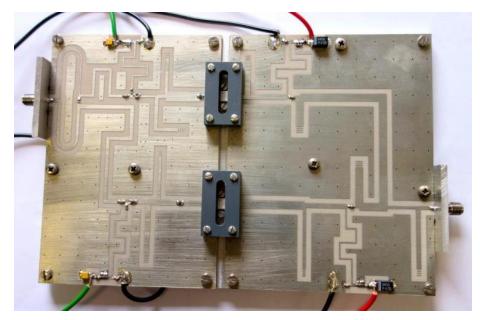

| Fig. 4.7 –  | Photograph of the implemented and tested 900MHz, GaN Doherty PA prototype                                                                                                                                                                                                                                                                                                                                           |

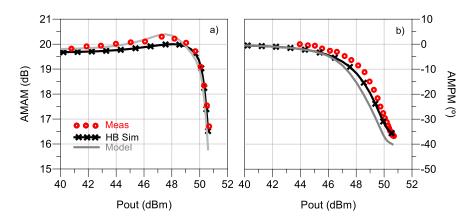

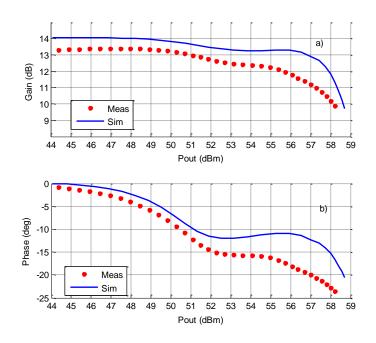

| Fig. 4.8 –  | Measured and simulated a) AM/AM and b) AM/PM characteristics of the implemented Doherty Power Amplifier prototype.                                                                                                                                                                                                                                                                                                  |

| Fig. 4.9 –  | a) Simulated transducer power gain and b) AM/PM characteristics of all Si LDMOS conceptual DPAs.                                                                                                                                                                                                                                                                                                                    |

| Fig. 4.10 - | - Measured and simulated a) AM/AM and b) AM/PM characteristics of the implemented Doherty power amplifier prototype                                                                                                                                                                                                                                                                                                 |

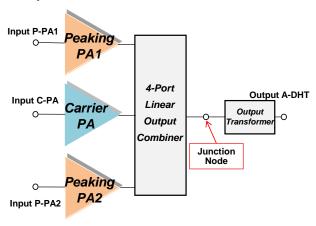

| -           | - Asymmetric 2-Way Doherty PA junction node selection example                                                                                                                                                                                                                                                                                                                                                       |

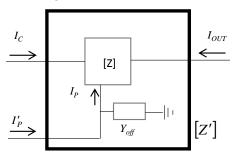

| Fig. 4.12 - | - Schematic representation of the embedding procedure of the peaking PA off output admittance in the combiner [Z] matrix                                                                                                                                                                                                                                                                                            |

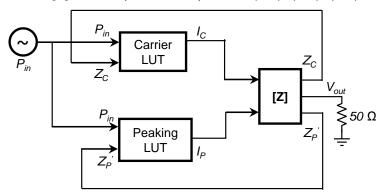

|             | - Block diagram implemented in Simulink to represent the asymmetric Doherty amplifier through LUT behavioural models.                                                                                                                                                                                                                                                                                               |

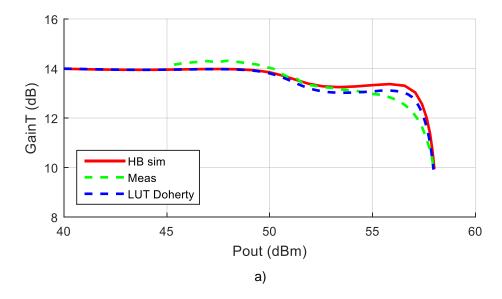

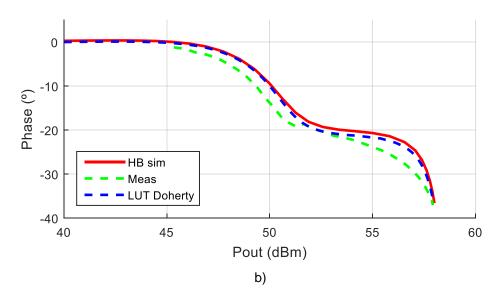

| Fig. 4.14 - | - Comparison between a) AM/AM and b) AM/PM measurements and simulations (obtained with ADS harmonic-balance and the Simulink LUT behavioural models)                                                                                                                                                                                                                                                                |

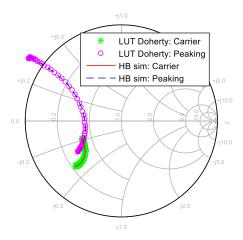

| Fig. 4.15 - | - Load modulation predictions obtained with ADS harmonic-balance and the Simulink LUT behavioural models                                                                                                                                                                                                                                                                                                            |

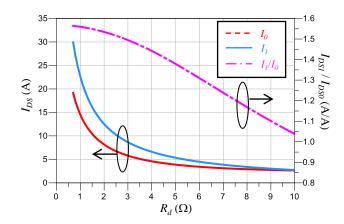

| Fig. 4.16 - | - Simulated dc, $I_0$ , and fundamental, $I_1$ , output current components of the FET, described by only the $i_{DS}(v_{GS},v_{DS})$ current source with a smooth turn-on. It is also plotted the ratio between $I_1$ and $I_0$ , which is the main responsible of the efficiency decrease when $R_d$ is increased                                                                                                  |

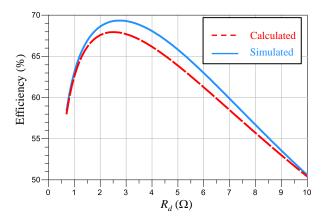

| Fig. 4.17 - | - An illustration of the calculated and simulated [through the smooth turn-on FET model] drain efficiency versus drain resistance profile, $\eta(R_d)$                                                                                                                                                                                                                                                              |

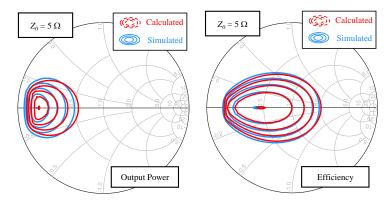

| Fig. 4.18 - | - An illustration of the calculated and simulated [of a real $i_{DS}(v_{GS}, v_{DS})$ current source model of the 250W Si LDMOS device used in the validation sub-section] drain efficiency load-pull contours ( $\eta_{Step}$ =5%, $\eta_{Max,simulated}$ =69.3% and $\eta_{Max,calculated}$ =67.9%)                                                                                                               |

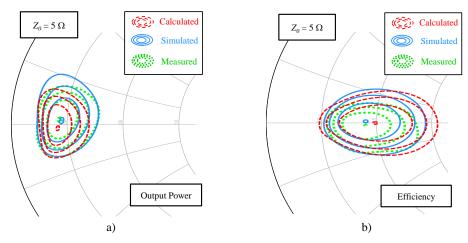

| Fig. 4.19 - | – A comparison between the output power ( $P_{Step}$ =0.5 dB, $P_{Max,simulated}$ =55.7 dBm, $P_{Max,measured}$ =54.2 dBm and $P_{Max,calculated}$ =54.5 dBm) a) and efficiency ( $\eta_{Step}$ =2 %, $\eta_{Max,simulated}$ =74.7 %, $\eta_{Max,measured}$ =70.2 % and $\eta_{Max,calculated}$ =67. 9%) b) load-pull contours predicted by the proposed theory and measured in the 250 W pre-matched Si LDMOS FET, |

|             | after transformation to the intrinsic device reference plane                                                                                                                                                                                                                                                                                                                                                        |

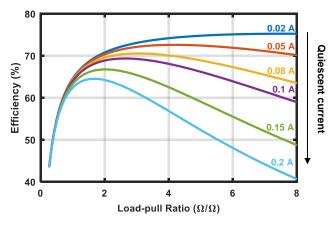

| Fig. 4.20 - | - Illustrative behaviour of the efficiency variation with the load impedance for increasing quiescent currents                                                                                                                                                                                                                                                                                                      |

| Fig. 4.21 - | <ul> <li>Comparison between the measured 900MHz CW gain profiles of the GaN HEMT (class B operation) and Si LDMOS (class B and class C) devices terminated with their maximum output power loads. In addition, it is also shown the measured gain profile when the GaN HEMT was excited with a fast two-tone signal.</li> </ul>                                                                                     |

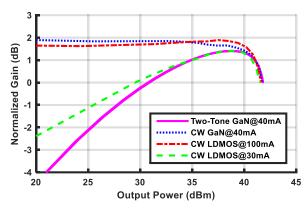

| Fig. 4.22 - | - Measured load-pull a) output power and b) PAE contours of a Si LDMOS device for two different bias points                                                                                                                                                                                                                                                                                                         |

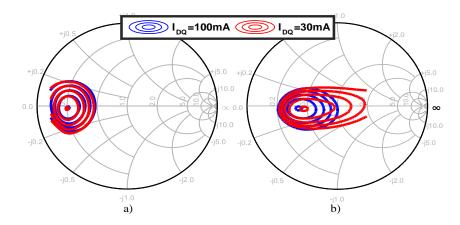

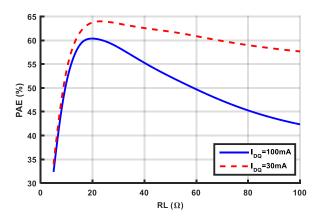

| Fig. 4.23 - | - Measured PAE dependence on the load resistance of a Si LDMOS device for two different bias points                                                                                                                                                                                                                                                                                                                 |

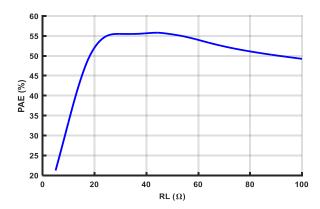

| Fig. 4.24 - | - Measured PAE dependency on the drain impedance of a GaN HEMT device                                                                                                                                                                                                                                                                                                                                               |

### List of Tables

| Table 2.1 – Extracted extrinsic components using the analytical method.   | 21 |

|---------------------------------------------------------------------------|----|

| Table 2.2 – Extracted extrinsic components using optimization methods.    | 24 |

| Table 2.3 – Parameters of the $i_{DS}(v_{GS}, v_{DS})$ large-signal model | 31 |

| Table 2.4 – Parameters for all large-signal models of the capacitances.   | 32 |

### List of Acronyms

ADS Advanced Design System

AM Amplitude Modulation

AM/AM Amplitude Modulation to Amplitude Modulation

AM/PM Amplitude Modulation to Phase Modulation

CAD Computer Aided Design

CW Continuous Wave

DC Direct Current

DLM Dynamic Load Modulation

DHT Doherty

DPA Doherty Power Amplifier

DPD Digital Pre-Distortion

DSP Digital Signal Processing

GaN Gallium Nitride

EER Envelope Elimination and Restoration

ET Envelope Tracking

FET Field Effect Transistor

H-EER Hybrid-Envelope Elimination and Restoration

HB Harmonic Balance

HEMT High Electron Mobility Transistor

IMD Intermodulation Distortion

LDMOS Laterally Diffused Metal Oxide Semiconductor

LTE Long-Term Evolution

LUT Look-Up Table

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOSCAP Metal Oxide Semiconductor Capacitor

MESFET Metal-Semiconductor Field Effect Transistor

PA Power Amplifier

PAE Power Added Efficiency

PAPR Peak to Average Power Ratio

PD Pre-Distortion

PM Phase Modulation RF Radio Frequency

RFPA Radio frequency Power Amplifier

### Nonlinear Distortion Generation Mechanisms in Doherty Amplifiers

Si Silicon

VoHB Volterra on top of Harmonic-Balance

W-CDMA Wideband Code Division Multiple Access

WiMAX Worldwide Interoperability for Microwave Access

### 1. Introduction

### 1.1. Background and Motivation

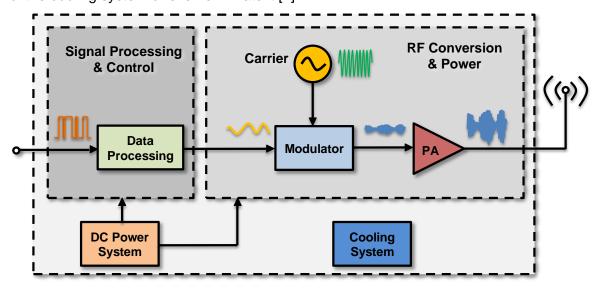

Energy consumption is one of the most important issues in all kinds of applications. Wireless communication systems are no exception, considering that a remarkable effort has been put in increasing the efficiency of their building blocks in order to decrease the overall energy consumption of the whole architecture. Fig. 1.1 represents a general block diagram of a conceptual wireless communication base station transmitter, which is composed of four main blocks: signal processing and control section, RF conversion and power amplification part, power supply system and cooling sector.

The most challenging part of a base station, in terms of energy consumption, is the final stage of the RF power amplification (about 40% of overall energy consumption [1]). Therefore, it is very important to increase the efficiency of the power amplifier, which translates into a direct reduction in its energy consumption. In addition, this efficiency enhancement of the power amplifier also allows for a reduction in the power consumption of the cooling system or even eliminate it [2].

Fig. 1.1 – Block diagram of a conceptual wireless communication base station transmitter link.

In addition, modern wireless communication systems try to find solutions to solve problems that appeared with the rapid growth of data rates and with the increased demand for mobility. Moreover, the very strict spectral masks imposed by telecommunication regulators, lead to the development of complex modulation formats, such as Wideband Code Division Multiple Access (W-CDMA), Long-Term Evolution (LTE) and Worldwide Interoperability for Microwave Access (WiMAX).

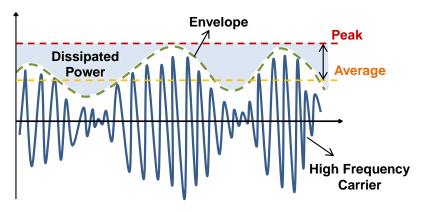

These new signals, modulated in amplitude, AM, and phase, PM, have large peak-to-average power ratios (PAPR) [3] – i.e., the ratio between the average and peak power values (it can reach up to 12 dB) – and whose relative bandwidths may reach, in extreme cases, 20% of the carrier frequency. This being the case, conventional current-mode power amplifiers are no longer a solution, since they are extremely inefficient when operated in back-off mode [4], as is illustrated in Fig. 1.2.

Fig. 1.2 – Illustration of the PAPR problem.

In this scenario, over the last decades, new techniques have appeared to improve the average efficiency of power amplifiers without degrading their linearity [5]–[9]. Actually, these techniques became new radio frequency transmitter architectures and they can be divided in two different strategies: PA supply voltage modulation and load modulation.

To understand the operating principle of these new techniques, let us concentrate on a classical class B power amplifier, whose efficiency is a function of amplitude,  $V_i(t)$ , given by:

$$\eta = \frac{P_{out}(t)}{P_{dc}(t)} = \frac{\pi}{8} \frac{R_L}{V_{dc}} G_m V_i(t)$$

(1.1)

where  $R_L$  is the load impedance,  $V_{dc}$  is the supply voltage and  $G_m$  is the transconductance of the transistor. To ensure linearity, the maximum PA signal excursion is limited by the knee voltage,  $V_K$ , otherwise the transistor enters the triode zone. Therefore, if the analysis is restricted to the case of fixed load and power supply voltage, the maximum efficiency is only obtained when the envelope peaks are equal to (1.2).

$$V_{i,Max} = 2 \frac{V_{dc} - V_K}{G_m R_L} {1.2}$$

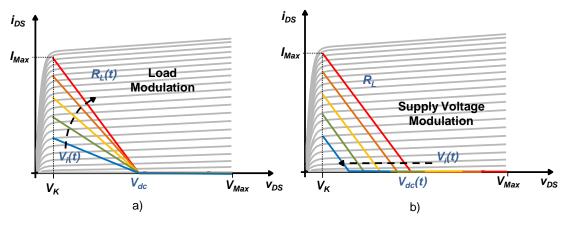

In order to solve the problem mentioned above, the supply voltage modulation technique dynamically reduces  $V_{dc}$  with the decrease of the amplitude envelope, whereas in the case of the load modulation technique it is the load that dynamically decreases with the increase of the amplitude envelope. As can be seen from (1.1) and from the illustration of the conceptual  $I_{DS}/V_{DS}$  characteristics of these techniques, in a class B power amplifier (Fig. 1.3), the amplifier will always be at the maximum efficiency point, thereby eliminating the waste of power consumption in zones of high output power back-off.

Fig. 1.3 – Conceptual  $I_{DS}/V_{DS}$  characteristics of efficiency enhancement techniques by a) load modulation and b) supply voltage modulation.

On one hand, regarding efficiency enhancement techniques by power supply voltage modulation, there are the EER [5][10], ET [11]–[14], H-EER [9][15] and Polar architectures [7]. On the other hand, recognized load modulation techniques in literature are the Doherty [16], Chireix Outphasing [17], and Dynamic Load Modulation architectures (DLM) [18]–[20]. Fig. 1.4 shows a comparison of the efficiency of all these techniques (when class B operation mode is considered for the main amplifier) as a function of envelope amplitude.

The Doherty architecture has been considered one of the most powerful architectures to extend the PA high efficiency operation region by the scientific community and the industrial community. The Doherty architecture was proposed in the 30s by W. H. Doherty [16] and today it is again reconsidered. It is based on the principle of active load modulation and the classical topology of this architecture uses two power amplifiers called the main and auxiliary amplifier, as shown in Fig. 1.5. Nevertheless, it is possible to use more than one auxiliary amplifier, which results in the so-called N-way Doherty or N-stage Doherty, depending on how the peaking amplifiers are interconnected [21]–[24]. The auxiliary amplifiers collaborate with the main amplifier so that it maintains a high efficiency for lower levels of input power and without saturating for high values of input power.

Fig. 1.4 – Efficiency of the efficiency enhancement techniques (when class B operation mode is considered for the main amplifier) as a function of envelope amplitude.

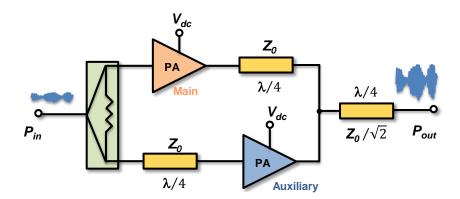

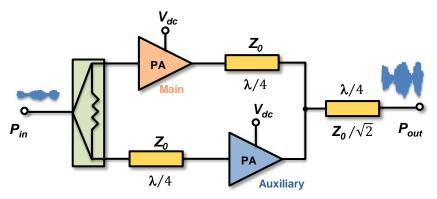

Fig. 1.5 – Classical block diagram of the Doherty architecture.

Although the Doherty amplifier presents a high efficiency for a wide range of input power levels, as well as it allows the use of new signals with high bandwidth, the practical Doherty amplifier presents a nonlinear behaviour due to the imperfect load modulation and the nonlinear behaviour of each of its amplifiers [22].

The nonlinear phenomena observed in the Doherty amplifier are explained in the literature [21], [25], [26] based on the behaviour of active devices operating in small signal, i.e. in the linear regime, and considering only the amplitude modulation to amplitude modulation (AM/AM) characteristics. This theory is centred on the fact that the main amplifier operates in class AB and the auxiliary amplifiers operates in class C, presenting compressive and expansive AM/AM characteristics, respectively. The auxiliary amplifiers compensate the compressive behaviour of the main amplifier resulting in a minimum of intermodulation distortion of the entire Doherty amplifier. However, even this justification which addresses only the AM/AM characteristic, is invalid because the Doherty amplifier is commonly used for very large signals, when their amplifiers are already very nonlinear.

The industry makes the amplifiers operate in a very nonlinear regime for energy efficiency optimization reasons. Therefore, as the mechanisms of nonlinear distortion

generation and control in the Doherty Amplifier are not yet fully understood, the linearization schemes used until now (in most cases digital pre-distortion) are chosen following a purely heuristic approach [27]–[30] and, consequently, with only a moderate probability of success. This way, the main objective of this PhD thesis work is to provide a model capable of describing and explaining the distortion generation mechanisms of a Doherty amplifier based on the most common RF transistor technologies presently used in power amplifiers for cellular infrastructures: the Si LDMOS and the GaN HEMT. This will enable the design of an amplifier with a better compromise between efficiency and linearity and the establishment of linearization schemes more suited to the compensation of these distortion generation mechanisms.

#### 1.2. State-of-the-Art

This section is dedicated to present an overview of the state-of-the-art regarding the Doherty power amplifier. It starts by a brief description of the ideal Doherty power amplifier architecture, presenting its main blocks and how they interact to obtain the desired high efficiency without compromising the linearity.

Secondly, the aspects of a practical Doherty power amplifier implementation that differ from the aforementioned theoretical analysis are presented. On this regard, the published studies concerning nonlinear distortion, for single-ended power amplifiers used to build the Doherty architecture, are discussed. After that, single-ended nonlinear distortion interactions in a Doherty arrangement are addressed.

Finally, the Doherty PA efficiency optimization, namely on what concerns techniques to improve the efficiency at higher back-off levels (beyond the 6dB of the conventional design) are presented.

#### 1.2.1 Doherty Power Amplifier Architecture

Doherty amplifier has been the most promising wireless communications PA architecture for base-stations. It was proposed in 1936 by W. Doherty [16] as a solution to the problem of efficiency degradation in the presence of a fully modulated signal in the Chireix architecture. Doherty attributed this reduction of efficiency to the fact that the Chireix arrangement does not work on completely resistive loads as his system does [16]. Therefore, the Doherty amplifier emerges as an architecture based on the principle of active load modulation capable of providing a high efficiency without compromising the linearity.

The classical arrangement of the Doherty amplifier (2-Way) can be seen in Fig. 1.5. It consists of a power splitter that divides the input signal into two branches, and then it uses two amplifiers (the main and auxiliary amplifiers), which are interconnected through a quarter-wavelength line. The main amplifier (also known as the carrier amplifier) is normally biased in class B, while the auxiliary amplifier (also known as the peaking amplifier) is biased in a moderate or deep class C. Thus, when the input power is very low it is assumed that the peaking amplifier is cut-off, i.e. the output current provided by the peaking PA,  $I_P$ , is equal to zero. Therefore, for low levels of input power, there is only the carrier PA, operating as a single-ended class B PA except that it is terminated by a load that is exactly twice the one expected in a conventional class B.

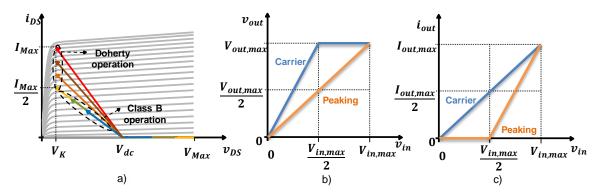

With the increase of the power level of the excitation signal, the efficiency of the main amplifier will increase until it reaches its peak (ideally 78.5%). It should be noted that, as the load impedance is twice the one expected in a conventional class B PA, this maximum peak is expected when the input voltage reaches half of the admissible excursion signal,  $V_{in,max}/2$ , as shown in Fig. 1.4 and Fig. 1.6.

Fig. 1.6 – a) Load Lines of the carrier amplifier in the Doherty architecture; b) Voltages and c) Currents of the carrier and peaking amplifiers as function of the input voltage.

In order to prevent the carrier amplifier from entering the triode zone, when the input voltage becomes higher than  $V_{in,max}/2$ , the peaking amplifier becomes active providing the necessary current to reduce the load impedance of the carrier amplifier. Actually, the peaking and carrier amplifiers behave as active loads to each other. From this point on, the main amplifier will operate as a voltage source and with a constant efficiency. When, finally the auxiliary amplifier reaches its maximum efficiency, the second point of maximum efficiency of the Doherty amplifier is obtained, as shown in Fig. 1.4.

In practice, there are some aspects to take into account that differ from the theoretical analysis described above. Firstly, a class B amplifier introduces distortion even before reaching the triode zone. In addition, a class C amplifier does not provide the

desired abrupt transition from the cut-off region to the region of perfectly linear operation, and the current gain provided by the class C peaking amplifier is less than the one of a class B amplifier. These nonlinear contributions from each amplifier will also degrade the theoretical load modulation, which results in a further nonlinear behaviour [8].

#### 1.2.2 Distortion Analysis of the Doherty Amplifier

As mentioned above, the Doherty amplifier combines two amplifiers (supposedly current-mode amplifiers) through a quarter-wavelength line, where each sub-amplifier has its associated nonlinear distortion. Therefore, in order to understand the nonlinear distortion of the whole Doherty amplifier, first it is necessary to understand the distortion generation mechanisms in each amplifier individually and then understand how these nonlinear phenomena interact in a Doherty arrangement.

#### A. CARRIER AND PEAKING DISTORTION ANALYSIS

Two very important characteristics of an amplifier that are recognized to assess its linearity are the Amplitude-induced amplitude variation, AM/AM, and the amplitude-induced phase variation, AM/PM, characteristics. So, it is important to study the causes of distortion in these two characteristics of a power amplifier when it is subjected to complex amplitude and phase modulation formats.

The AM/AM characteristic has been a highly regarded topic by the scientific community and for many years was considered sufficient to assess the PA intermodulation distortion (IMD) performance [31]–[34]. The performed studies were based on small-signal analysis with Volterra series and then extrapolated to large signal, commonly using Describing Functions (DF) techniques [35].

In these studies, for a static analysis, it is assumed that the output current of an active device can be described with a low order Volterra series, or its memoryless subset, the Taylor series:

$$I_{out}[v_{in}(t)] = I_{DC} + G_{m1} \cdot v_{in}(t) + G_{m2} \cdot v_{in}(t)^2 + G_{m3} \cdot v_{in}(t)^3$$

(1.3)

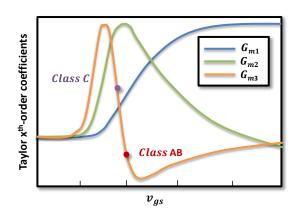

where  $v_{in}$  is the RF input voltage and the  $G_{mx}$  coefficients are the x<sup>th</sup>-order expansion coefficients of the nonlinear transconductance. In Fig. 1.7 it can be seen the typical variations of these coefficients as a function of input voltage up to the 3rd order expansion for a FET.

Fig. 1.7 – Normalized coefficients of the FET's nonlinear transconductance up to 3rd-order.

The odd coefficients of the output current expansion in Taylor series are the only ones that cause in-band distortion because these are the only ones that produce mixing-products coincident with the fundamental. Therefore, focusing only on the  $G_{m3}$  coefficient, the variations that exist on it according to the bias point determine the existing changes in the 3<sup>rd</sup> order IMD.

These analyses about the impact of the bias point on the intermodulation distortion and, consequently, in the AM/AM characteristic, help us understand and clarify the classes of operation near the threshold voltage, VT. Thus, the class B operation is defined when the transistor is biased exactly in the null of  $G_{m3}$ , which results in a minimum of the IMD3 (the so-called small-signal IMD sweet-spot). Positive values of the  $G_{m3}$  result in a gain expansion (class C behaviour), while for negative values of the  $G_{m3}$  the gain is compressive (class AB behaviour) [36].

Although these studies only address the AM/AM characteristic, they were able to predict most of PA distortion behaviour, namely the so-called IMD sweet-spots, despite neglecting the possible AM/PM conversion of the amplifier. However, in order to be able to expand this analysis to large signal, it is assumed that the large-signal distortion in a PA can be represented by Describing Functions [31], which is not always easy to perform. In addition, it is also assumed that the overall PA distortion is the sum of the small-signal response with the large-signal response, which is not always correct.

Recently, some large-signal studies have been published addressing the AM/AM as well as the AM/PM distortion in a PA [37], [38]. In these studies, it is also used a Volterra analysis but now built on top of a harmonic balance simulation. Unfortunately, as their authors did not derive any analytical model for the amplitude and phase nonlinear distortion generation mechanisms, and for their potential relationship, they were unable to connect these simulated nonlinear distortion sources to the PA measured characteristics.

#### B. DISTORTION ANALYSIS OF THE OVERALL DOHERTY AMPLIFIER

The analysis using the Taylor expansion can also be applied in the study of the nonlinear phenomena observed in the Doherty amplifier [22], [25], [26]. Actually, this is the state-of-art of the theoretical analysis of the nonlinear distortion of Doherty amplifiers.

From the studies carried out on current-mode PAs operating in small-signal, it is known that the nonlinear distortion of an active device is strongly dependent on the bias point, i.e. the operation class. Thus, as the main amplifier is normally biased in a class AB regime, i.e. a negative  $G_{m3}$ , it exhibits a gain compression characteristic over the entire range of input power. On the other hand, the auxiliary amplifier is normally biased in a class C regime, i.e. a positive  $G_{m3}$ . So, it exhibits a gain expansion characteristic for low levels of input voltage. Therefore, by adding up these distinct nonlinear behaviours, namely a positive and negative  $G_{m3}$ , it is possible to cancel the IMD3 of the whole Doherty amplifier and, consequently, producing an amplifier with a gain characteristic much more flat [21].

Once again, the previous study neglected possible AM/PM conversions of the amplifiers and how they affect the nonlinear load modulation. Moreover, as mentioned in the Background and Motivation, the issues of reducing energy consumption in base stations lead the PA's designers to design amplifiers focusing predominantly on the efficiency performance and, consequently, the amplifiers will operate close to saturation. Unfortunately, this prevents the cancellation of the nonlinear distortion generation mechanism based on the main and auxiliary amplifiers producing a strongly nonlinear behaviour, which fails the strict wireless communication standards. In order to solve this, the industry usually uses digital pre-distortion techniques but not always successfully. Thus, it is very important to know why the digital pre-distortion fails and the only way to do that is to fully understand the nonlinear distortion generation mechanisms of a Doherty amplifier. This is precisely the main objective of this PhD Thesis.

#### 1.2.3 Efficiency Enhancement Techniques in the Doherty Amplifier

Since the introduction of the Doherty amplifier, the wireless communication signals have constantly evolved to keep up with the strong demand for higher transmission rates and fulfil the strict spectral masks. Naturally, both the scientific and the industrial communities have been putting efforts in the design of Doherty amplifiers even more efficient than the classical one, as well as in the development of techniques to improve their linearizability. This section is dedicated to the new efficiency and linearizability

enhancement techniques that are applied to the Doherty amplifiers to accommodate the modern wireless communication signals.

A classic Doherty with one auxiliary amplifier can produce two peaks of efficiency, one at the maximum input power and another one at 6 dB below this point. However, the new wireless communication signals have a PAPR higher than this value, sometimes as high as 12dB. Therefore, to solve this problem, a new topology appeared in the literature, the so-called N-Way Doherty [21], [39], which uses more than one auxiliary amplifier. Fig. 1.8 illustrates this topology of the Doherty amplifier as well as the efficiency characteristic as a function of the auxiliary amplifiers that are used.

Fig. 1.8 – N-Way Doherty Amplifier: a) N-Way block diagram; b) N-Way efficiency characteristic and the PDF of a W-CDMA signal with 10 dB of PAPR.

In Fig. 1.8 b) it is possible to see the improvement of the average efficiency using the N-Way Doherty arrangement. For example, the 3-Way Doherty has the first maximum peak exactly at the maximum peak of the probability distribution function (PDF) of a W-CDMA signal with 10 dB of PAPR. However, with the increase of the number of auxiliary amplifiers, the efficiency between the two peaks will be increasingly degraded. Therefore, an alternative topology has been considered, the N-Stage Doherty amplifier [22]–[24], [40], [41].

In the literature, there are two different arrangements of the three-stage Doherty amplifier as shown in Fig. 1.9. In the first one, the carrier amplifier has the structure of a Doherty amplifier and the other auxiliary amplifier modulates its load. In the second one, it is used a Doherty amplifier to modulate the load of a single-ended carrier amplifier. In these topologies the auxiliary amplifiers are turned on sequentially allowing three peaks on the efficiency characteristic, as show in Fig. 1.9 c). Although both three-stage topologies present the same efficiency characteristic, the first one requires an active power splitter due to earlier carrier PA current saturation and so, the second one seems to be preferred because it presents a better linearity performance [22],[42].

Fig. 1.9 – Three-Stage Doherty Amplifier: a) and b) different types of a Three-Stage arrangements; c) Three-Stage efficiency characteristic and the PDF of a W-CDMA signal with 10 dB of PAPR

Unfortunately, although the theoretical calculations of the Doherty PA efficiency for all above arrangements predict that the efficiency peak at back-off is equal to the one obtained at full-power, in practical Doherty implementations the efficiency peaks vary with the back-off power level. It is observed that efficiency starts to increase as the back-off level is increased and then there is an efficiency degradation for higher back-off levels. In an attempt to explain this efficiency dependency on the back-off power levels, some transistor models with artificial series and parallel losses have been presented [43], [44].

The series losses are used to describe the initial efficiency increase with the backoff and the parallel losses are used to justify the efficiency degradation for higher back-off

levels. However, although the series losses can have a physical support in the FET's

channel resistance,  $R_{on}$ , the model with parallel losses does not have a physical meaning

since the device package is almost purely reactive. Therefore, a physically consistent

efficiency model capable of predicting the efficiency dependency on the back-off power

levels, namely the efficiency degradation, would be helpful to optimize the Doherty power

amplifier design.

In addition, all the Doherty arrangement topologies most often use the auxiliary amplifiers in class C regime so that they come into conduction only for large signal.

However, as it is known, a class C amplifier has a soft turn on as well as a lower current gain. These nonlinear phenomena will produce an imperfect load modulation causing a nonlinear behaviour in the Doherty amplifier. To solve these problems, in the literature there were proposed some approaches, such as the use of an unequal power divider at the input [45], [46], different transistor peripheries [47]–[50], asymmetrical drain voltages [51], [52] or more complicated solutions such as using drivers before the main and auxiliary amplifiers [53], [54], changing the gate bias digitally [40], [55], [56] and independent paths for the main and auxiliary amplifiers [57], [58].

In addition to the efficiency and linearizability enhancement techniques applied to the Doherty amplifier [56], [59], [60], the digital pre-distortion (DPD) techniques are indispensable to fulfil the strict linearity requirements imposed by the wireless communication operators. Unfortunately, as previously mentioned, these linearization schemes are not always successful, mainly because the PA designers usually attribute more weight to the efficiency enhancement when designing the Doherty PAs. Moreover, as the nonlinear distortion generation mechanisms of the Doherty PA are not yet fully understood, when the DPD techniques fail, the PA designers do not know how to improve the linearity of their Doherty PAs. Thus, it is essential to increase the knowledge of the nonlinear distortion mechanisms of the Doherty, so that it is possible to develop new PA design methodologies that improve the efficiency without compromising the linearity. This is precisely the main objective of this PhD Thesis.

# 1.3. Objectives and Thesis' Organization

As mentioned in the Background and Motivation, the scientific and industrial communities have been putting significant efforts in obtaining power amplifiers with higher efficiency, higher linearity and higher bandwidth. At the moment, the approach that is usually taken consists in the design of power amplifiers optimized for efficiency in a wide bandwidth (often they are designed for multi-bands) and then use digital pre-distortion techniques in order to fulfil the stringent spectral masks.

The problem with this philosophy of efficiency maximization is that, as the linearization schemes are chosen following a purely heuristic approach [27]–[30], there is only a moderate probability of success. Therefore, it is necessary to change this approach and return to the theoretical foundations based on the mathematical modelling of circuits.