Flávio Carlos da Silva

**Rodrigues Silvestre**

Detetor Digital Síncrono de Sinal CW Baseado em FPGA

## Flávio Carlos da Silva Rodrigues Silvestre

# Detetor Digital Síncrono de Sinal CW Baseado em FPGA

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia Electrónica e Telecomunicações, realizada sob a orientação científica do Doutor Armando Carlos Domingues da Rocha e do Doutor Arnaldo Silva Rodrigues de Oliveira, Professores do Departamento de Electrónica e Telecomunicações e Informática da Universidade de Aveiro

## o júri / the jury

presidente / president Professor Doutor Tomás António Mendes Oliveira e Silva

Professor Associado da Universidade de Aveiro

**G**

Professor Doutor Armando Carlos Domingues da Rocha

Professor Auxiliar da Universidade de Aveiro (Orientador)

**Professor Doutor Arnaldo Silva Rodrigues de Oliveira** Professor Auxiliar da Universidade de Aveiro (Co-orientador)

#### Palavras-chave

#### Resumo

Recetor Digital, Propagação de Microondas, Medição de Balizas, Comunicações por Satélite, Rádio definido por Software, Phase Locked Loop.

A propagação de sinais acima de 10 GHz na atmosfera sofre de atenuação e despolarização devido à presença de hidrometeoros. A caracterização e o modelamento destas contrariedades exige longas campanhas de medição as quais são efectuados usando receptores dedicados que monitorizam o sinal CW de elevada pureza espectral radiado por satélites geo-estacionário.

Os sinais a medir são habitualmente dois, o denominado copolar (recebido com polarização original) e o crosspolar (polarização ortogonal). A medição da amplitude permite obter a magnitude de atenuação atmosférica, a qual é importante para saber durante quanto tempo do ano uma ligação de satélite estará indisponível.

A medição do tipo de sinais aqui pretendido é sempre problemático pois o sinal recebido apresenta um valor de CNR muito reduzido, algum espalhamento espectral e deriva de frequência. Os métodos de deteção coerente por PLL ou FLL são preferidos neste tipo de aplicações e apresentam uma gama dinâmica superior mas por outro lado a sua implementação no domínio analógico pode ser bastante díficil.

De modo a contornar a inflexibilidade dos métodos analógicos recorreu-se ao conceito de Software Defined Radio (SDR) que procura tratar os sinais de rádio, tanto quanto possível, no domínio digital. Deste modo resultou a ideia para o trabalho desta dissertação, que consistiu na elaboração de um pequeno módulo capaz de detectar digitalmente o sinal proveniente de satélite a uma frequência intermédia (IF) e com recurso a uma FPGA, adicionalmente os resultados da detecção são enviados para um computador hospedeiro.

Com vista à conceptualização do projecto é feita uma caracterização do sinal a detectar e são apresentados alguns métodos de detecção dando-se enfâse aos que fazem uso de malhas de sincronização. Seguidamente é feita uma descrição da placa de conversão analógico-digital construída e da arquitectura do detector síncrono realizado na FPGA: etapas de filtragem, decimação e especificação dos parâmetros de loop. É ainda descrito o processo de transferência de dados para o PC via controlador USB.

Por fim alguns resultados utilizando um gerador RF para sintetizar o sinal de entrada são apresentados e analisados. Foi concluído que o detector adquire o sincronismo para sinais acima de -60 dBm, o que apesar de ser uma situação onde o ruído é muito reduzido, deixa boas indicações para testes efetuados em ambiente real.

## Keywords

#### **Abstract**

Digital Receiver, Characterization of Earth-Satellite propagation channel, CW Signal, Satellite Communications, Software Defined Radio, Phase Locked Loop.

Earth-Satellite propagation channel modeling requires extensive measurement campaigns at as many sites, frequencies and link parameters as possible. The campaigns are made by estimating the received amplitude of a beacon CW signal radiated from a satellite using beacon receivers.

The receiver measures the signal with the same polarization as the radiated one (copolar) and often the orthogonal (crosspolar) that carries additional information on the channel. As the carrier to noise ratio (CNR) is low a coherent detection is often used and requires the use of tracking loops whose implementation in the analogue domain is harsh.

The use of digital radio hardware and/or software defined radio techniques to handle the tracking and detection is now being used: the down conversion is made within a FPGA, processed, and the data is moved to a host computer for further software processing.

A stand-alone detector unit combining the frequency down conversion and detection in a single board and delivering the Cartesian two channel detected amplitudes to a host PC is described. The advantages would be a general purpose board that could handle, with no more hardware or software developments, measurement of beacon signals in a wide IF input range making also easier the analogue design of the preceding beacon receiver hardware.

Some preliminar results of the developed detector with a clean signal provided by a waveform generator are presented and analysed. It was concluded that the detector can achieve lock with signals as low as -60 dBm in absense of phase noise, which leaves good indications to a real world detection scenario.

The dissertation ends with some ideas for improvement and future work such as the utilization of frequency locked loops.

# Conteúdo

| $\mathbf{C}$ | onteí | ido                                                 | j        |

|--------------|-------|-----------------------------------------------------|----------|

| Li           | sta d | le Figuras                                          | v        |

| Li           | sta d | le Tabelas                                          | vii      |

| A            | cróni | mos                                                 | ix       |

| 1            | Intr  | rodução                                             | 1        |

|              | 1.1   | Enquadramento                                       | 1        |

|              | 1.2   | Motivação                                           | 1        |

|              | 1.3   | Objetivos                                           | 2        |

|              | 1.4   | Estrutura da dissertação                            | 3        |

| 2            | Con   | aceitos Fundamentais                                | 5        |

|              | 2.1   | Introdução                                          | 5        |

|              | 2.2   | Caracterização do sinal a detectar                  | 5        |

|              |       | 2.2.1 EIRP                                          | 5        |

|              |       | 2.2.2 Bloco Analógico                               | 6        |

|              |       | 2.2.2.1 CNR - Link Budget                           | 7        |

|              | 2.3   | Métodos de deteção                                  | 8        |

|              |       | 2.3.1 Detecção no domínio do tempo                  | 8        |

|              |       | 2.3.2 Deteção no domínio da frequência              | 9        |

|              | 0.4   | 2.3.3 Deteção síncrona usando malhas de sincronismo | 10       |

|              | 2.4   | Malhas de sincronização - PLL                       | 10       |

|              |       | 2.4.0.1 Detetor de rase                             | 11<br>11 |

|              |       | 2.4.0.3 VCO                                         | 12       |

|              |       | 2.4.0.4 Função Transferência                        | 12       |

|              |       | 2.4.0.5 Largura de Banda de ruído                   | 13       |

|              |       | 2.4.0.6 Potência de ruído                           | 14       |

|              |       | 2.4.0.7 Manutenção e aquisição de sincronismo       | 15       |

|              |       | 2.4.1 PLL: Simulação em Simulink                    | 15       |

|              | 2.5   | Sumário                                             | 17       |

| 3            | Plat  | taforma de Hardware do Detetor                      | 19       |

| •            | 3.1   | Introdução                                          | 19       |

|              | 3.2   | Field Programmable Gate Arrays (FPGA's)             | 19       |

|              |       | 3.2.1 Comparação entre FPGAs e DSPs                 | 20       |

|              | 3.3   | Módulo FPGA                                         | 20       |

|              |       | 3.3.1 Trenz Electronic TE0320-EVO2B                 | 22       |

|              | 3.4   | ADC - AD9248                                        | 23       |

|              | 3.5   | Arquitectura do Detetor e Aspecto Físico            | 25       |

| 4            | $\mathbf{Arq}$ | uitectura do detetor síncrono             | 27         |

|--------------|----------------|-------------------------------------------|------------|

|              | 4.1            | Introdução                                | 27         |

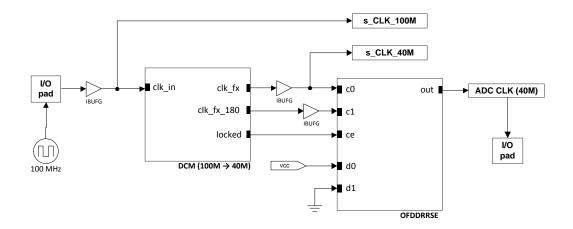

|              | 4.2            | Domínios de clock                         | 27         |

|              |                | 4.2.1 Síntese do clock para ADC           | 28         |

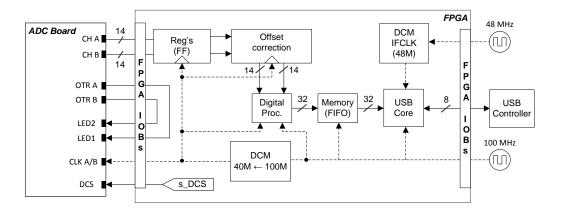

|              | 4.3            | Interface com ADC e Computador Hospedeiro | 29         |

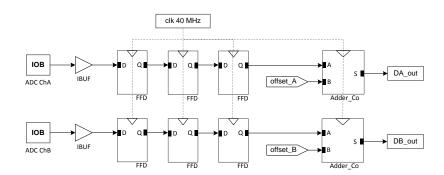

|              |                | 4.3.1 Entrada de Dados da ADC             | 29         |

|              | 4.4            | PLL digital                               | 30         |

|              | 1.1            | 4.4.1 NCO                                 | 32         |

|              |                | 4.4.2 Detetor de fase (Multiplicadores)   | 32         |

|              |                | 4.4.3 FIFOS de Interface                  | 33         |

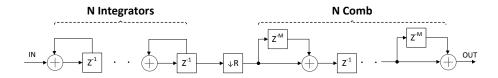

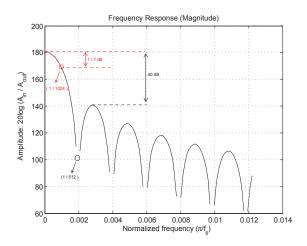

|              |                | 4.4.4 Filtros CIC                         | 33         |

|              |                | 4.4.5 FIR (Primário)                      | 35         |

|              |                |                                           | 36         |

|              | 4 5            | 4.4.6 FFT                                 | 39         |

|              | 4.5            | <u> -</u>                                 |            |

|              | 1.0            | 4.5.1 Filtro de malha                     | 40         |

|              | 4.6            | Canal Crosspolar                          | 44         |

| 5            | Con            | nunicação via USB                         | 45         |

| -            | 5.1            | Introdução                                | 45         |

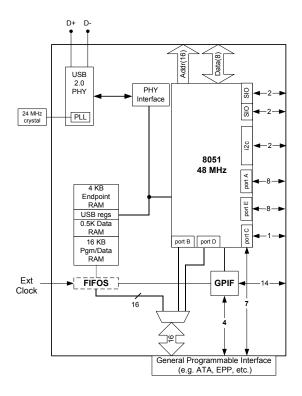

|              | 5.2            | Estrutura geral do controlador USB (Fx2)  | 46         |

|              | ٠              | 5.2.1 Configuração via Firmware           | 47         |

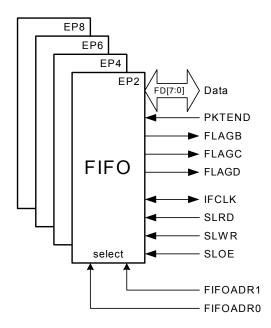

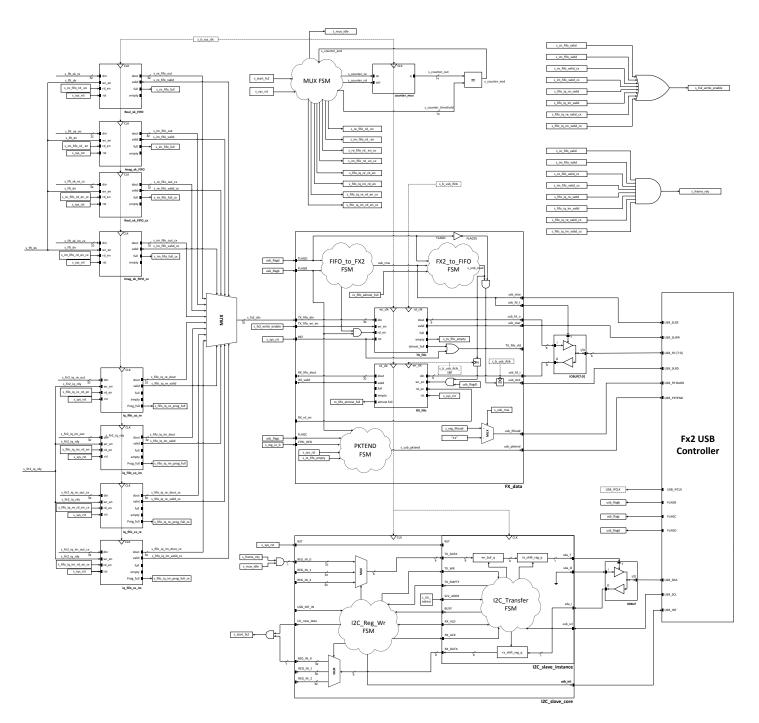

|              |                | 5.2.2 Interface Slave FIFOs               | 48         |

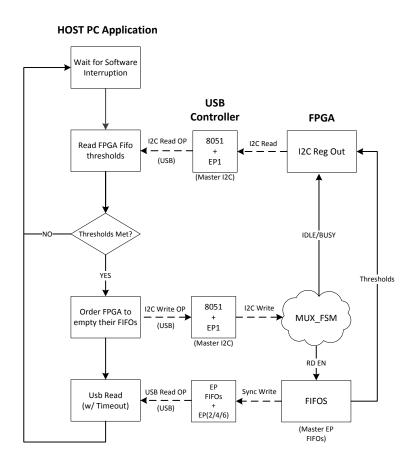

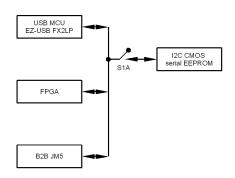

|              |                | 5.2.3 Interface I2C                       | 49         |

|              | 5.3            | Implementação                             | 49         |

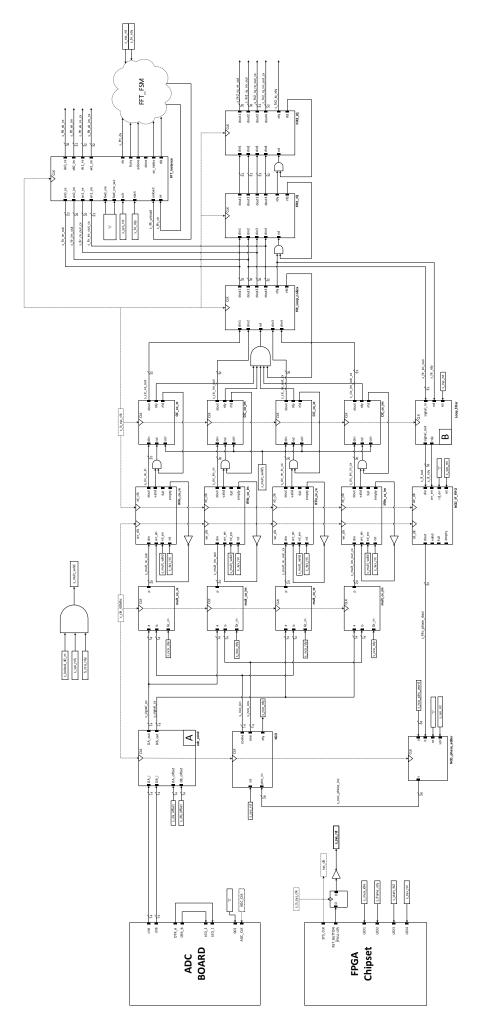

|              | 5.4            | Multiplexagem dos FIFOS da FPGA           | 50         |

|              | 5.5            | Core USB                                  | 51         |

|              | 0.0            |                                           | -          |

| 6            | Test           | tes e Resultados                          | <b>5</b> 3 |

|              | 6.1            | Introdução                                | 53         |

|              | 6.2            | Resultados usando sinal sintético         | 53         |

|              | 6.3            | Testes com gerador RF                     | 54         |

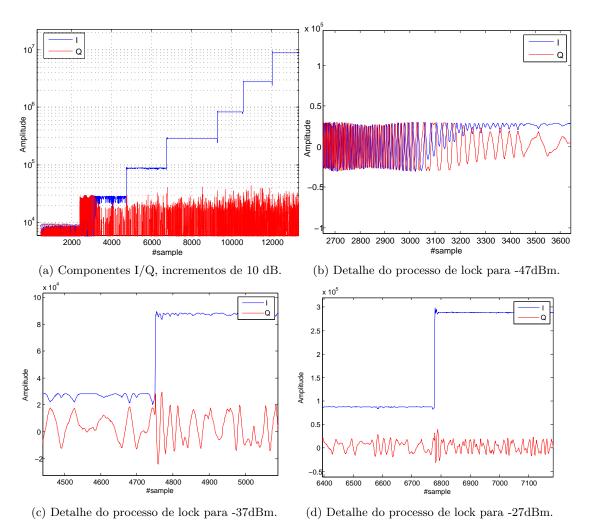

|              |                | 6.3.1 Análise do período de pré aquisição | 57         |

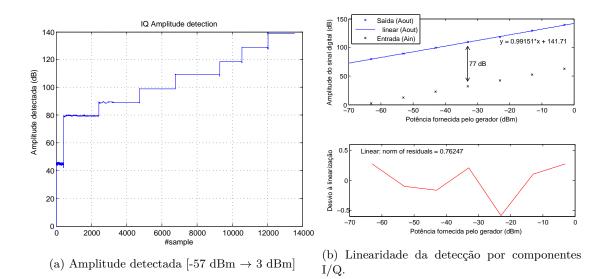

|              |                | 6.3.2 Deteção por componentes I/Q         | 58         |

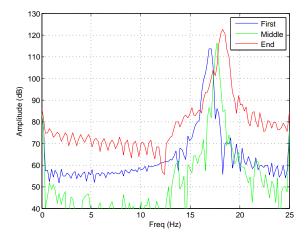

|              |                | 6.3.3 Deteção por FFT                     | 59         |

|              |                | 6.3.4 ADC                                 | 60         |

|              | 6.4            |                                           | 60         |

|              |                |                                           |            |

| 7            | Con            | nclusões e trabalho futuro                | 61         |

|              | 7.1            | Conclusões                                | 61         |

|              | 7.2            | Trabalho futuro                           | 61         |

|              | ^ 1            | ,                                         | 00         |

| A            | pênd           | ices                                      | 63         |

| $\mathbf{A}$ | Plac           | ca de conversão analógico-digital         | 64         |

| В            | Sigt           | ema sintetizado em FPGA                   | 67         |

| _            |                | Ocupação de recursos                      | 70         |

|              |                | Xilinx IP Cores: Configuração             | 71         |

|              |                |                                           |            |

| $\mathbf{C}$ | TEO            | 0320: Configuração                        | 81         |

|              | C.1            | Controlador USB Fx2 - Drivers/Firmware    | 81         |

|              | $C_{2}$        | Programação da SPI PROM                   | 81         |

| D            | Setup do ambiente de desenvolvimento de Software                                              | 83 |

|--------------|-----------------------------------------------------------------------------------------------|----|

|              | D.1 Nokia Qt Framework                                                                        | 83 |

|              | D.2 Instruções para instalação da biblioteca $qwt$                                            | 83 |

|              | $\mathrm{D.3}~\mathrm{Parâmetros}$ de compilação/linkagem para o uso de QT em ambiente MSVC10 | 83 |

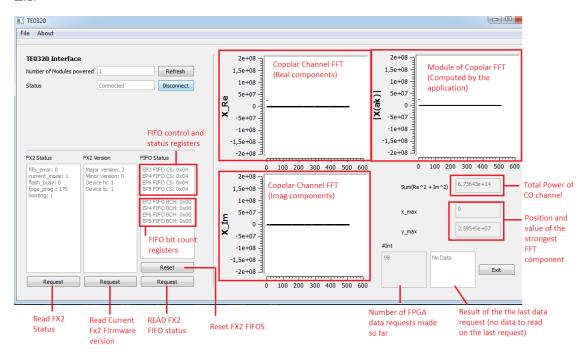

| $\mathbf{E}$ | Aplicação de interface com a FPGA                                                             | 84 |

| Bi           | ibliografia                                                                                   | 85 |

# Lista de Figuras

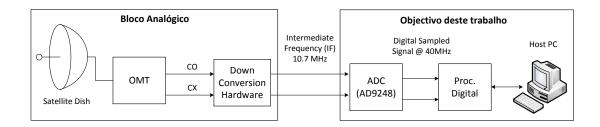

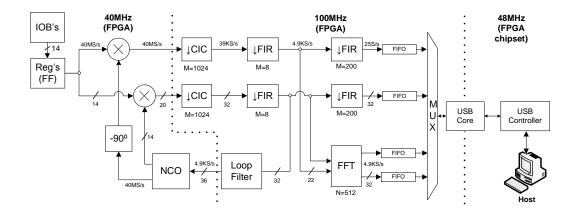

| 2.1  | Arquitectura geral do detector síncrono baseado em FPGA                       | Ę  |

|------|-------------------------------------------------------------------------------|----|

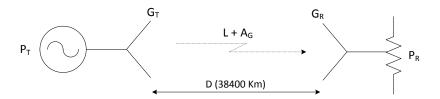

| 2.2  | Power Budget: conjunto emissor-receptor                                       | 6  |

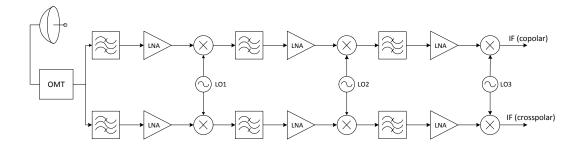

| 2.3  | Conversão do sinal recebido para a frequência IF                              | 7  |

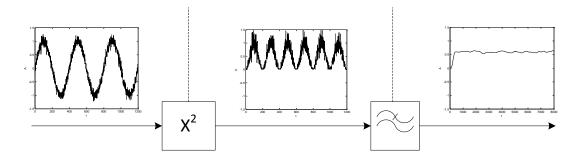

| 2.4  | Detecção no tempo via quadrador e filtro passa-baixo                          | E  |

| 2.5  | Diagrama de blocos genérico de uma PLL                                        | 10 |

| 2.6  | Comparação entre a saída do detector de fase ideal e um multiplicador         | 11 |

| 2.7  | Filtro de malha de 2ª ordem com integrador e correcção de avanço de fase      | 12 |

| 2.8  | Diagrama de blocos da PLL no domínio de Laplace.                              | 13 |

| 2.9  | Diagrama de Bode da PLL com filtro de malha ativo de 2ª ordem                 | 14 |

| 2.10 | Largura de banda de ruído da PLL em função do coeficiente de amortecimento    | 15 |

| 2.11 | 3                                                                             | 16 |

|      | Simulações com variação de CNR                                                | 18 |

|      | Simulações com variação do desvio de frequência                               | 18 |

|      | Simulações com variação da largura de banda de ruído.                         | 18 |

| 2.15 | Espectro do sinal de entrada simulado, com adição de ruído                    | 18 |

| 3.1  | FPGA: Arquitectura em forma de matriz                                         | 20 |

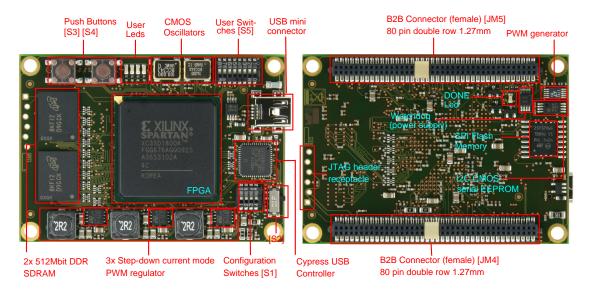

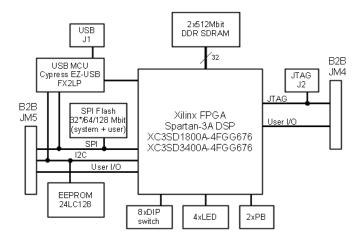

| 3.2  | Módulo TE0320-EVO2 (Trenz Electronic) e identificação de elementos. [Ele13a]  | 23 |

| 3.3  | Diagrama de Blocos do módulo TE0320 da Trenz Electronic. [Ele13b]             | 23 |

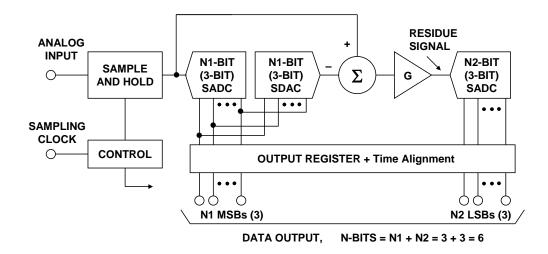

| 3.4  | Arquitectura geral de uma ADC pipelined                                       | 24 |

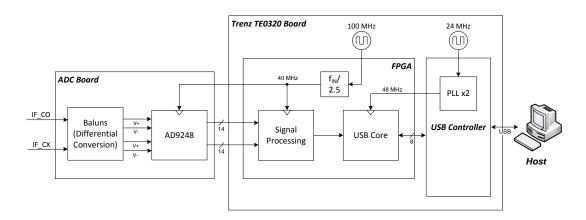

| 3.5  | Diagrama de blocos do hardware utilizado para a detecção do sinal IF          | 25 |

| 3.6  | Placa de conversão analógico-digital                                          | 25 |

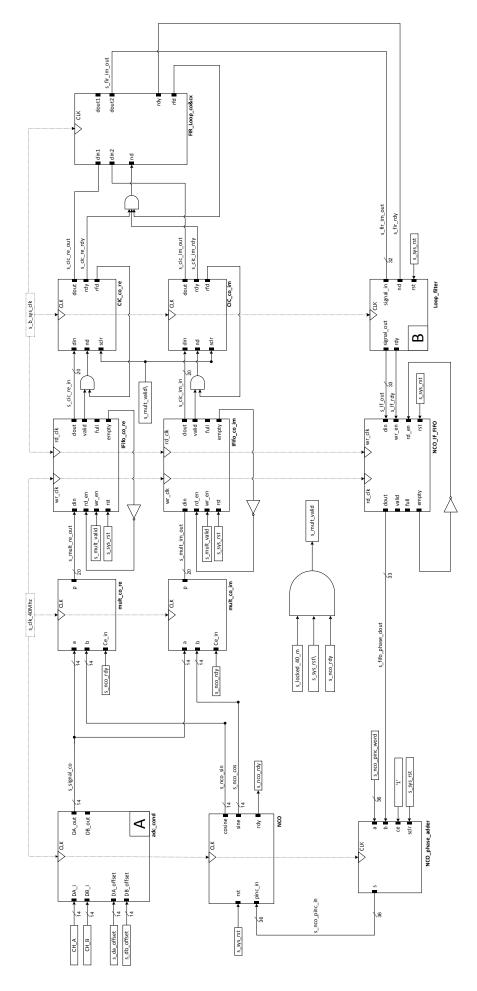

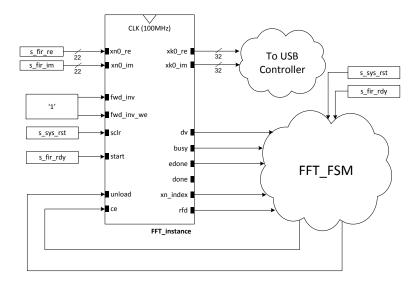

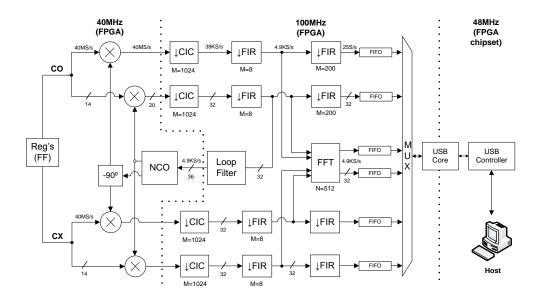

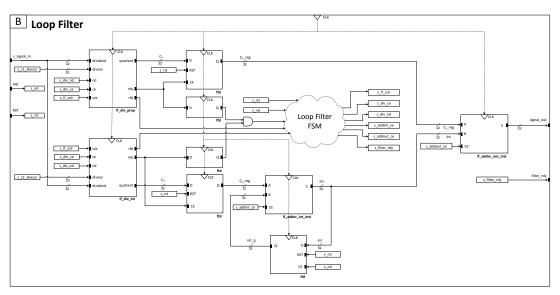

| 4.1  | Diagrama de blocos do detector síncrono para um canal                         | 28 |

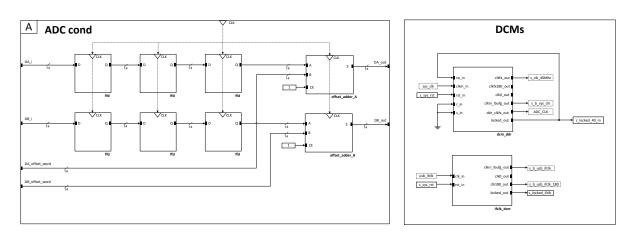

| 4.2  | DCMs sintetizados, sinais e respectivas ligações                              | 29 |

| 4.3  | Sinais de interface ADC-FPGA                                                  | 30 |

| 4.4  | Sincronismo do sinal de entrada e correção do offset da ADC                   | 30 |

| 4.5  | Diagrama de blocos da PLL digital sintetizada em VHDL                         | 31 |

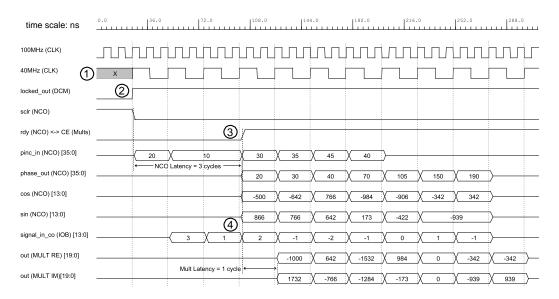

| 4.6  | Diagrama temporal: DCM(40MHz), NCO, multiplicador                             | 33 |

| 4.7  | Esquema de um filtro CIC decimador de factor R                                | 34 |

| 4.8  | Resposta em magnitude do filtro CIC implementado. (R=1024, N=3, M=1)          | 34 |

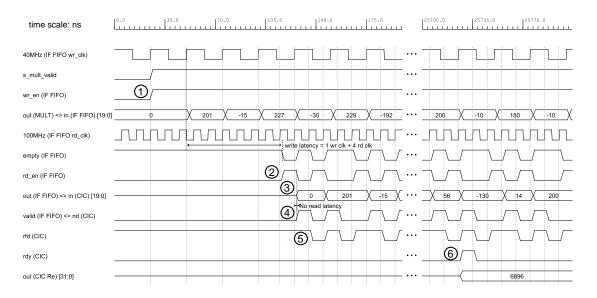

| 4.9  | Diagrama temporal: Interface multiplicador/filtros CIC                        | 35 |

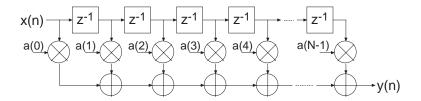

|      | Implementação de filtros FIR com linha de atraso. [Xil12]                     | 36 |

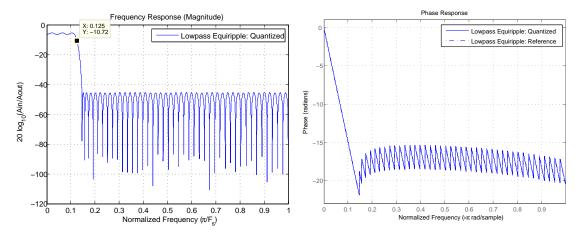

|      | Filtro FIR (primário), resposta em amplitude e fase                           | 36 |

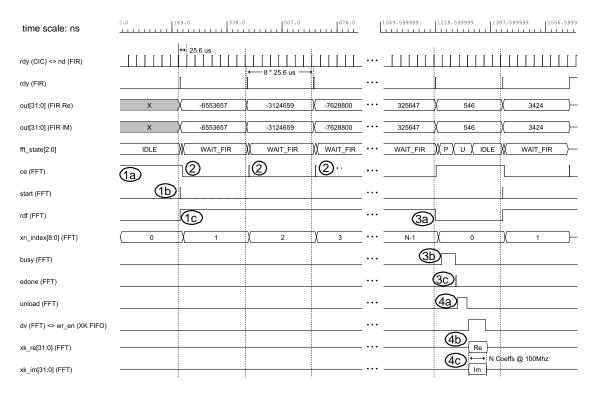

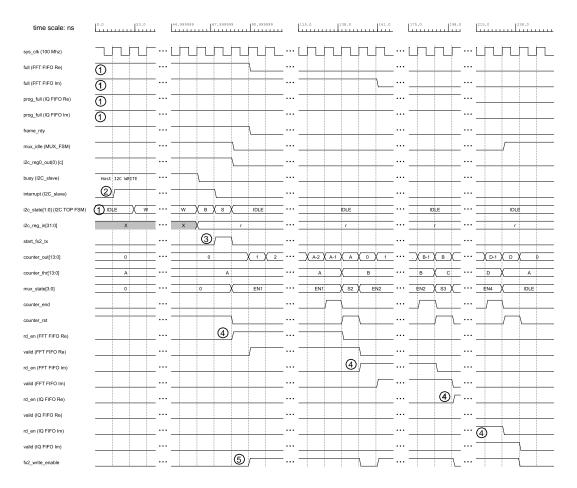

|      | Diagrama temporal: Interface entre FIR Filter e FFT                           | 38 |

|      | Interface do bloco FFT                                                        | 38 |

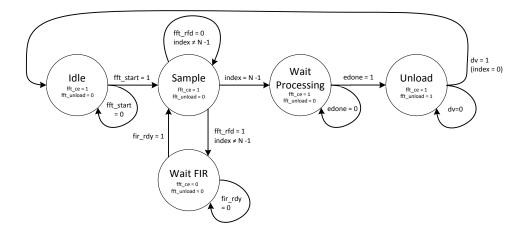

|      | Diagrama de transições da máquina de estados implementada para o FFT IP core. | 39 |

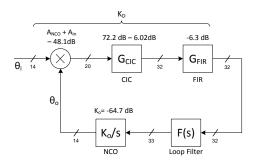

|      | PLL digital em FPGA: Ganhos                                                   | 41 |

|      | Diagrama de blocos simplificado - Filtro de malha PLL                         | 41 |

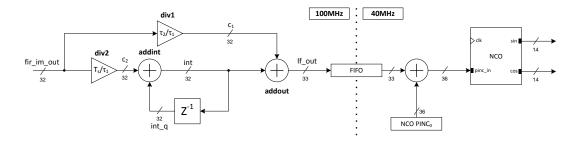

|      | Filtro de Malha, diagrama de blocos e de ligações                             | 42 |

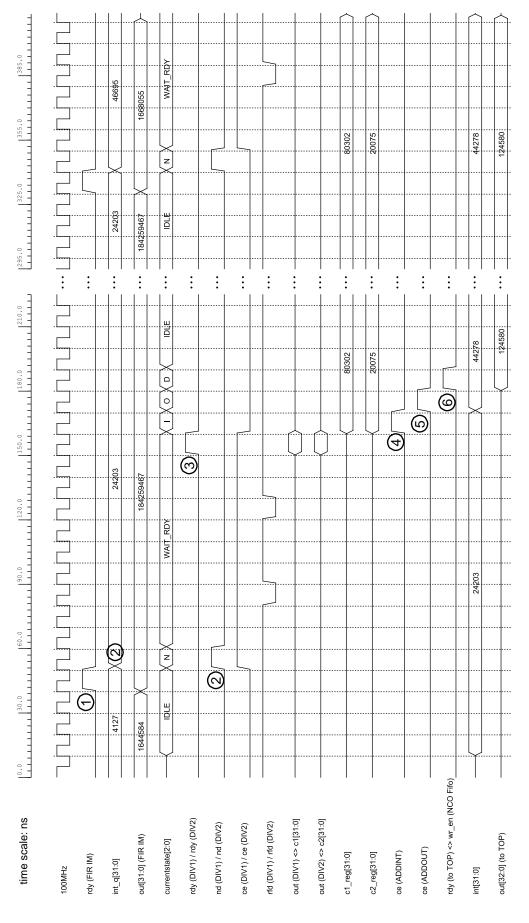

|      | Diagrama temporal: Filtro de malha, processamento de uma amostra              | 43 |

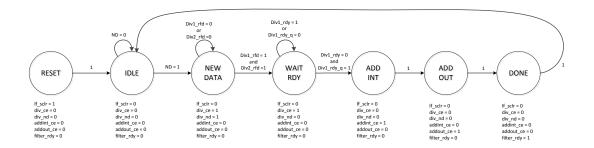

| 4.19 | Filtro de Malha, diagrama de transições da máquina de estados                 | 44 |

| 4.20       | Diagrama de blocos geral do sistema, inclusão do canal crosspolar                                                                                            | 44 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

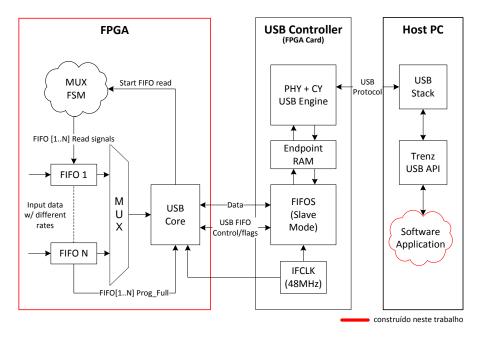

| 5.1        | Esquema geral da comunicação FPGA $\leftrightarrow$ computador hospedeiro                                                                                    | 45 |

| 5.2<br>5.3 | Diagrama interno do controlador USB Cypress Ez-USB Fx2. [Sem12] FIFOs Internos do controlador Fx2 + sinais de interface para configuração em Slave           | 47 |

|            | Mode                                                                                                                                                         | 49 |

| 5.4        | Diagrama de comunicações: Computador hospedeiro $\leftrightarrow$ FPGA                                                                                       | 50 |

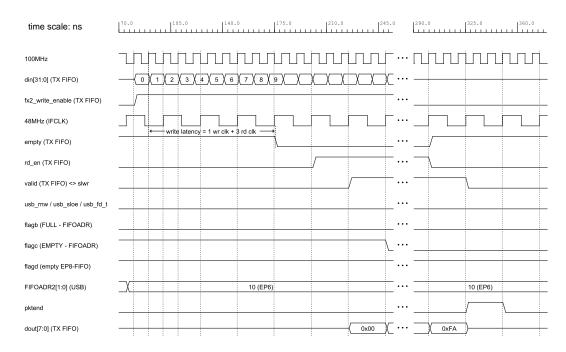

| 5.5        | Diagrama temporal: multiplexagem dos FIFOs de armazenamento                                                                                                  | 51 |

| 5.6        | Diagrama temporal: Transmissão de dados para os Slave Fifos do controlador USB.                                                                              | 52 |

| 6.1        | Testes com sinal sintetico armazenado na FPGA                                                                                                                | 54 |

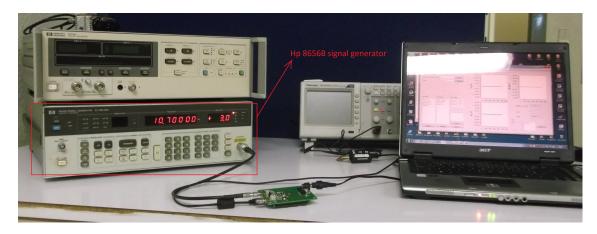

| 6.2        | Equipamento envolvido nos testes de laboratório                                                                                                              | 54 |

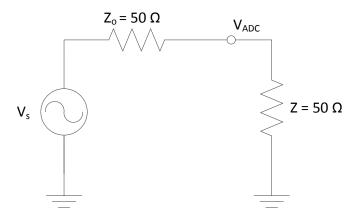

| 6.3        | Circuito ilustrativo para cálculo da potência entregue à ADC                                                                                                 | 55 |

| 6.4        | Resultados obtidos com o gerador de RF                                                                                                                       | 56 |

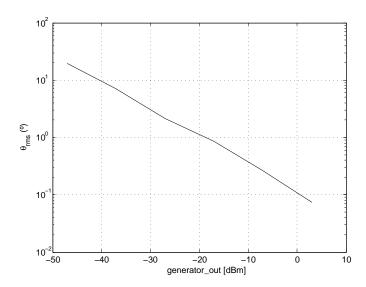

| 6.5        | Valor quadrático médio da variância de fase à saída do detector síncrono                                                                                     | 57 |

| 6.6        | Evolução do espectro na aquisição de sincronismo.                                                                                                            | 58 |

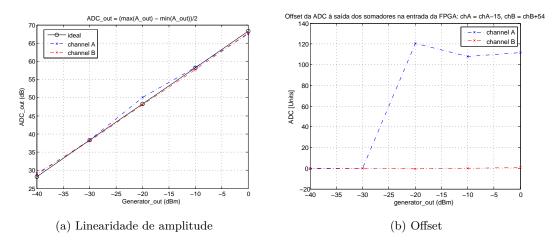

| 6.9        | Teste efetuados à saída dos dois canais do AD9248                                                                                                            | 60 |

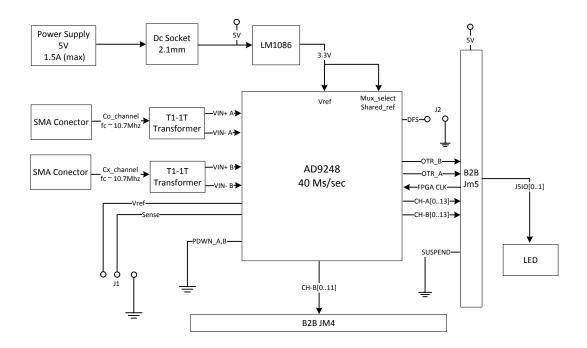

| A.1        | Diagrama de blocos da placa de conversão analógica                                                                                                           | 65 |

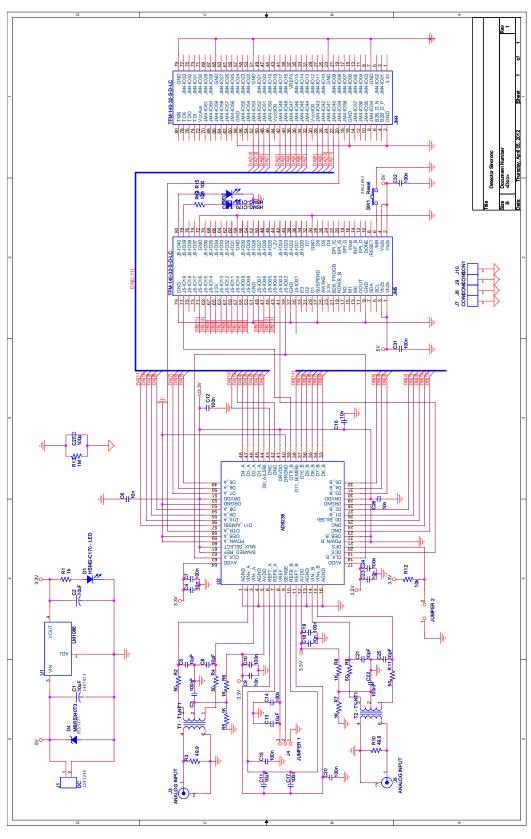

| A.2        | Esquemático: ADC Printed Circuit Board                                                                                                                       | 66 |

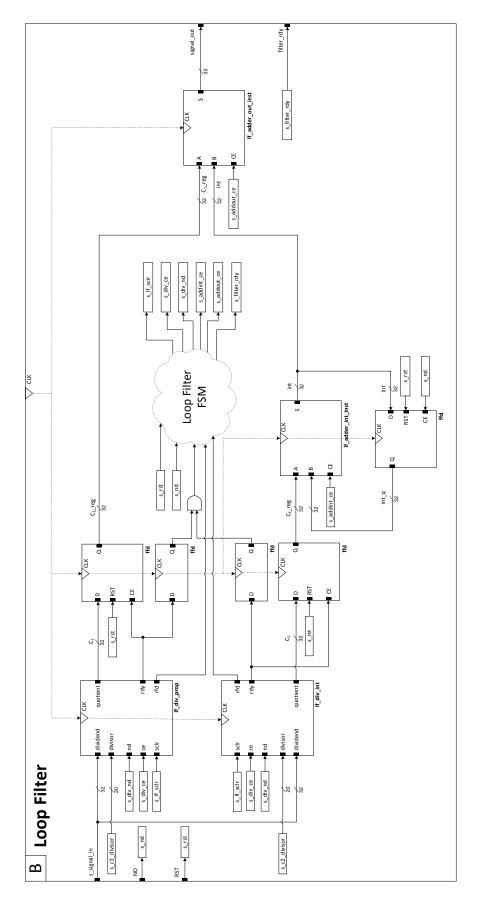

| B.1<br>B.2 | FPGA: Bloco de entrada do sinal da ADC (ADC_cond), DCMs e filtro de malha FPGA: Interface com a placa de ADCs e o chipset, PLL digital, bloco FFT, filtragem | 67 |

|            | das componentes I/Q                                                                                                                                          | 68 |

| В.3        | FPGA: Fifos de armazenamento, Fx2 Core, I2C core, respectivas máquinas de es-                                                                                |    |

|            | tados e interface com o controlador USB.                                                                                                                     | 69 |

| B.4        | Distribuição dos recursos da FPGA                                                                                                                            | 70 |

| B.5        | Distribuição dos recursos da FPGA                                                                                                                            | 71 |

| C.1        |                                                                                                                                                              | 82 |

| E.1        | Screenshot da aplicação desenvolvida                                                                                                                         | 84 |

# Lista de Tabelas

| 1.1        | Bandas de Frequência utilizadas para serviços de Satélite. Adaptado de [BC07]                                      | 2        |

|------------|--------------------------------------------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | Alphasat I-XL beacon: Características esperadas                                                                    | 6<br>8   |

| 3.1<br>3.2 | Vantagens e desvantagens entre FPGA e DSP                                                                          | 21<br>22 |

| 4.1        | Dimensionamento da PLL efetuada para uma amplitude do sinal de entrada de 8191 (valor máximo para a ADC utilizada) | 40       |

| 5.1        | Configuração dos end<br>points do controlador USB Fx2 via firmware                                                 | 48       |

| A.1        | ADC configuração (J1)                                                                                              | 64       |

| A.2        | Configuração ADC (J2)                                                                                              | 64       |

| A.3        | Configuração ADC (Hardwired)                                                                                       | 65       |

| В.1        | Xilinx Clocking Wizard Clock - Forwarding/Board Deskew                                                             | 71       |

| B.2        | Xilinx Clocking Wizard - Single DCM_SP                                                                             | 72       |

| B.3        | Xilinx Core Generator - DDS Generator (NCO)                                                                        | 72       |

| B.4        | Xilinx Core Generator - PD Multiplier                                                                              | 73       |

| B.5        | Xilinx Core Generator - Interface FIFOs                                                                            | 73       |

| B.6        | Xilinx Core Generator - CIC Filter                                                                                 | 74       |

| B.7        | Xilinx Core Generator - Loop FIR                                                                                   | 74       |

| B.8        | Xilinx Core Generator - FF $\hat{T}$                                                                               | 75       |

| B.9        | Xilinx Core Generator - Binary Counter                                                                             | 75       |

|            | Xilinx Core Generator - Loop Filter Dividers                                                                       | 75       |

|            | Xilinx Core Generator - Loop Filter Adder Int                                                                      | 76       |

| B.12       | Xilinx Core Generator - Loop Filter Adder Out                                                                      | 76       |

| B.13       | Xilinx Core Generator - NCO phase Adder                                                                            | 76       |

| B.14       | Xilinx Core Generator - NCO FIFO                                                                                   | 77       |

|            | Xilinx Core Generator - IQ FIR1                                                                                    | 77       |

|            | Xilinx Core Generator - IQ FIR2                                                                                    | 78       |

|            | Xilinx Core Generator - IQ FIFOs                                                                                   | 78       |

|            | Xilinx Core Generator - FFT FIFOs                                                                                  | 79       |

|            | Xilinx Core Generator - FX2_Core TX FIFO                                                                           | 79       |

| B.20       | Xilinx Core Generator - FX2_Core RX FIFO                                                                           | 80       |

# Acrónimos

**ADC** Analog to Digital Converter

**AFC** Automatic Frequency Control

AGC Automatic Gain Control

API Application Programmable Interface

**AWGN** Additive White Gaussian Noise

B2B Board to Board

CIC Cascaded Integrator Comb

**CLBs** Configurable Logic Blocks

CMOS Complementary Metal-Oxide-Semiconductor

**CNR** Carrier to Noise Ratio

**CPU** Central Processing Unit

**CW** Continuous Waveform

DC Direct Current

**DCM** Digital Clock Manager

**DDR** Double Data Register

**DDS** Direct Digital Synthesizer

**DRSP** Digital Receiver Signal Processor

**DSP** Digital Signal Processor

**EEPROM** Erasable Programmable Read-Only Memory

**EIRP** Equivalent Isotropically Radiated Power

**ESA** European Space Agency

**FFT** Fast Fourier Transform

**FIFO** First In First Out

FIR Finite Impulse Response

**FLL** Frequency Locked Loop

FPGA Field Programmable Gate Array

**FSM** Finite State Machine

GPIF General Programmable InterFaceHDL Hardware Description Language

I/O Input/Output

IC Integrated Circuit

**IEEE** Institute of Electrical and Electronics Engineers

IF Intermediate FrequencyIIR Infinite Impulse Response

IOB Input/Output Blocks

IP Intellectual property

ITU International Telecommunication Union

LED Light Emitting Diode

LOW Noise Amplifier

LSB Least Significant Bit

**LUT** Lookup Table

**LVDS** Low Voltage Differential Signaling

MSB Most Bignificant Bit

NCO Numerically Controlled oscillator

**NF** Noise Factor

OMT OrthoMode Transducer

PCB Printed Circuit Board

PLL Phase Locked Loop

RF Radio Frequency

**RFD** Ready For Data

ROM Read Only Memory

**SDR** Software Defined Radio

**SFDR** Spurious Free Dynamic Range

**SNR** Signal to Noise Ratio

**SPI** Serial Peripheral Interface Bus

**TDP** Technology Demonstration Payload

TTL Transistor Transistor logic

**USB** Universal Serial Bus

**USRP** Universal Software Radio Peripheral

VCO Voltage Controlled Oscillator

**XPD** Cross Polarization Discrimination

## Capítulo 1

# Introdução

## 1.1 Enquadramento

Desde o lançamento do primeiro satélite artificial, o *Sputnik 1* em 1957, as comunicações por satélite têm sofrido uma grande evolução a diferentes níveis tecnológicos. Desde os modestos 20 MHz e 40 MHz utilizados como portadoras nos *transceivers* do primeiro satélite, que permitiam larguras de banda da ordem dos kHz, que se tem assistido a um aumento das velocidades de transmissão, bandas de frequência utilizadas e da diversidade de serviços fornecidos. Hoje em dia larguras de banda da ordem dos 500 MHz na banda Ka (20 GHz) estão a ser exploradas para fins comerciais e o interesse começa estender-se para a banda Q.

Por outro lado a propagação de sinais acima de 10 GHz na atmosfera sofre os seguintes efeitos:

- Atenuação (absorção) causada por água líquida (chuva, nuvens, nevoeiro) e vapor de água;

- Despolarização causada por chuva e nuvens de gelo;

- Cintilação causada por turbulência atmosférica devido à variabilidade temporal e espacial do índice de refraçção.

Todos os efeitos anteriores, excepto a atenuação por vapor de água, aumentam com a frequência (até pelo menos 90 GHz). A caracterização e a modelação destas contrariedades exige longas campanhas de medição. Estas por sua vez são efectuadas usando receptores dedicados que monitorizam o sinal  $Continuous\ Waveform\ (CW)$ , de elevada pureza espectral e estabilidade radiado por satélites geo-estacionário.

Os sinais a medir são habitualmente dois: o denominado *copolar* (recebido com uma polarização original) e o *crosspolar* (recebido com a polarização ortogonal). A medição da amplitude do primeiro permite obter a magnitude da atenuação atmosférica a qual é importante para saber durante quanto tempo do ano uma ligação de satélite estará indisponível. O segundo tem bastante menos potência e indica a despolarização introduzida pela atmosfera. A relação das amplitudes do canal *copolar* e *crosspolar* (em dB) é denominada de discriminação da polarização cruzada *Cross Polarization Discrimination (XPD).*

## 1.2 Motivação

A implementação de uma margem de atenuação para garantir a tradicional disponibilidade de serviço de 99.99% torna-se impraticável na banda Ka (e superiores) sem técnicas de correcção adequadas. No entanto é possível recorrer a diversas técnicas que podem contribuir para minorar

| Frequency<br>Band       | Uplink<br>Frequency<br>GHz | Downlink<br>Frequency<br>GHz | Major Applications                | Bandwidth          |

|-------------------------|----------------------------|------------------------------|-----------------------------------|--------------------|

| UHF Band (military)     | 0.292 - 0.312              | 0.250 - 0.270                | Military applications             | 20 MHz             |

| C Band (commercial)     | 5.9 - 6.4                  | 3.7 - 4.2                    | Television Broadcast              | 500 MHz            |

| X Band<br>(military)    | 7.25 - 7.75                | 3.7 - 4.2                    | Mobile (ships, aircrafts)         | $500~\mathrm{MHz}$ |

| Ku-Band<br>(commercial) | 14 - 14.5                  | 11.7 - 12.2                  | Broadcast and fixed point service | $500~\mathrm{MHz}$ |

| Ka-Band (commercial)    | 27 - 30                    | 17 - 20                      | Broadcast                         | $3~\mathrm{GHz}$   |

| Ka-Band<br>(military)   | 20 - 21                    | 11.7 - 12.2                  | Military                          | 1 GHz              |

|                         |                            |                              |                                   |                    |

Tabela 1.1: Bandas de Frequência utilizadas para serviços de Satélite. Adaptado de [BC07].

os efeitos de atenuação (Fade Counter-measuremente methods). A panóplia de métodos é grande e engloba o controlo de potência, a redução da taxa de transmissão, etc. A obtenção de dados experimentais relativamente ao sinal recebido na superfície terrestre é fundamental para o desenvolvimento de modelos para vários parâmetros do canal físico.

Para meados de 2013 está previsto o lançamento do satélite Alphasat I-XL que fornecerá diversos *Technology Demonstration Payload (TDP)* cujo desenvolvimento está por conta da agência espacial europeia (ESA). Um desses *Payloads* consistirá na emissão de sinal *CW* nas bandas Ka e Q para efeitos de recolha de dados e avaliação do meio de propagação.

No que toca à implementação dos detetores, o recente desenvolvimento dos sistemas de rádio digitais trouxe uma nova janela de oportunidades e um primeiro detetor usando *chips* discretos foi apresentado em [JCo98]. O detetor consistia em *chips Digital Receiver Signal Processor (DRSP)* que efectuavam a conversão e decimação dos sinais amostrados, os quais eram de seguida transferidos para um kit Digital Signal Processor (DSP). O método de detecção baseava-se numa estimativa espectral do sinal.

Os desenvolvimentos seguintes usaram uma abordagem semelhante contudo introduziu-se uma *Phase Locked Loop (PLL)* por software reprogramando os osciladores digitais nos *chips* DRSP [Pir07] [Sou07]. Outro tipo de loops foram superficialmente testados para esta aplicação.

## 1.3 Objetivos

Face ao exposto o objectivo deste trabalho é a implementação de hardware que permita a medição de sinal CW a partir de uma frequência intermédia (IF) convertida previamente por um andar de conversão de frequência analógico. De entre os requisitos desejáveis do sistema é possível destacar:

• Medição da amplitude e fase relativa dos canais copolar e crosspolar;

- Tracking da frequência central do sinal recebido;

- Rejeição de ruído fora da banda do sinal.

A medição do tipo de sinais aqui pretendido é sempre problemático pois o sinal recebido é invariavelmente fraco ou seja a sua Carrier to Noise Ratio (CNR) (dBHz) raramente excede os 55 dB em recetores com antenas até cerca de 1 a 1.5 metros de diâmetro. Outro problema é o espalhamento espectral do sinal (ruído de fase) que leva à necessidade de usar uma largura de banda não nula para ser possível efectuar a sua detecção com a máxima gama dinâmica. A gama dinâmica de medida da atenuação e despolarização é sempre limitada e aproveitar o melhor possível os limites teóricos nas medidas é sempre importante.

Face ao exposto, os objetivos do trabalho resumem-se a:

- Análise e apresentação de várias técnicas de detecção de sinal CW;

- Desenvolvimento de um sistema completamente integrado com Analog to Digital Converter (ADC) e uma Field Programmable Gate Array (FPGA), com a capacidade de autonomamente implementar as técnicas de detecção mais comuns e de enviar os resultados às taxas necessárias para o tipo de estudos em vista.

Esta ideia, em termos de hardware, partiu dos kits Software Defined Radio (SDR) de uso comum, com a única diferença a residir no facto de o processamento de sinal ser também efetuado dentro da FPGA. A razão para o desenvolvimento desta solução mais especializada prende-se com a pouca flexibilidade de configuração destes kits: um sistema de detecção utilizando o kit Universal Software Radio Peripheral (USRP) da Ettus Research foi efectuado em [Sou11] contudo constatou-se que era muito complicado utilizar o mesmo Numerically Controlled oscillator (NCO) para detetar mais que um canal dentro da FPGA. Para permitir o anterior seria necessário ter acesso e modificar o código Hardware Description Language (HDL) dos kits assim como efetuar a reprogramação do mesmo.

Apenas uma solução similar a esta terá sido desenvolvida por uma firma britânica <sup>1</sup> que contudo usava *chips* dedicados à implementação eficiente de FFTs. Não se conhecem desenvolvimentos posteriores.

## 1.4 Estrutura da dissertação

Este documento encontra-se organizado em seis capítulos. O capítulo atual visa fazer um enquadramento nos sistemas de telecomunicações por satélite, realçar a importância da obtenção de dados experimentais para caracterização física do canal atmosférico e apresentar também os objetivos propostos para a atual dissertação.

- Capítulo 2: É efetuada a caracterização do sinal a detetar e são apresentados vários métodos de deteção de sinal CW, dando-se particular relevância a deteção síncrona usando malhas de sincronização. São apresentados também resultados da simulação efetuada em Simulink relativamente a uma PLL digital.

- Capítulo 3: Descrição do sistema físico implementado para a digitalização da IF e que realiza a interface com a FPGA e com o PC anfitrião.

- Capítulo 4: Arquitectura do detetor síncrono implementado em FPGA, sinais de interface com a placa de conversão analógico-digital, blocos instanciados, síntese de filtros digitais e

$<sup>^1 {</sup>m Signal~Processors~Limited}$

dimensionamento da PLL digital.

- Capítulo 5: Comunicação via *Universal Serial Bus (USB)* com o PC anfitrião. É apresentada a estrutura básica do controlador USB e o seu modo de funcionamento, de seguida são apresentados os mecanismos que foram construídos, tanto ao nível da FPGA como do computador hospedeiro, de modo a possibilitar a transferência de informação.

- Capítulo 6: Descrição dos testes realizados ao sistema e análise dos métodos de deteção implementados, domínio da frequência com recurso a Fast Fourier Transform (FFT) complexa e com PLL digital.

- Capítulo 7: Conclusões finais e propostas de trabalho futuro.

- Anexo A: Esquemático, diagrama de blocos e opções de configuração da placa de conversão analógico-digital.

- Anexo B: Diagrama de blocos do sistema implementado em FPGA, ocupação de recursos e configurações utilizadas nos *IP cores* da Xilinx.

- Anexo C: Procedimento para o setup da placa TE0320: instalação de drivers do controlador USB FX2 e programação da PROM.

- Anexo D: Instruções para o desenvolvimento de software utilizando a framework Nokia QT e os drivers do controlador USB FX2 em ambiente Microsoft Visual Studio 2010.

- Anexo E: Descrição da aplicação desenvolvida para interface com a FPGA e recolha de dados.

## Capítulo 2

## Conceitos Fundamentais

## 2.1 Introdução

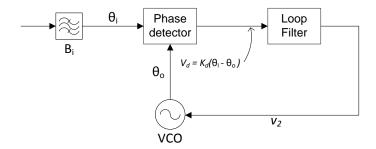

Sendo o objectivo do presente trabalho a realização de um detetor de sinal digital a partir de uma frequência intermédia é do maior interesse saber as características e condições em que chega esse mesmo sinal. A figura 2.1 apresenta o diagrama de blocos geral do sistema. Antes de ser processado digitalmente o sinal de satélite recebido pela antena passa por um bloco analógico (desenvolvido fora do âmbito desta dissertação) cujo objectivo é condicionar o sinal de modo a fornecer uma réplica deste, em amplitude e diferença de fase, a uma frequência mais reduzida, passível de ser digitalizada e processada posteriormente. Para além disto é neste bloco que se efetua a separação do sinal recebido em duas polarizações ortogonais obtendo-se os chamados sinais copolar e crosspolar. Para além da caracterização do sinal a detectar serão apresentados vários métodos de deteção de sinal CW e alguns resultados decorrentes da implementação de tais métodos em Simulink.

## 2.2 Caracterização do sinal a detectar

O satélite Alphasat I-XL terá dois *beacons* (padrões de frequência) coerentes nas bandas Ka e Q, derivados de uma fonte comum de baixo ruído de fase. As características previstas dos *beacons* encontram-se sumariadas na tabela 2.1.

Figura 2.1: Arquitectura geral do detector síncrono baseado em FPGA

## 2.2.1 EIRP

Define-se por Equivalent Isotropically Radiated Power (EIRP) a potência necessária por uma antena isotrópica para produzir a mesma densidade de potência numa dada direção que frequen-

| Beacon                              | Ka Beacon       | Q Beacon               |

|-------------------------------------|-----------------|------------------------|

| Frequency (GHz)                     | 19.701          | 39.402                 |

| Polarization                        | Linear Vertical | Linear at $45^{\circ}$ |

| EIRP                                | 21.5            | 29.3                   |

| Frequency stability (3 years) (ppm) | 2               | 2                      |

| Phase Noise (dBc) at Amb. Temp      |                 |                        |

| 10 Hz                               | -48.19          | -40.10                 |

| 100 Hz                              | -56.00          | -51.16                 |

| $1000~\mathrm{Hz}$                  | -68.49          | -60.00                 |

| 10  kHz                             | -69.95          | -62.63                 |

Tabela 2.1: Alphasat I-XL beacon: Características esperadas.

temente é a direção do receptor 2.2. Pode ser calculado através da equação 2.1

$$EIRP = P_T + G_T \quad (dBW) \tag{2.1}$$

Em que  $P_T$  representa a potência transmitida à antena em dBW e  $G_T$  o ganho da antena em relação a uma antena isotrópica (dBi). O EIRP toma valores absolutos que podem variar entre 20 e 30 dBW. A ordem de grandeza típica para as variações do EIRP devidos aos ciclos de aquecimento/arrefecimento de periodicidade diária é de algumas décimas de dB.

Figura 2.2: Power Budget: conjunto emissor-receptor.

## 2.2.2 Bloco Analógico

Não é objectivo desta dissertação aprofundar o funcionamento e as características deste bloco pelo que se irá apenas fazer uma breve descrição dos aspectos essenciais.

A arquitetura do bloco é ilustrada na figura 2.3. A antena é do tipo cassegrain com um prato de 1  $m^2$ , a separação das polarizações é feita com recurso a um  $OrthoMode\ Transducer\ (OMT)$  com um isolamento de 30 dB entre os canais. Posteriormente é feita uma conversão em frequência seguindo um esquema de desmodulação super-heterodino com vários estágios onde consecutivamente se vai diminuindo a frequência intermédia e a largura dos filtros passa banda.

Figura 2.3: Conversão do sinal recebido para a frequência IF.

### 2.2.2.1 CNR - Link Budget

O link budget é calculado relativamente ao beacon Ka e para a saída receptor analógico descrito na secção anterior. CNR por definição é o quociente entre potência da portadora e a densidade espectral de ruído que o acompanha, ou a diferença no caso de os respectivos valores estiverem representados em unidades logarítmicas.

$$CNR_0 = P_{recebida} - \eta_{ruido} \quad (dB/Hz)$$

(2.2)

Uma estimativa da potência recebida pode ser calculada através da seguinte equação:

$$P_{in} = EIRP - (L + L_{omt} + A_g) + G_r \quad (dBW)$$

(2.3)

Em que L e  $L_{omt}$  representa as perdas em espaço livre devido à distância do satélite (38400 km) e as perdas do OMT,  $A_g$  a atenuação devido a partículas atmosféricas e  $G_r$  o ganho da antena receptora. Por outro lado a densidade espectral de ruído à saída da unidade analógica  $\eta_{ruído}$  é dado por:

$$\eta_{ruido} = k_B T_{eq} = k_B \left( T_{sky} + T_{rx} \right) \quad (dBW/Hz) \tag{2.4}$$

A temperatura de ruído equivalente do sinal no receptor à frequência intermédia apresenta contribuições da potência de ruído recebida pela antena devido à absorção atmosférica  $(T_{sky})$  e do ruído introduzido pelos atenuadores e amplificadores da cadeia de recepção  $T_{rx}$ ,  $k_B$  representa a constante de  $Boltzmann (-228.6 \ (dBW/Hz)/K)$ .

$$T_{rx} = T_0 \left( 10^{\frac{L_{omt}}{10}} - 1 \right) + \frac{T_{Lna}}{10^{-L_{omt}/10}}$$

(K) (2.5)

$$T_{Lna} = T_0 \left( 10^{\frac{NF}{10}} - 1 \right)$$

(K) (2.6)

Assume-se que o ganho do primeiro Low Noise Amplifier (LNA) é suficientemente grande para se desprezar a contribuição de ruído pelos amplificadores seguintes. NF representa a figura de ruído do primeiro LNA e  $L_{omt}$  a figura de ruído do OMT que é idêntico ao seu factor de perdas.

A tabela 2.2 resume os valores envolvidos no cálculo do *link budget* e apresenta o valor esperado para a CNR do sinal em condições normais.

Por último a Signal to Noise Ratio (SNR) do sinal obtido pode ser calculada através de:

$$SNR = CNR - 10\log_{10}\left(B_i\right) \tag{2.7}$$

onde  $B_i$  é a largura de banda do detetor.

Para o valor médio de CNR do sinal (56.4 dB) pode-se verificar que para uma largura do filtro de pré deteção  $B_i$  maior que 1 MHz (60 dB) a potência do ruído é superior à do sinal.

| Var.      | Description                                 | Value (Ka-Band) | Un.              |

|-----------|---------------------------------------------|-----------------|------------------|

| EIRP      | Potência isotrópica radiada equivalente     | 21.5            | dBW              |

| $G_r$     | Ganho da antena 1m                          | 44.1            | dB               |

| L         | Perdas de propagação                        | 210.0           | dB               |

| $A_{q}$   | Perdas Atmosféricas                         | 0.5             | dB               |

| $L_{omt}$ | Perdas OMT                                  | 0.8             | dB               |

| $P_{in}$  | Potência à saída do OMT                     | -115.7          | $\mathrm{dBm}$   |

| $T_{sky}$ | Temperatura de ruído: atmosfera (Clear Sky) | 32.9            | K                |

| NF        | LNA Noise Factor                            | 3.0             | dB               |

| $T_{rx}$  | Temperatura de ruído: receptor (Clear Sky)  | 438.5           | K                |

| CNR       | Carrier to noise ratio (Clear Sky)          | 56.4            | $\mathrm{dB/Hz}$ |

Tabela 2.2: Link Budget: Sistema satélite  $\rightarrow$  recetor terrestre.

## 2.3 Métodos de deteção

Como foi referido anteriormente, a detecção consiste na estimação da amplitude/potência do sinal de entrada e no caso de dois canais também a fase relativa entre os dois sinais. Nesta secção serão descritas algumas das técnicas mais comuns tendo em consideração que o sinal à entrada do detetor se encontra afetado por ruído  $Additive\ White\ Gaussian\ Noise\ (AWGN)$  de banda estreita resultante da filtragem passa banda pelo filtro de pré detecção  $B_i$ .

$$s(t) = A_0 \cos(\omega t + \phi_n(t)) + n_i(t) \cos(\omega t) + n_q(t) \sin(\omega t)$$

(2.8)

Onde  $n_i(t)$  e  $n_q(t)$  são as componentes em fase e quadratura do ruído gaussiano em banda base e  $\phi_n(t)$  o ruído de fase do sinal.

## 2.3.1 Detecção no domínio do tempo

Provavelmente o método mais simples de implementar (2.4), consiste essencialmente num bloco quadrador seguido de um filtro passa baixo para eliminar a réplica de maior frequência.

A saída do detetor é dada por 2.9.

$$\overline{s(t)^2} = \frac{A_0^2}{2} + \eta_0 B_1 \tag{2.9}$$

Como se pode verificar a amplitude detectada inclui um desvio sistemático devido à deteção de ruído não filtrado por  $B_1$ . A utilização de um filtro arbitrariamente estreito de modo a tornar o erro desprezável também não é uma solução viável pelos seguintes motivos:

- Em situações reais o sinal a detectar não se encontra, em frequência, contido numa única risca infinitesimal. Tomando o exemplo do beacon Ka (2.1) a potência do sinal encontra-se espalhada numa largura de banda de cerca de 50 Hz devido ao ruído de fase dos osciladores do recetor e do sinal.

- A utilização de um filtro largo implica a admissão de ruído adicional no resultado da detecção, por outro lado também não é possível recorrer a um filtro demasiado estreito com risco de se estar a cortar potência do sinal.

- O sinal na prática sofre deslocamentos na frequência central devido ao envelhecimento dos osciladores a cristal tanto na parte de emissão como de recepção.

Figura 2.4: Detecção no tempo via quadrador e filtro passa-baixo.

## 2.3.2 Deteção no domínio da frequência

Um outro método de detecção pode ser implementado utilizando medidas no domínio da frequência. Um dos métodos mais comuns consiste em realizar FFTs em tempo real do sinal, procurar o máximo e somar as riscas adjacentes correspondentes à largura de banda do sinal. Considerando que a potência do sinal se encontra contida entre as riscas  $r_1$  e  $r_2$  (inclusivé) a potência desta banda pode ser calculada recorrendo à fórmula de Parseval.

$$P_b = \sum_{n=r_1}^{r_2} S(n)S(n)^*$$

(2.10)

Onde S(n) representa a N-ésima linha espectral da FFT complexa e (\*) o operador de conjugado complexo. Naturalmente  $P_b$  representa não só a potência do sinal mas também a potência do ruído AWGN. De modo a obter um valor mais preciso pode-se estimar estimar um valor da densidade espectral ruído através das restantes riscas.

$$\eta_0 = \frac{\sum_{n=0}^{r_1} |S(n)|^2 + \sum_{n=r_2}^{N-1} |S(n)|^2 - P_b}{B_n}$$

(2.11)

Onde  $B_n$  representa a largura de banda do sinal processado pela FFT excluindo as riscas que contêm o sinal. Não é estritamente obrigatório que se utilizem todos os índices da FFT mas uma melhor estimativa resulta se tal for efetuado.

$$B_s = (r_2 - r_1 + 1)\frac{f_a}{N} \qquad B_n = (N - (r_2 - r_1 + 1))\frac{f_a}{N}$$

(2.12)

Finalmente um valor mais exato da potência detectada pode ser obtido obtido subtraindo a  $P_b$  o valor estimado do ruído para a respectiva banda  $(B_s)$  o qual deve ser integrado durante o tempo mais longo possível.

$$P_s = P_b - \eta_0 B_s \tag{2.13}$$

Naturalmente neste contexto N representa o número de amostras utilizadas para o algoritmo da FFT e  $f_a$  a frequência de amostragem do sinal.

## 2.3.3 Deteção síncrona usando malhas de sincronismo

Um outro método de detecção promissor é o uso de um oscilador local  $A_{ref}(t)$  sincronizado com o sinal de entrada (possivelmente com um offset de fase  $\theta_0$ ).

$$A_{ref}(t) = A_{OR}\cos\left(\omega t + \phi_n(t) + \theta_0\right)$$

(2.14)

Figura 2.5: Diagrama de blocos genérico de uma PLL.

A obtenção deste sinal síncrono pode ser obtido com malhas de sincronismo como a PLL, Frequency Locked Loop (FLL) ou Costas Loop, que basicamente utilizam um NCO ou Voltage Controlled Oscillator (VCO) inseridos numa malha de realimentação para sintetizar um sinal proporcional em fase ou frequência ao de entrada.

Após a obtenção deste sinal a detecção resume-se basicamente à multiplicação destes dois sinais e à respectiva filtragem passa baixo (ou média/integração). Deve-se ter em atenção que larguras de banda muito reduzidas podem inviabilizar a correta medição de fenómenos de propagação que apresentam frequências mais elevadas.

$$\overline{s(t)_i} = \overline{s(t) A_{0r} \cos(\omega t + \phi_n(t) + \theta_0)} = \frac{A_0 A_{0r}}{2} \cos \theta_0 + \frac{A_{0r} n_i(t)}{2}$$

(2.15)

$$\overline{s(t)_q} = \overline{s(t) A_{0r} \cos\left(\omega t + \phi_n(t) + \theta_0 - \frac{\pi}{2}\right)} = \frac{A_0 A_{0r}}{2} \sin \theta_0 + \frac{A_{0r} n_q(t)}{2}$$

(2.16)

$\mathrm{d}$

Após deteção toda a potência do sinal encontra-se em banda base e a contribuição do ruído de fase para a medida parece ser nula, adicionalmente se:  $\theta_0 = k.\pi/2, (k \in \mathbb{Z})$  a componente em quadratura torna-se nula o que permite excluir  $n_q(t)$ , ou seja, metade do ruído presente na deteção o que contribuí para uma melhoria de 3 dBs da SNR. Na secção seguinte dedicada às PLL será possível verificar que esta condição se verifica sempre que a malha se encontre em sincronismo.

## 2.4 Malhas de sincronização - PLL

Uma PLL ou malha de seguimento de fase consiste basicamente num sistema de realimentação constituído por três blocos essenciais que se podem observar na figura 2.5: um detetor de fase, um oscilador local controlável e um filtro de malha. O detetor de fase calcula a diferença de fase instantânea entre o sinal de entrada e de saída (VCO) que por sua vez é integrado ao longo do tempo de modo a levar o VCO a sincronizar em frequência com o sinal de entrada. Uma vez em sincronismo qualquer desvio de frequência é compensado com o desenvolvimento de uma tensão de correção no detetor de fase.

Recordando que o sinal é corrompido por ruído aditivo AWGN e ruído de fase é necessário que a PLL esteja convenientemente dimensionada de modo a rejeitar o mais possível o ruído aditivo, sem no entanto, comprometer a qualidade e a gama dinâmica da deteção.

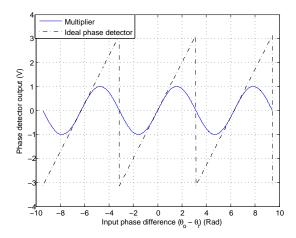

Figura 2.6: Comparação entre a saída do detector de fase ideal e um multiplicador, considerando entradas sinusoidais.

#### 2.4.0.1 Detetor de Fase

Idealmente um detetor de fase tem uma saída proporcional à diferença de fase entre duas entradas:

$$v_d = K_d \left( \theta_i - \theta_o \right) \tag{2.17}$$

Onde  $K_d$  é o ganho do detetor de fase e tem dimensões de V/rad. Muito frequentemente este componente é um simples multiplicador, assumindo que os sinais de entrada se encontram inicialmente dessincronizados:

$$y_i(t) = A\sin(\omega t + \phi_i(t))$$

(2.18)

$$y_o(t) = B\cos(\omega t + \phi_0(t))$$

(2.19)

A frequência angular dos dois sinais não é necessariamente igual uma vez que a diferença pode ser incluída em  $\phi_i(t) - \phi_o(t)$ . A saída do multiplicador, desprezando a componente de alta frequência, resulta num sinal do tipo:

$$u_1(t) = \frac{AB}{2}\sin(\phi_i(t) - \phi_0(t))$$

(2.20)

Um dos problemas do multiplicador em relação ao detetor ideal é a não linearidade do mesmo (figura 2.6), o que traz consequências no comportamento dinâmico da PLL como se vai ver mais adiante. Contudo para pequenos valores de  $\left(\phi_i(t)-\phi_0(t)\right)$  é possível fazer a aproximação  $\sin(\theta_d)\approx\theta_d$

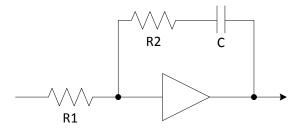

#### 2.4.0.2 Filtro de Malha

O filtro de malha é bastante influente sobre o comportamento dinâmico da PLL. O filtro é de natureza passa-baixo de modo a eliminar as componentes de alta frequência à saída do detetor, e naturalmente também ruído. Um estudo exaustivo dos vários tipos de filtros de malha é efetuado em [Gar66] e [Bla76], contudo apenas vai ser abordado o filtro de 2ª ordem com integrador perfeito e correção de avanço de fase representado na figura 2.7.

Figura 2.7: Filtro de malha de 2ª ordem com integrador e correcção de avanço de fase.

A saída do filtro em termos de transformada de Laplace vem dada por:

$$F(s) = \frac{s CR_2 + 1}{s CR_1} = \frac{s \tau_2 + 1}{s \tau_1} = \frac{\tau_2}{\tau_1} + \frac{1}{s \tau_1}$$

(2.21)

Onde  $\tau_1$  e  $\tau_2$  representam as constantes de tempo, podendo-se concluir que a função de transferência apresenta um fator proporcional  $\tau_2/\tau_1$  e um fator integrador  $1/\tau_1$ .

Para além da filtragem de ruído o filtro tem como objectivo integrar ou fazer a média da saída do detetor de fase. Isto significa que para o sinal de entrada do VCO estabilizar é necessário que o sinal de entrada do filtro seja em termos médios igual a zero o que significa, por sua vez, que as frequências dos sinais de entrada da PLL são idênticas.

#### 2.4.0.3 VCO

Como o próprio nome indica são osciladores controlados por tensão. A saída é uma sinusóide de amplitude constante cuja frequência  $\Delta \omega_o$  em torno de uma frequência central é função da tensão de controlo de entrada  $v_c$ . O desvio do VCO em relação à frequência central é dada então por:

$$\Delta \omega_o = K_o v_c \tag{2.22}$$

Uma vez que a frequência é a derivada em ordem ao tempo da fase a equação pode ser reescrita como:

$$\frac{d\theta_o}{dt} = K_o v_c \tag{2.23}$$

Ou aplicando a transformada de Laplace:

$$s \theta_o(s) = K_o V_c(s) \Rightarrow \theta_o(s) = \frac{K_o V_c(s)}{s}$$

(2.24)

#### 2.4.0.4 Função Transferência

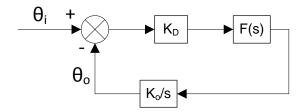

Na figura 2.8 está representado um diagrama da malha da PLL, cujas funções de transferência de cada bloco estão de acordo com as respectivas equações 2.21 e 2.24. Como se pode observar a função de transferência em malha aberta é dada por:

$$G(s) = \frac{K_d K_o F(s)}{s} \tag{2.25}$$

e logo, a função de transferência em malha fechada é dada por:

$$H(s) = \frac{G(s)}{1 + G(s)} = \frac{K_d K_o F(s)}{s + K_d K_o F(s)}$$

(2.26)

Figura 2.8: Diagrama de blocos da PLL no domínio de Laplace.

Outro parâmetro útil para a análise do sistema é o ganho em Direct Current (DC) em malha aberta dado por:

$$K_v = \lim_{s \to 0} s G(s) = K_d K_o F(0)$$

(2.27)

Substituindo F(s) pelo filtro apresentado na seção 2.4.0.2, a função transferência fica finalmente:

$$H(s) = \frac{K_d K_o (s \tau_2 + 1) / \tau_1}{s^2 + s (K_d K_o \tau_2 / \tau_2) + K_d K_o / \tau_1}$$

(2.28)

podendo ser reescrita usando a notação comum para sistemas lineares de 2ª ordem,

$$H(s) = \frac{2\zeta \omega_n s + \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

(2.29)

onde  $\omega_n$  é a frequência natural e  $\zeta$  é o coeficiente de amortecimento, dados por:

$$\omega_n = \sqrt{\frac{K_d K_o}{\tau_1}} \qquad \qquad \zeta = \frac{\tau_2}{2} \sqrt{\frac{K_d K_o}{\tau_1}} \qquad (2.30)$$

### 2.4.0.5 Largura de Banda de ruído

Considerando que o sinal à entrada da PLL é caracterizado por uma densidade espectral de ruído de fase  $S_{ni}(f)$  este vai ser alterado como resultado da actuação da PLL, recorrendo à teoria dos sistemas lineares invariantes no tempo e considerando o ruído em causa um processo estacionário é possível calcular o ruído à saída do sistema.

$$S_{no}(f) = |H(f)|^2 S_{ni}(f)$$

(2.31)

A potência de ruído  $\overline{\theta_{no}^2}$  ou jitter de fase à saída resulta da integração matemática de  $S_{no}$  sobre a banda do filtro de pré-deteção  $B_i$ .

$$\overline{\theta_{no}^{2}} = \int_{0}^{B_{i}/2} |H(f)|^{2} S_{ni}(f) df \approx S_{ni}(f) \int_{0}^{\infty} |H(f)|^{2} df$$

(2.32)

A aproximação efectuada considera que o filtro de pre-deteção é muito mais largo que a largura de banda de H(f) o que em geral se verifica sempre devido aos filtros de pre-deteção terem de acomodar as variações na Intermediate Frequency (IF).

Deste modo, e observando a equação 2.32, é possível definir  $B_L$  como a largura de banda equivalente que um filtro passa baixo perfeito precisaria de ter para se obter a mesma potência de ruído à saída da PLL.

$$B_L = \int_0^\infty |H(f)|^2 df$$

(2.33)

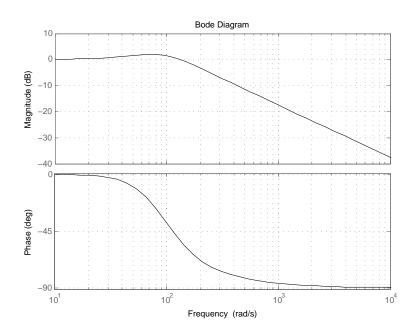

Figura 2.9: Diagrama de Bode da PLL com filtro de malha ativo de 2ª ordem.

Para o caso particular que temos vindo a considerar de um filtro de segunda ordem, o valor 2.33 encontra-se tabelado em [Gar66] e é dado por:

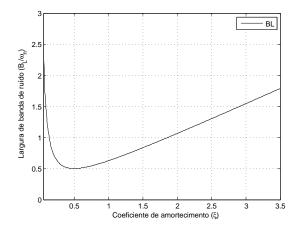

$$B_L = \frac{\omega_n}{2} \left( \zeta + \frac{1}{4\zeta} \right) \quad (Hz) \tag{2.34}$$

A curva é apresentada na figura 2.10 e é possível verificar que a largura de banda de ruído apresenta um mínimo para  $\zeta=0.5$ .

## 2.4.0.6 Potência de ruído

De acordo com [Gar66] é possível calcular a potência do ruído de fase de um sinal afectado por AWGN. De facto a adição de ruído na amplitude causa incerteza nas passagens por zero. A relação é estabelecida por:

$$\overline{\theta_{ni}^2} = \frac{1}{2SNR_i} \tag{2.35}$$

e consequentemente a potência do ruído de fase à saída da PLL é dada por:

$$\overline{\theta_{no}^2} = \frac{B_L}{2CNR_i} \tag{2.36}$$

que é um resultado intuitivo. A potência de ruído à saída da PLL é tanto menor quanto maior for a CNR do sinal de entrada e é proporcional à largura de banda de ruído  $(B_L)$ , contudo existem também problemas decorrentes de diminuir demasiado este parâmetro:

- A diminuição de  $B_L$  implica diminuir a largura de banda do filtro de malha (passa-baixo). Se a diferença de frequência do sinal de entrada em relação ao VCO for demasiado elevada o sinal à saída do detetor de fase é fortemente atenuado o que por sua vez implica que a tensão de correção do VCO pode não ser suficiente para corrigir a sua frequência;

- Da mesma forma, se o sistema se encontrar inicialmente em sincronismo, pequenos desvios na frequência que ocorrem em situações reais serão dificilmente corrigidos pela PLL. Uma

Figura 2.10: Largura de banda de ruído da PLL em função do coeficiente de amortecimento, considerando filtro de malha ativo de 2ª ordem.

outra forma de ver as coisas é constatar que diminuir  $B_L$  em geral é conseguido através da diminuição da frequência natural  $\omega_n$ , o que implica situar os pólos do sistema mais próximo da origem o que por sua vez se traduz em tempos de resposta mais longos relativamente a alterações do sinal de entrada.

#### 2.4.0.7 Manutenção e aquisição de sincronismo

Em termos de sistema, inicialmente, é de esperar que as frequências do VCO e do sinal de entrada sejam diferentes. Consoante a dimensão deste desvio e dos parâmetros da PLL. Se o detetor fosse ideal, independentemente das condições iniciais dos dois sinais, a PLL chegaria sempre ao sincronismo uma vez que desenvolveria sempre uma tensão proporcional à diferença de fase entre os dois sinais porém, como foi visto na secção 2.4.0.1, a utilização de multiplicadores ou outros circuitos de deteção de fase possuem curvas de saída diferentes das ideais. Este facto provoca que em alguns casos a PLL atinja o sincronismo mais lentamente se a diferença de frequências dos sinais de entrada for elevada ou mesmo tornar impossível a aquisição de sincronismo. De acordo com [Gar66] é possível distinguir três gamas de frequências:

- Gama de Lock-In:  $|\Delta\omega| < K_v$ O sincronismo é quase imediato, uma vez que a tensão desenvolvida à entrada do VCO nos primeiros ciclos é suficiente para corrigir a frequência do mesmo;

- Gama de Hold- $In: K_v < |\Delta \omega| < 2\sqrt{\zeta \omega_n K_v}$ O sincronismo não é imediatamente atingido, mas é desenvolvida uma tensão de média não nula à saída do detetor de fase (beatnote) que ao longo do tempo vai corrigindo a frequência do VCO:

- Gama em que não é atingido sincronismo:  $2\sqrt{\zeta\omega_nK_v}<|\Delta\omega|$

## 2.4.1 PLL: Simulação em Simulink

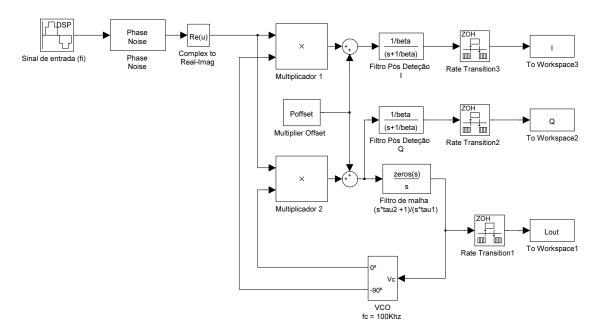

Com o objectivo de aprofundar o conhecimento na área das PLLs e para efeitos de estudo do sistema a implementar foi realizado um modelo parametrizável em *Simulink*. O diagrama de blocos encontra-se na figura 2.11, essencialmente trata-se de uma PLL simples em que a saída do VCO é utilizada para obter as componentes em fase (I) e quadratura (Q) de um sinal sinusoidal de entrada. Para além disto foram introduzidas várias não idealidades como a adição de ruído de fase à entrada do sistema e offset de tensão à saída dos multiplicadores.

Figura 2.11: Circuito de simulação da PLL realizado em Simulink.

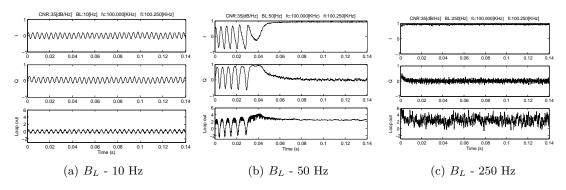

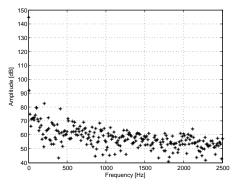

O ruído de fase sintetizado apresenta um decaimento na forma de 1/f em torno da frequência central da portadora, como se pode observar na figura 2.15.

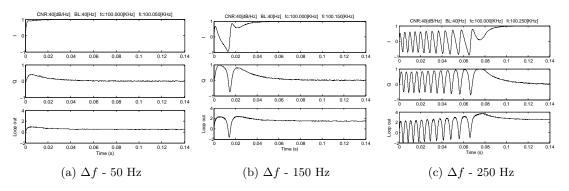

De modo a avaliar o impacto de certos parâmetros do loop, foram efetuados alguns testes com este modelo, nomeadamente:

- 1. Variação da CNR do sinal de entrada, para um desvio inicial de frequência de 100 Hz em relação à frequência inicial do VCO (lock-in);

- 2. Variação da frequência de entrada para um valor de CNR médio (40 dB/Hz);

- 3. Variação da largura de banda de ruído.

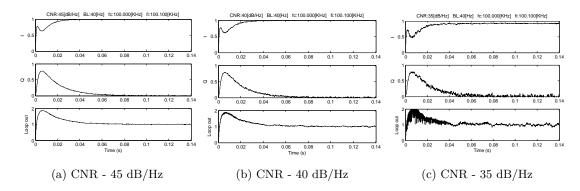

Os resultados destes testes, nomeadamente as componentes I/Q detetadas e a tensão de entrada do VCO  $(L_{out})$ , estão representadas nas figuras seguintes. O propósito principal destes testes foi avaliar qualitativamente o impacto dos parâmetros do loop pelo que a análise será da mesma natureza:

- 1. figura 2.12 Verifica-se que um aumento do ruído leva a uma maior variância nas componentes I/Q como seria de esperar;

- 2. figura 2.13 (a) o desvio de frequência do sinal de entrada para a frequência central do VCO encontra-se dentro da gama de lock-in pelo que a aquisição de sincronismo é quase imediata, fora desta gama (a e b) o sincronismo é muito mais demorado, havendo deslizamento das duas frequências o que leva ao aparecimento das oscilações observadas nas componentes I/Q;

- 3. figura 2.14 (a) a largura de banda do loop é muito reduzida (10 Hz) pelo que o sinal de entrada é fortemente atenuado o que impede o VCO a adquirir o sincronismo rapidamente, (c) largura de banda excessiva, o loop adquire rapidamente o sincronismo mas as componentes I/Q são bastante afetados pelo ruído fora da banda do sinal, (b) situação intermédia em que existe o compromisso entre rapidez da resposta dinâmica e variância de ruído à saída.

#### 2.5 Sumário

Neste capítulo foi descrito o bloco analógico prévio ao detetor digital, o link budget foi calculado à saída do mesmo para valores típicos de ruído atmosférico obtendo-se uma valor de cerca de 56 dB para a CNR esperada do sinal. O espalhamento espectral da potência do sinal a detectar e o desvio em frequência ao longo do tempo do mesmo torna pouco viáveis os métodos de deteção com base em quadrador e filtragem. Os métodos tipo PLL que utilizam uma portadora sincronizada com o sinal de entrada resolvem este problema pelo que será o método a implementar no detetor digital, contudo, é necessário dimensionar corretamente os parâmetros da malha de modo a haver um bom compromisso entre a variância de ruído à saída e rapidez da resposta dinâmica.

Figura 2.12: Simulações com variação de CNR.  $\Delta f$  =100 Hz,  $B_L$  =40Hz,  $\zeta$  = 0.707.

Figura 2.13: Simulações com variação do desvio de frequência. CNR=40 dB/Hz,  $B_L$  =40Hz,  $\zeta=0.707.$

Figura 2.14: Simulações com variação da largura de banda de ruído. CNR=35 dB/Hz,  $\Delta f$  =250 Hz,  $\zeta=0.707.$

Figura 2.15: Espectro do sinal de entrada simulado, com adição de ruído.

### Capítulo 3

# Plataforma de Hardware do Detetor

#### 3.1 Introdução

Este capítulo tem como objectivo descrever e justificar as escolhas efetuadas a nível de hardware para a implementação do detetor de sinal a partir da sua frequência intermédia. Como foi referido no capítulo anterior a frequência do sinal encontra-se situada nos 10.7 MHz e é necessário efetuar a sua conversão para o domínio digital de modo a poder ser processada pelo detetor. Quanto ao processamento digital são descritas brevemente as duas opções mais comuns, nomeadamente os Digital Signal Processors (DSPs) e as FPGAs.

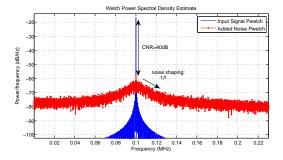

### 3.2 Field Programmable Gate Arrays (FPGA's)

Uma FPGA é, na sua essência, um circuito integrado que contêm uma matriz de elementos programáveis que podem ser interconectados de forma flexível para implementar um circuito digital específico. Os elementos lógicos podem-se dividir basicamente em três categorias:

- Blocos Lógicos tipicamente Configurable Logic Blocks (CLBs), os blocos básicos de construção do sistema digital compostos geralmente por Look up Tables (LUT), registos (Flip Flops) e multiplexers.

- Blocos I/O Permitem a conexão de sinais internos da FPGA aos pinos de I/O e vice-versa, condicionamento de sinal (níveis de tensão) e configurar o drive de corrente.

- Switch Matrixes Responsáveis pela configuração das ligações entre elementos lógicos.

A configuração dos elementos lógicos é geralmente efetuada a partir de linguagens de descrição de *hardware* que descrevem a nível comportamental ou a nível das próprias ligações o circuito deseiado.

Uma das vantagens de efetuar processamento de sinal em FPGA decorre do facto de o processamento ser inerentemente paralelo o que permite a realização de vários etapas de tratamento de sinal simultaneamente sem que para isso sejam necessárias frequências de relógio muito elevadas (quando comparadas com uma implementação em DSP).

Deste modo quase se pode dizer que a FPGA é um meio termo entre um Application-specific integrated circuit (ASIC) e uma DSP, permitindo a realização de sistemas complexos e específicos para a aplicação em causa e ao mesmo tempo permitindo a reconfigurabilidade do mesmo.

Figura 3.1: FPGA: Arquitectura em forma de matriz.

#### 3.2.1 Comparação entre FPGAs e DSPs

Os algoritmos de processamento digital podem ser implementados também através de DSPs, sendo os mesmos, microprocessadores otimizados para o efeito. A otimização consiste essencialmente numa arquitetura que facilita a realização de produtos internos e operações aritméticas que permitem maior eficácia em operações comuns de processamento de sinal, nomeadamente: convolução, correlação, FFT, cálculos matriciais, etc.

As DSPs são também bastante flexíveis e podem ser programados de forma fácil e rápida com recurso a linguagens de alto-nível, como por exemplo C. Contudo em comparação com as FPGAs a flexibilidade é menor decorrente da arquitetura fixa das DSPs, em contrapartida os tempos de desenvolvimento são muito menores. A tabela 3.1 resume as vantagens e desvantagens das duas tecnologias.

Tendo em conta a referida tabela e o esquema de um detetor com recurso a malha de sincronização as vantagens são evidentes. Dificilmente uma DSP de baixa-média gama teria capacidade para processar continuamente e em tempo-real um sinal amostrado a uma frequência da ordem dos MHz. Para além disso, quer as necessidades de I/O do sistema (2 canais de entrada, e envio em tempo real da detecção para um computador) quer a natureza das malhas de sincronismo, fazem valer a paralelização de operações inerente à implementação em FPGA. Esta escolha permite também implementar simultaneamente os vários tipos de detecção apresentados no capítulo 2.

#### 3.3 Módulo FPGA

Na escolha da FPGA optou-se por adquirir um módulo de modo a poupar esforços de desenvolvimento do hardware de suporte ao *chip* da FPGA. Os módulos industriais da *Trenz Electro-nic* com FPGAs de baixa-gama (*Spartan 3* e *Spartan 6*) [Ele13c] [Ele13d] revelaram-se bastante interessantes quer pelo tamanho compacto da placa, preço reduzido e quantidade de funcionalida-

|                                    | FPGA                                                                                                                                                                                                                                                                             | DSP                                                                                                                                                                                                                                                                    |  |  |  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Aplicação<br>em sistemas<br>de SDR | <ul> <li>✓ IP cores facilitam a implementação de multiplicadores, divisores, FFT e operações trigonométricas (CORDIC).</li> <li>✓ NCO de fácil síntese através de blocos de propriedade intelectual parametrizáveis. Implementação eficaz de filtros CIC tirando par-</li> </ul> | <ul> <li>✗ Implementação de NCO e filtros CIC pouco eficientes a frequências relativamente elevadas, reduzindo significativamente o tempo disponível para o processamento a jusante.</li> <li>✓ Maior facilidade na implementação de operações matemáticas,</li> </ul> |  |  |  |

|                                    | tido da paralelização de operações.  X Maior esforço de desenvolvimento na implementação de                                                                                                                                                                                      | especialmente em vírgula flutu-<br>ante.                                                                                                                                                                                                                               |  |  |  |

|                                    | operações matemáticas, cálculos em vírgula flutuante dispendiosos em termos de recursos.                                                                                                                                                                                         | ✓ Implementação dos algoritmos em linguagens de alto nível (C) facilitam e permitem reduzir o tempo de desenvolvimento.                                                                                                                                                |  |  |  |

|                                    | ✓ Reconfiguração da FPGA permite a readaptação dos recursos às necessidades do sistema.                                                                                                                                                                                          | X Arquitetura fixa das DSPs<br>torna mais criteriosa a escolha da<br>mesma para a aplicação em causa.                                                                                                                                                                  |  |  |  |

| Flexibilidade                      | X Sistemas com um número<br>elevado de operações condicionais<br>são mais díficeis de implementar.<br>Alocação de recursos para cada<br>configuração.                                                                                                                            | ✓ Mudança de contexto facilitada pelo salto do processador para diferentes zonas do programa, re-utilização em run-time dos recursos de processamento.                                                                                                                 |  |  |  |

| Desempenho                         | • Melhor desempenho para sistemas que podem tirar partido da paralelização de operações.                                                                                                                                                                                         | • A arquitectura centralizada torna-a mais eficiente em aplicações que não tirem partido de paralelização.                                                                                                                                                             |  |  |  |

|                                    | <ul> <li>Frequências de relógio me-<br/>nores devido aos elementos de<br/>switching da FPGA que aumen-<br/>tam os tempos de propagação<br/>das linhas, compensado pela<br/>paralelização de operações.</li> </ul>                                                                | • Frequências de relógio mais elevadas mas o tempo do processador é dividido em execução de instruções, acesso à memória e execução de rotinas de interrupção I/O.                                                                                                     |  |  |  |

Tabela 3.1: Vantagens e desvantagens entre FPGA e DSP.

| Módulo       | FPGA       | Família        | Eq.Cells | BRAM   | DSP | #IOs | Preço |

|--------------|------------|----------------|----------|--------|-----|------|-------|

| TE0320-EV02  | XC3SD1800A | Spartan-3A DSP | 37 K     | 1.5 Kb | 84  | 109  | 177€  |

| TE0320-EV02B | XC3SD3400A | Spartan-3A DSP | 53 K     | 2.2 Kb | 109 | 469  | 201€  |

| TE0630-00    | XC6SLX45   | Spartan-6 LX   | 43 K     | 2  Kb  | 58  | 110  | 190€  |

| TE0630-00IBF | XC6SLX75   | Spartan-6 LX   | 74 K     | 3 Kb   | 132 | 110  | 272€  |

| TE0630-00IV  | XC6SLX150  | Spartan-6 LX   | 147 K    | 4.8 Kb | 180 | 110  | 332€  |

Tabela 3.2: Comparativo dos módulos FPGA da Trenz Electronic.

des/periféricos incluídos. A tabela 3.2 reflete as opções mais apropriadas para o projeto em causa. Todos estes módulos apresentam um controlador USB e respectivo conector em forma "mini" facilitando as comunicações com o computador hospedeiro com taxas de transferência elevadas.